# **PDP-15** VT15 GRAPHIC PROCESSOR MAINTENANCE MANUAL

DIGITAL EQUIPMENT CORPORATION • MAYNARD, MASSACHUSETTS

EK-0VT15-MN-002

# **PDP-15** VT15 GRAPHIC PROCESSOR MAINTENANCE MANUAL

DIGITAL EQUIPMENT CORPORATION • MAYNARD, MASSACHUSETTS

1st Edition December 1970 2nd Printing (Rev) August 1971 3rd Printing (Rev) January 1974

# Copyright © 1970, 1971, 1974 by Digital Equipment Corporation

The material in this manual is for information purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC       | PDP          |

|-----------|--------------|

| FLIP CHIP | FOCAL        |

| DIGITAL   | COMPUTER LAB |

# CONTENTS

# CHAPTER 1 VT15 BASIC DESCRIPTION

| 1.1 | Purpose and Scope                           | 1-1 |

|-----|---------------------------------------------|-----|

| 1.2 | Functional Description                      | 1-1 |

| 1.3 | Physical Description                        | 1-5 |

| 1.4 | System Options                              | 1-6 |

| 1.5 | System Specifications                       | 1-6 |

| 1.6 | Referencing Conventions                     | 1-6 |

| 1.7 | Terminology                                 | 1-7 |

| 1.8 | Engineering Drawings and Circuit Schematics | 1-8 |

# CHAPTER 2 INSTALLATION

| 2.1   | Unpacking                                            | 2-1 |

|-------|------------------------------------------------------|-----|

| 2.2   | Primary ac Power Cables                              | 2-2 |

| 2.3   | Initial Setup                                        | 2-4 |

| 2.3.1 | VT15 Power Connections                               | 2-4 |

| 2.3.2 | Cable Installation                                   | 2-4 |

| 2.3.3 | System Power-Up                                      | 2-5 |

| 2.4   | Customer Acceptance                                  | 2-6 |

| 2.4.1 | Checklist                                            | 2-6 |

| 2.4.2 | Diagnostic Programs                                  | 2-7 |

| 2.5   | System Checks and Adjustments                        | 2-7 |

| 2.6   | VM15 Display Multiplex Option Installation Procedure | 2-9 |

# CHAPTER 3 SYSTEM OPERATION

| 3.1     | System Organization             | 3-1 |

|---------|---------------------------------|-----|

| 3.1.1   | I/O Control                     | 3-4 |

| 3.1.1.1 | DCH Control and API Multiplexer | 3-4 |

| 3.1.1.2 | Read Cycle                      | 3-4 |

| 3.1.1.3 | Write Cycle                     | 3-4 |

| 3.1.2   | Data Collectors                 | 3-4 |

| 3.1.2.1 | Bus Receivers                   | 3-4 |

| 3.1.2.2 | Bus Drivers                     | 3-4 |

|         |                                           | Page |

|---------|-------------------------------------------|------|

| 3.1.2.3 | Input Buffer Register                     | 3-5  |

| 3.1.2.4 | Data Buffer Register                      | 3-5  |

| 3.1.3   | Timing and Control                        | 3-5  |

| 3.1.3.1 | Main Timing                               | 3-5  |

| 3.1.3.2 | Control and Graphic Timing                | 3-6  |

| 3.1.4   | Instruction Register and Logic            | 3-6  |

| 3.1.4.1 | Parameter and Skip Registers              | 3-6  |

| 3.1.4.2 | Direction and Rotate Logic                | 3-10 |

| 3.1.4.3 | Increment Register                        | 3-10 |

| 3.1.4.4 | Intensity                                 | 3-10 |

| 3.1.4.5 | Status                                    | 3-11 |

| 3.1.4.6 | Adder Gating                              | 3-11 |

| 3.1.5   | Main Registers                            | 3-11 |

| 3.1.5.1 | PC, X- and Y-Registers                    | 3-11 |

| 3.1.5.2 | Magnitude of Change ( $\Delta$ ) Register | 3-11 |

| 3.1.6   | Digital-to-Analog Converters              | 3-12 |

| 3.1.7   | Analog Function Group                     | 3-12 |

| 3.1.8   | Arbitrary Vector Timing and Control       | 3-17 |

| 3.1.9   | Character Generator                       | 3-17 |

| 3.1.9.1 | Control Logic                             | 3-17 |

| 3.1.9.2 | Input Mixer and Read–Only Memory          | 3-17 |

| 3.1.10  | Display Console Multiplexer Option        | 3-17 |

| CHAPTER | 4 INSTRUCTION FLOW ANALYSES               |      |

| 4.1     | Input/Output Transfer Commands            | 4-2  |

| 4.2     | IOT Operate Commands                      | 4-3  |

| 4.2.1   | Set Initial Conditions                    | 4-3  |

| 4.2.1.1 | Program Interrupt Enables                 | 4-3  |

| 4.2.1.2 | Clear Flags                               | 4-3  |

| 4.2.1.3 | Paper Area Change Enable                  | 4-3  |

| 4.2.1.4 | Paper Area                                | 4-3  |

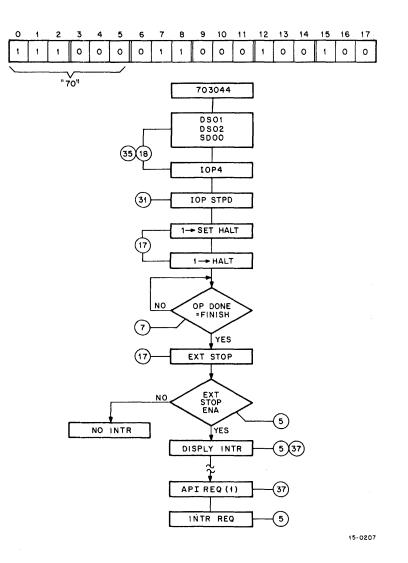

4.2.2Load and Start Display4-74.2.3External Stop Display4-7

.

|         |                                     | Page |

|---------|-------------------------------------|------|

| 4.2.4   | Resume Display After Flag           | 4-8  |

| 4.2.5   | Clear Flags                         | 4-8  |

| 4.3     | IOT Skip Commands                   | 4-10 |

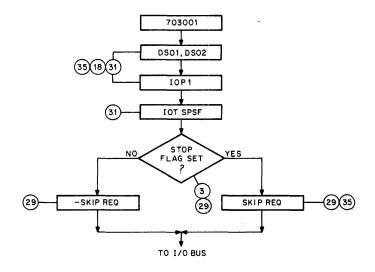

| 4.3.1   | Skip On Stop Flag                   | 4-10 |

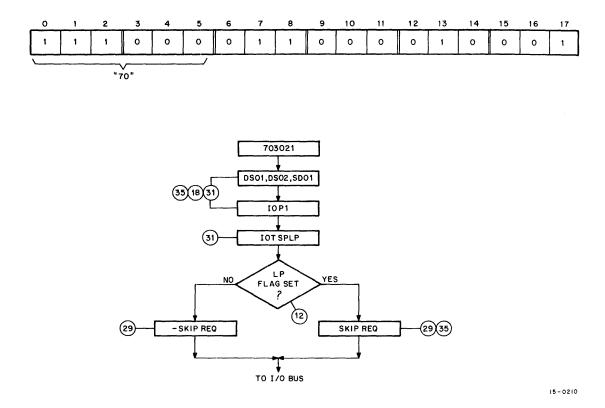

| 4.3.2   | Skip On Light Pen Flag              | 4-10 |

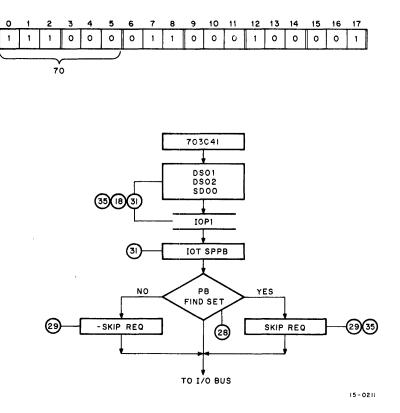

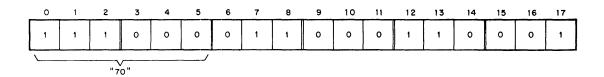

| 4.3.3   | Skip On Pushbutton Flag             | 4-10 |

| 4.3.4   | Skip On Edge Flag                   | 4-10 |

| 4.3.5   | Skip On Any Flag                    | 4-14 |

| 4.3.6   | Skip On Any Interrupt Flag          | 4-14 |

| 4.3.7   | Skip On External Stop               | 4-16 |

| 4.4     | IOT Read Commands                   | 4-16 |

| 4.4.1   | Read Status 1                       | 4-17 |

| 4.4.2   | Read Status 2                       | 4-19 |

| 4.4.3   | Read Status 3                       | 4-20 |

| 4.4.4   | Read Program Counter (RPC) Register | 4-20 |

| 4.4.5   | Read X-Position Register            | 4-21 |

| 4.4.6   | Read Y-Position Register            | 4-21 |

| 4.5     | VT15 Graphic Processor Instructions | 4-24 |

| 4.5.1   | Parameter/Skip Instructions         | 4-25 |

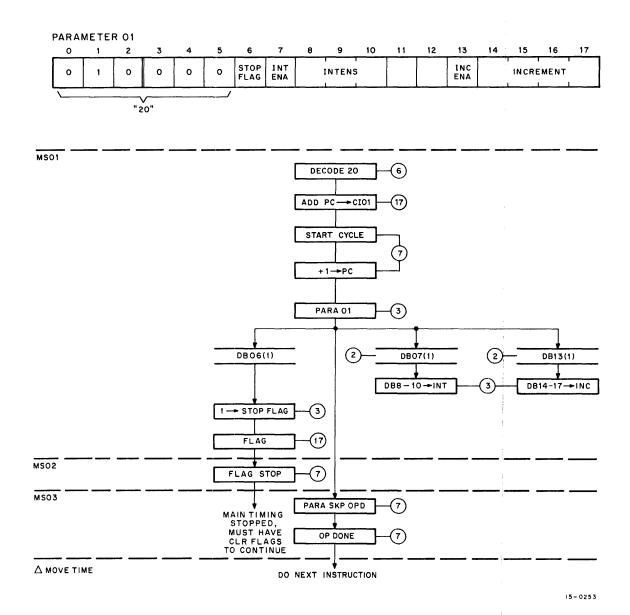

| 4.5.1.1 | Parameter 1                         | 4-25 |

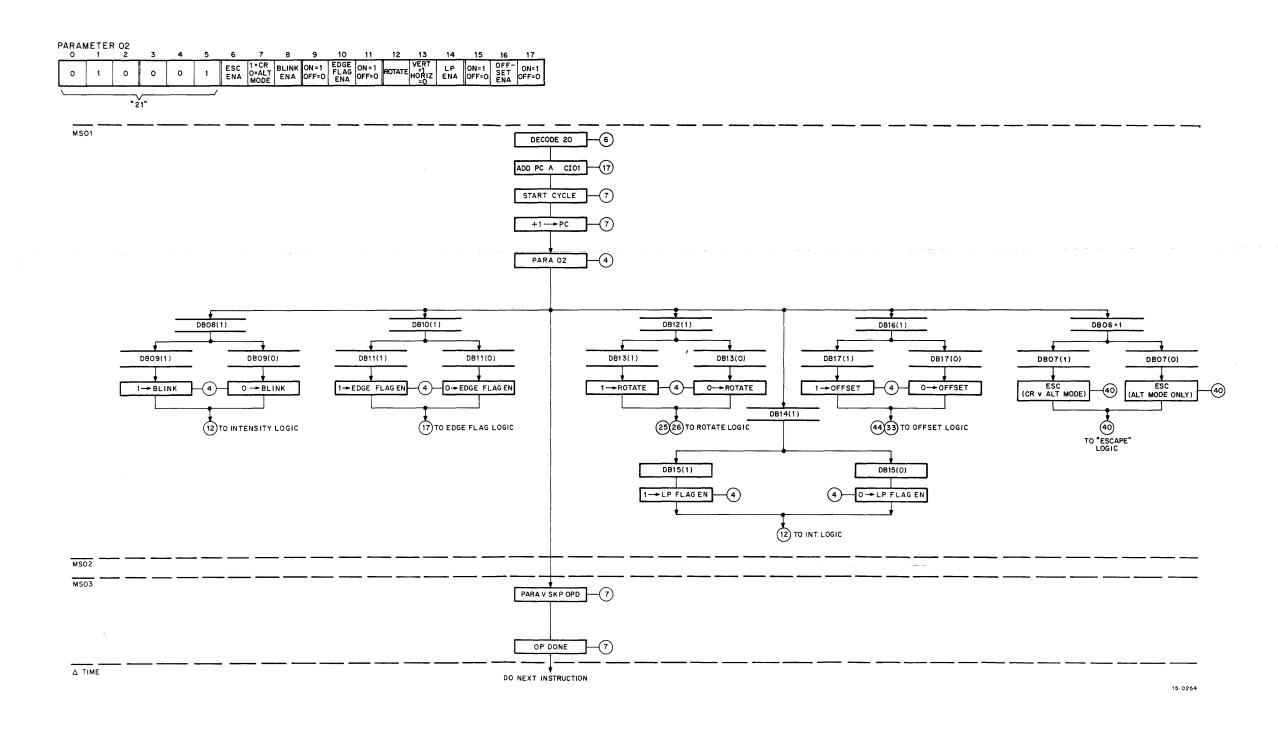

| 4.5.1.2 | Parameter 2                         | 4-28 |

| 4.5.1.3 | Parameter 3                         | 4-31 |

| 4.5.1.4 | Skip 1                              | 4-35 |

| 4.5.1.5 | Skip 2                              | 4-35 |

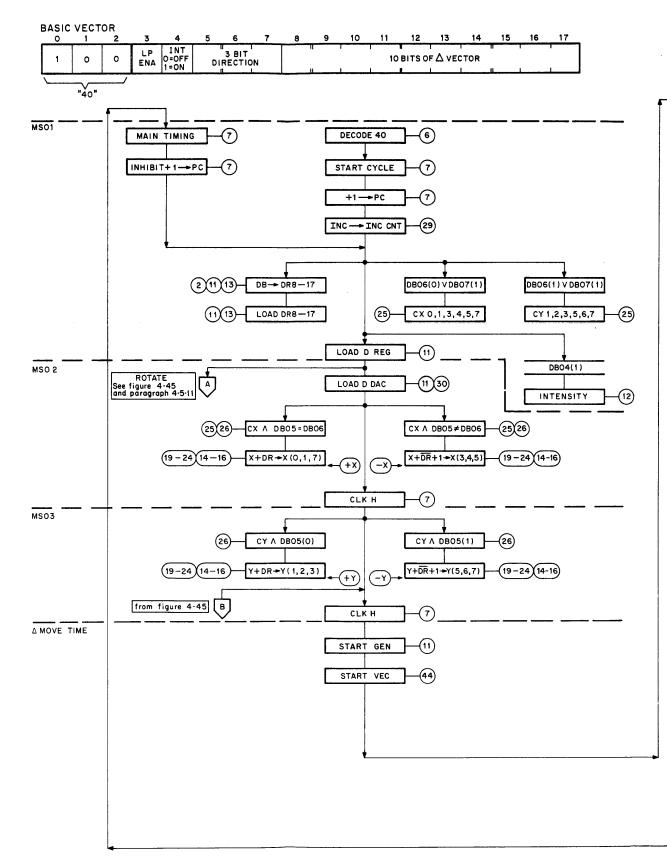

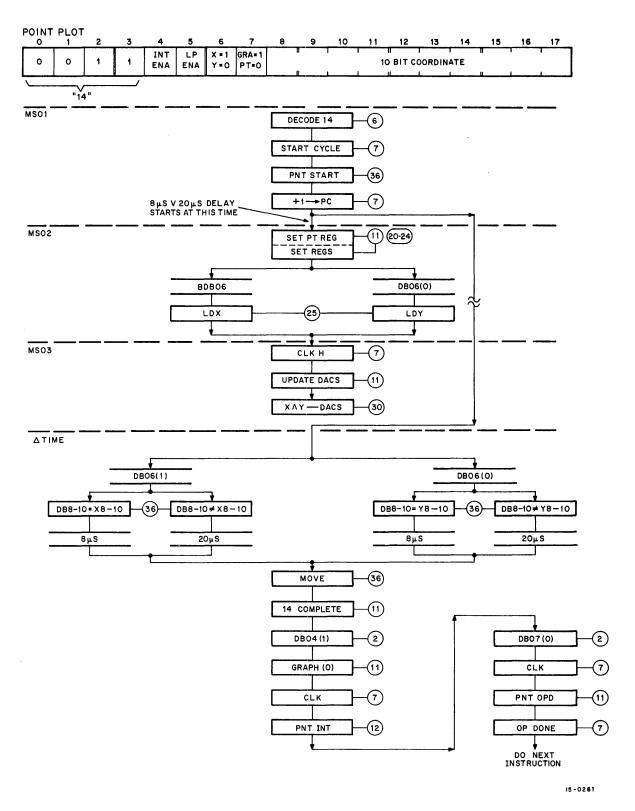

| 4.5.2   | Basic Vector                        | 4-37 |

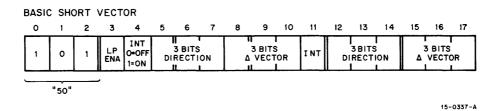

| 4.5.3   | Basic Short Vector                  | 4-39 |

| 4.5.4   | Point/Graph Plot                    | 4-44 |

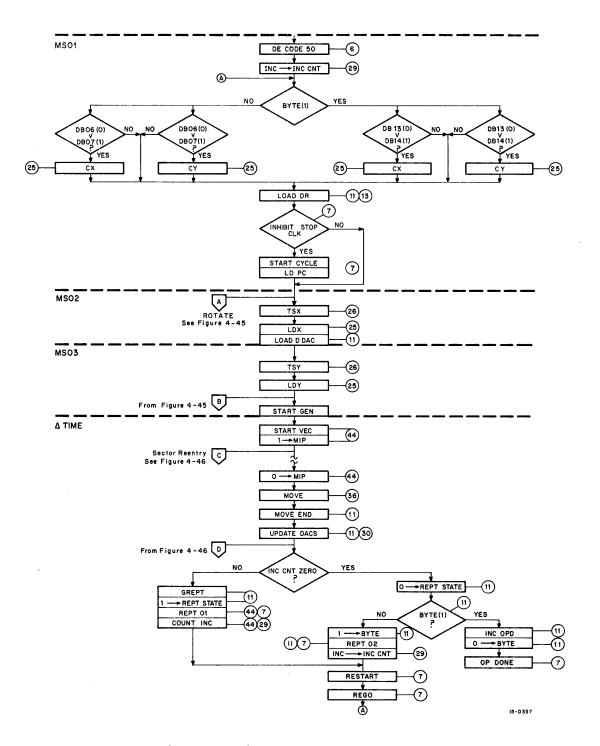

| 4.5.4.1 | Point Plot                          | 4-44 |

| 4.5.4.2 | Graph Plot                          | 4-46 |

| 4.5.5   | Jump/Jump-to-Subroutine             | 4-46 |

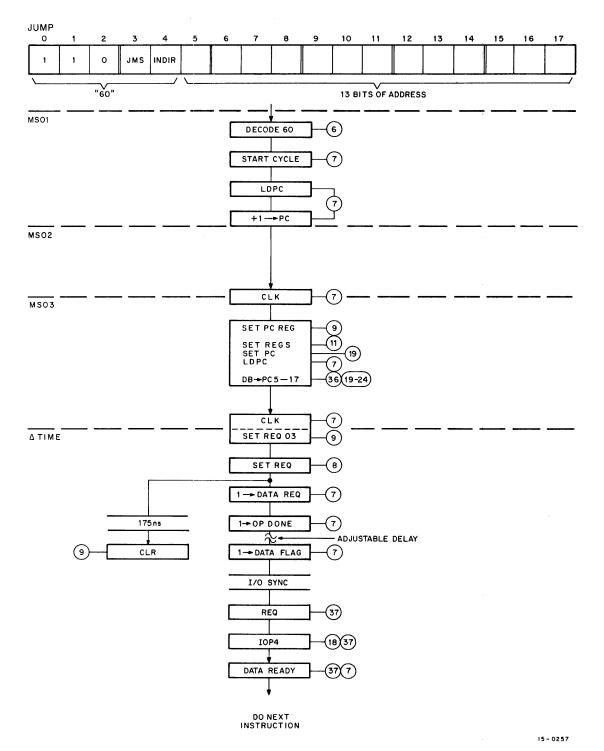

| 4.5.5.1 | Jump                                | 4-49 |

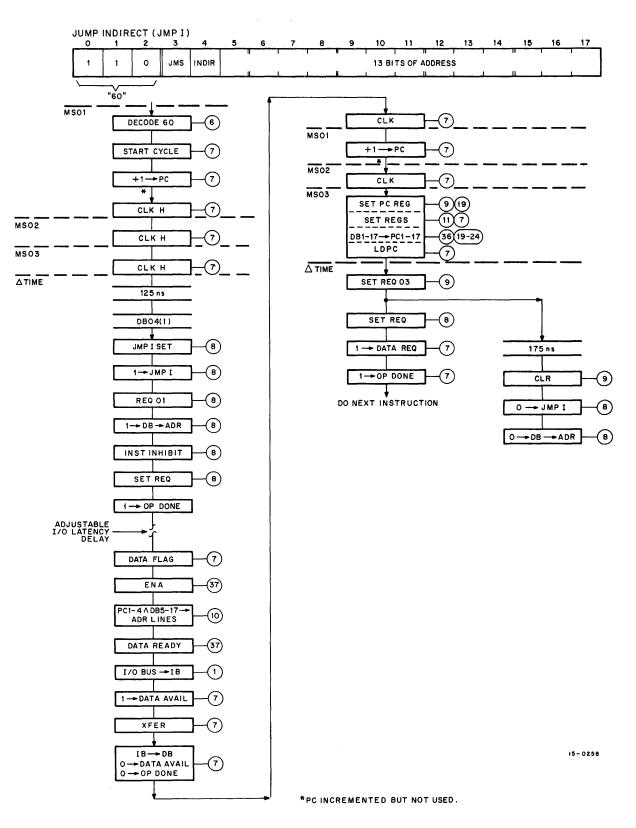

| 4.5.5.2 | Jump Indirect                       | 4-49 |

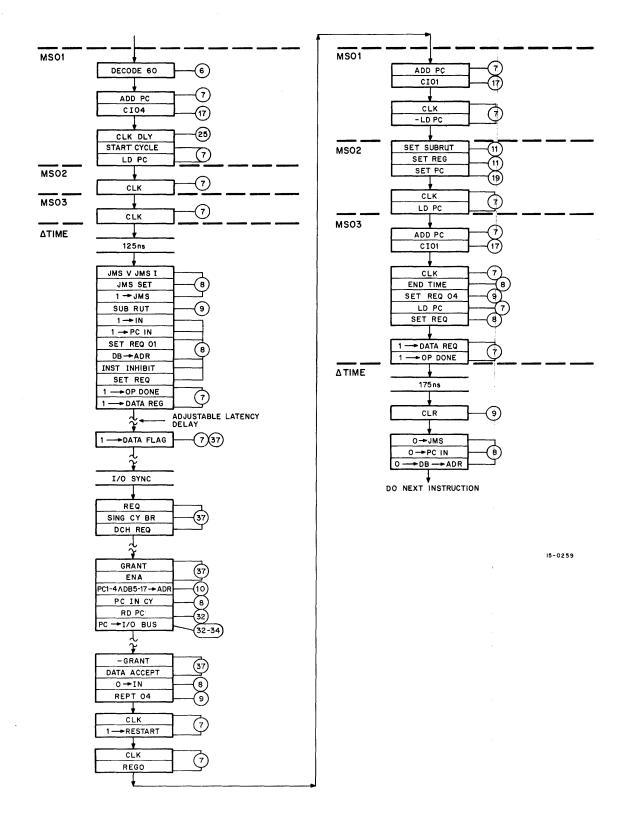

| 4.5.5.3 | Jump-to-Subroutine                  | 4-49 |

| 4.5.5.4 | Jump-to-Subroutine Indirect         | 4-49 |

| 4.5.6   | Save/Restore Instruction                    | 4–54 |

|---------|---------------------------------------------|------|

| 4.5.7   | Character Input                             | 4-57 |

| 4.5.8   | Character String                            | 4–59 |

| 4.5.8.1 | IOPS ASCII                                  | 4-67 |

| 4.5.8.2 | Implied JMS                                 | 4-67 |

| 4.5.8.3 | Termination Functions and Tab               | 4-68 |

| 4.5.9   | Arbitrary Vector and Arbitrary Short Vector | 4-69 |

| 4.5.9.1 | Arbitrary Vector                            | 4-69 |

| 4.5.9.2 | Arbitrary Short Vector                      | 4-73 |

| 4.5.10  | Slave                                       | 4-75 |

| 4.5.11  | Rotate                                      | 4-76 |

| 4.5.12  | Sector Re-entry                             | 4-76 |

## CHAPTER 5 SPECIAL MODULES

| 5.1    | General                                  | 5-1  |

|--------|------------------------------------------|------|

| 5.1.1  | M Series Measurement Definitions         | 5-1  |

| 5.1.2  | Loading                                  | 5-2  |

| 5.1.3  | Parts Location                           | 5-2  |

| 5.1.4  | Digital–to–Analog Converter A618YA       | 5-3  |

| 5.1.5  | Digital–to–Analog Converter A622         | 5-3  |

| 5.1.6  | Read–Only Memory Matrix and Decode G618  | 5-3  |

| 5.1.7  | ROM Diode Matrix Receiver M762           | 5-9  |

| 5.1.8  | Thirty–Two to Eight Bit Multiplexer M761 | 5-9  |

| 5.1.9  | Vector Generator A3180                   | 5-10 |

| 5.1.10 | VV15 Timing and Control M7010            | 5-12 |

| 5.1.11 | Arbitrary Vector Generator A3170         | 5-13 |

| 5.1.12 | Dual Analog Switch A140                  | 5-14 |

| 5.1.13 | Dual Analog Summer Driver A238           | 5-14 |

# CHAPTER 6 MAINTENANCE

| 6.1 | Equipment Required     | 6-1 |

|-----|------------------------|-----|

| 6.2 | Diagnostic Programming | 6-1 |

| 6.3 | Preventive Maintenance | 6-3 |

|         |                                               | Page |

|---------|-----------------------------------------------|------|

| 6.3.1   | Mechanical Checks                             | 6-3  |

| 6.3.2   | Electrical Checks                             | 6-3  |

| 6.4     | System Logic Checks and Adjustments           | 6-4  |

| 6.4.1   | H721 Logic Power Supply Adjustment            | 6-4  |

| 6.4.2   | M401 System Basic Clock Adjustment            | 6-5  |

| 6.4.3   | Data Flag Delay                               | 6-5  |

| 6.4.4   | Display Console Bus Delay                     | 6-6  |

| 6.4.5   | Move Settle Delay                             | 6-6  |

| 6.4.6   | Blink Delay                                   | 6-7  |

| 6.4.7   | Long Point Settle Delay                       | 6-7  |

| 6.4.8   | Short Point Settle Delay                      | 6-7  |

| 6.5     | Analog Adjustments                            | 6-8  |

| 6.5.1   | Analog Voltage Adjustments                    | 6-8  |

| 6.5.1.1 | H707 Precision Analog Power Supply Adjustment | 6-8  |

| 6.5.1.2 | D DAC Reference Voltage Adjustment            | 6-9  |

| 6.5.2   | Analog Adjustments                            | 6-9  |

| 6.6     | Corrective Maintenance                        | 6-9  |

| 6.6.1   | Module Handling                               | 6-10 |

| 6.6.2   | System Troubleshooting                        | 6-11 |

| 6.6.3   | Functional Group Troubleshooting              | 6-11 |

| 6.6.4   | Module Troubleshooting                        | 6-11 |

| 6.6.5   | VT15 Graphic Processor Engineering Drawings   | 6-11 |

# APPENDIX A ASCII CHARACTER GENERATION AND DECODING A-1

#### ILLUSTRATIONS

| Figure No. | Title                                          | Page |

|------------|------------------------------------------------|------|

| 1-1        | VT15 Graphic Processor                         | 1-2  |

| 1-2        | Graphic–15 Display System Interconnect Diagram | 1-3  |

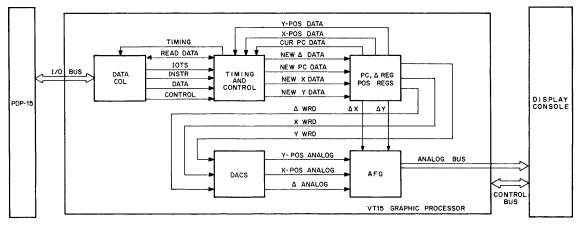

| 1-3        | VT15 Functional Block Diagram                  | 1-4  |

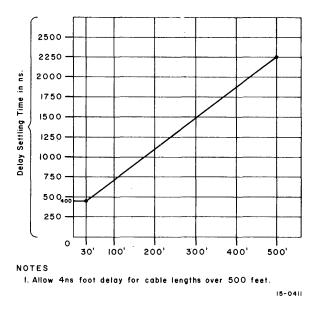

| 2-1        | Delay Setting vs Cable Lengths                 | 2-5  |

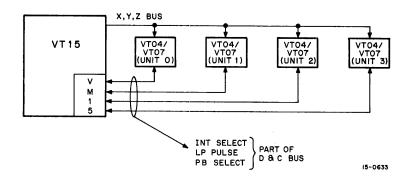

| 2-2        | VM15 Interconnect Diagram                      | 2-9  |

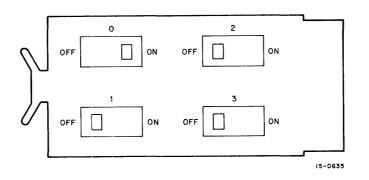

| 2-3        | W719 Unit Select Module                        | 2-10 |

# ILLUSTRATIONS (Cont)

| Figure No. | Title                                                                | Page |

|------------|----------------------------------------------------------------------|------|

| 3-1        | Major Functional Groups, Interconnect Diagram                        | 3-1  |

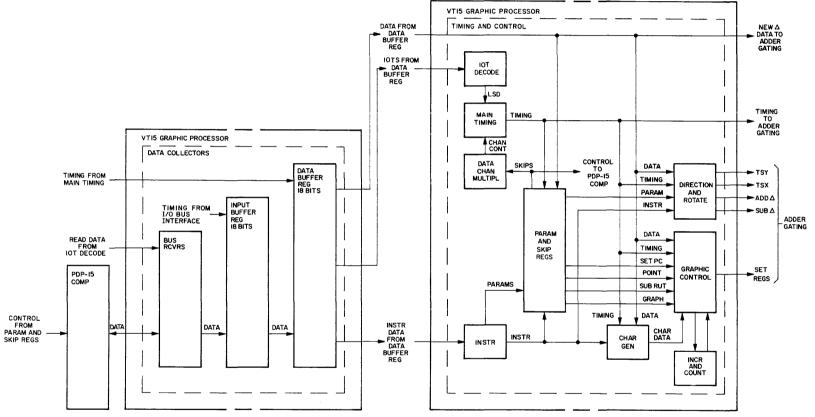

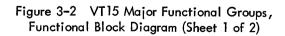

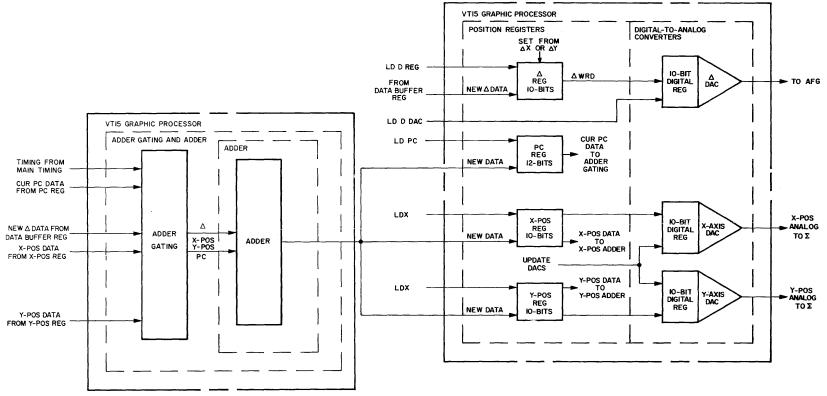

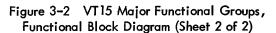

| 3-2        | VT15 Major Functional Groups, Functional Block<br>Diagram (2 Sheets) | 3-2  |

| 3-3        | VT15 Main Timing Flow Diagram                                        | 3-7  |

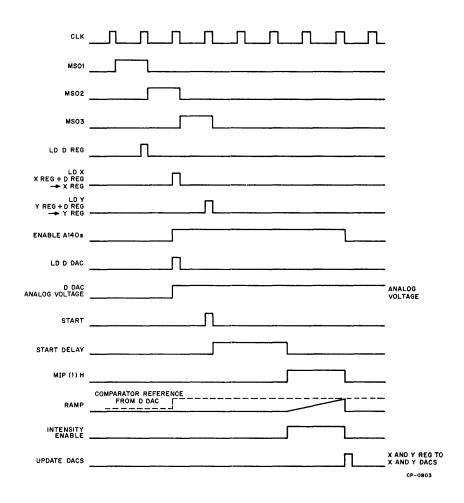

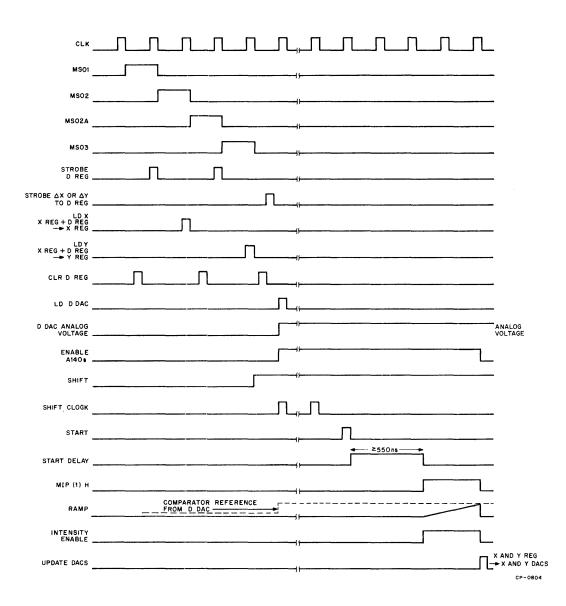

| 3-4        | VT15 Main Timing Diagram (2 Sheets)                                  | 3-9  |

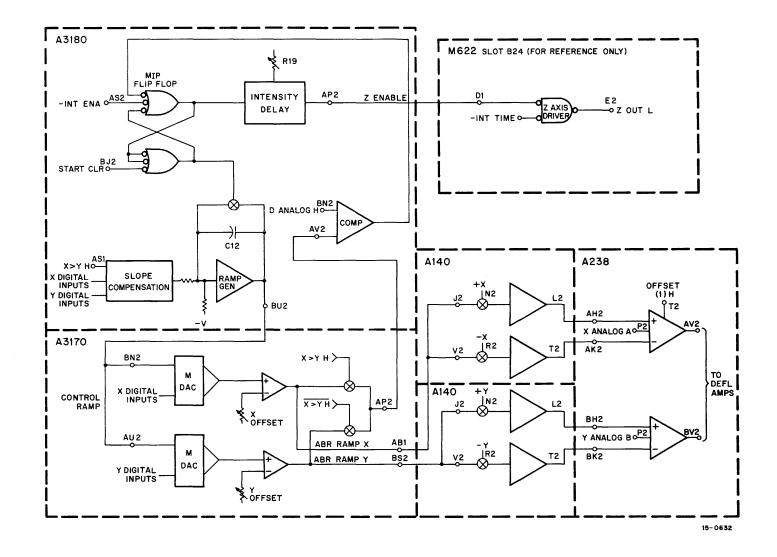

| 3-5        | Analog Function Group                                                | 3-14 |

| 3-6        | Analog Function Timing Diagram (Basic Vector)                        | 3-15 |

| 3-7        | Analog Function Timing Diagram (Arbitrary Vector)                    | 3-16 |

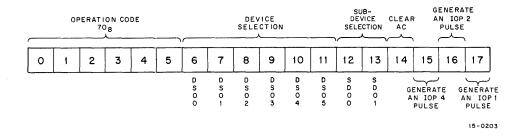

| 4-1        | Basic IOT Command Format                                             | 4-2  |

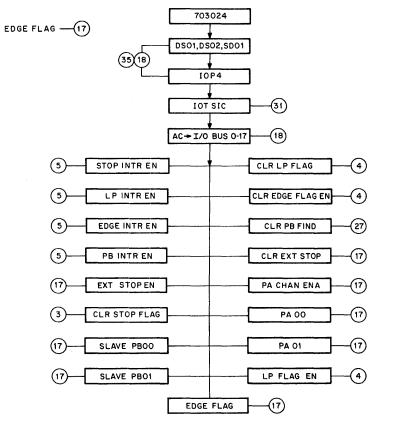

| 4-2        | Set Initial Conditions (SIC) Flow Diagram                            | 4-4  |

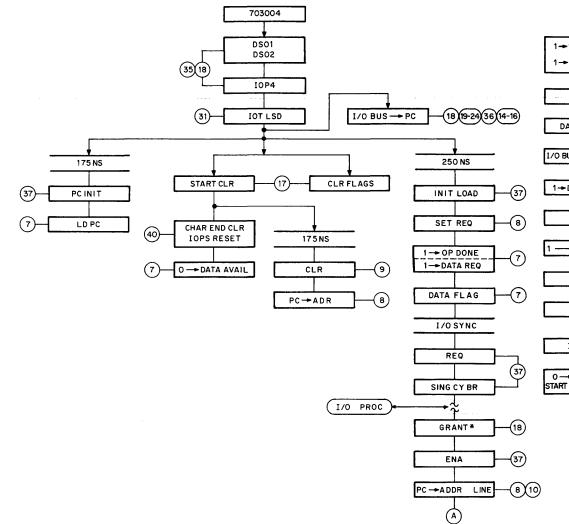

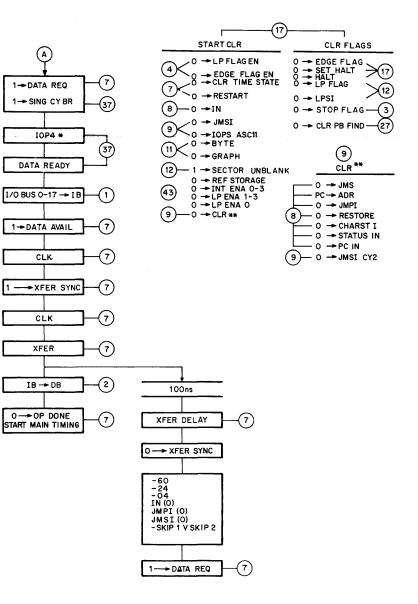

| 4-3        | Load and Start Display (LSD) Flow Diagram                            | 4-5  |

| 4-4        | External Stop Display (STPD) Flow Diagram                            | 4-8  |

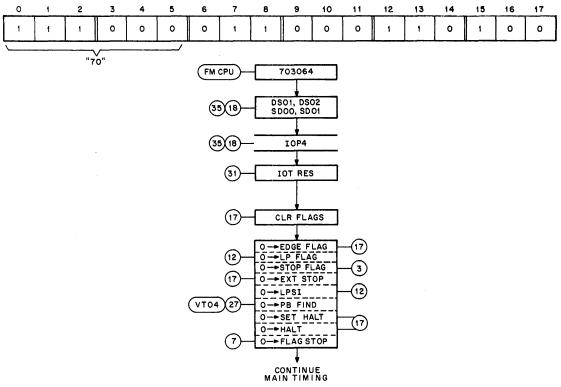

| 4-5        | Resume Display After Flag (RES) Flow Diagram                         | 4-9  |

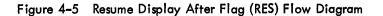

| 4-6        | Clear Flags (CAF) Flow Diagram                                       | 4-9  |

| 4-7        | Skip On Stop Flag (SPSF) Flow Diagram                                | 4-11 |

| 4-8        | Skip On Light Pen Flag (SPLP) Flow Diagram                           | 4-12 |

| 4-9        | Skip On Pushbutton Flag (SPPB) Flow Diagram                          | 4-13 |

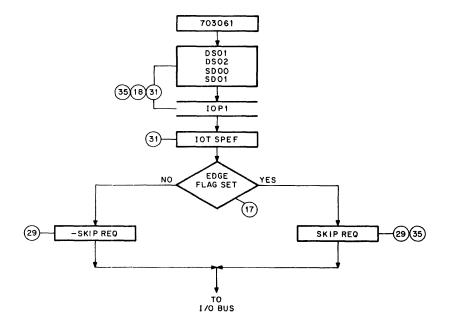

| 4-10       | Skip On Edge Flag (SPEF) Flow Diagram                                | 4-14 |

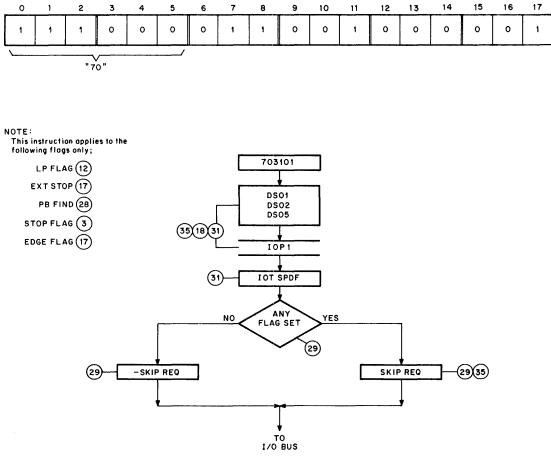

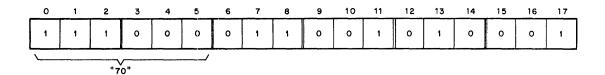

| 4-11       | Skip On Any Flag (SPDF) Flow Diagram                                 | 4-15 |

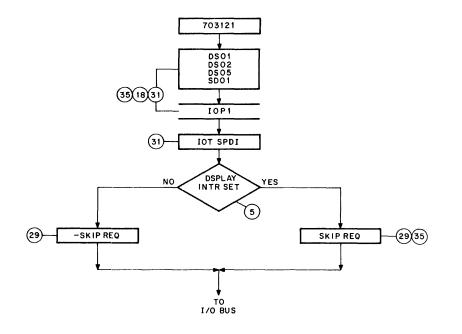

| 4-12       | Skip On Any Interrupt Flag (SPDI) Flow Diagram                       | 4-16 |

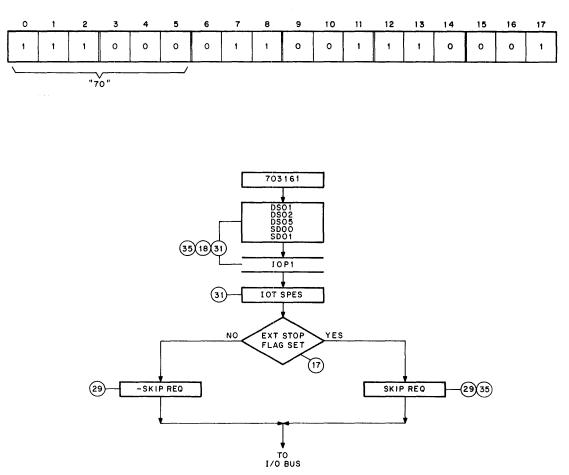

| 4-13       | Skip On External Stop (SPES) Flow Diagram                            | 4-17 |

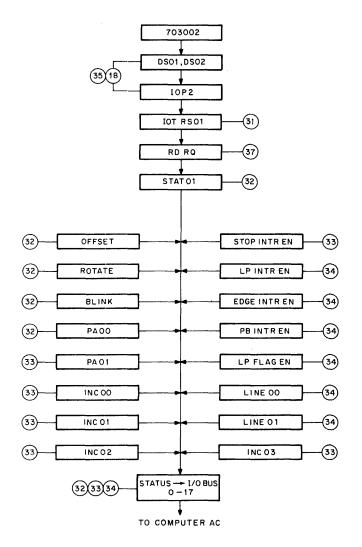

| 4-14       | Read Status 1 (RS1) Flow Diagram                                     | 4-18 |

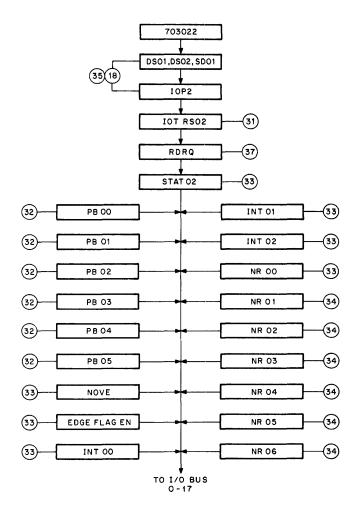

| 4-15       | Read Status 2 (RS2) Flow Diagram                                     | 4-19 |

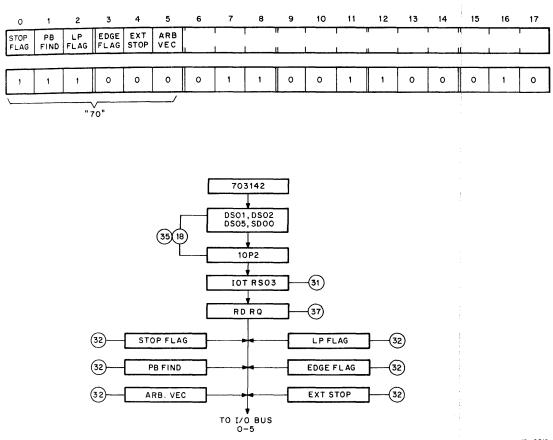

| 4-16       | Read Status 3 (RS3) Flow Diagram                                     | 4–20 |

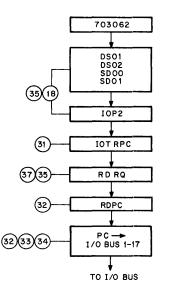

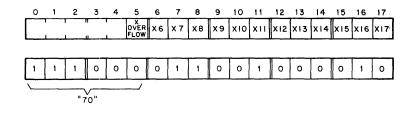

| 4-17       | Read Program Counter (RPC) Register Flow Diagram                     | 4-21 |

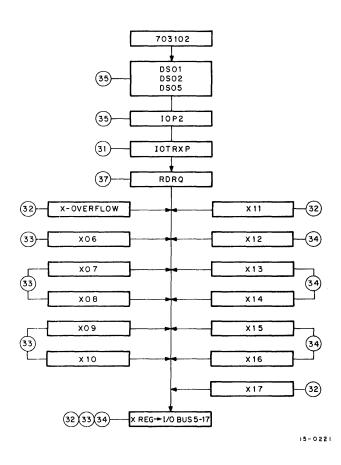

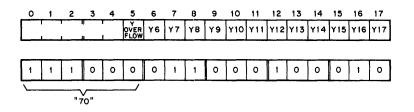

| 4-18       | Read X-Position Register (RXP) Flow Diagram                          | 4-22 |

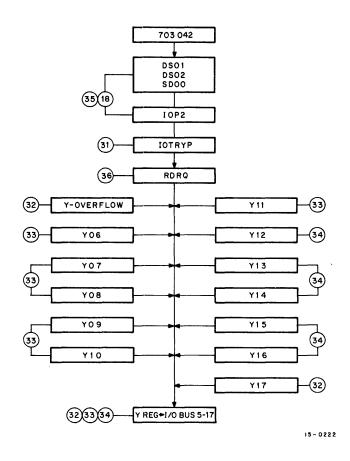

| 4-19       | Read Y-Position Register (RYP) Flow Diagram                          | 4-23 |

| 4-20       | Parameter 1 Instruction Flow Diagram                                 | 4-26 |

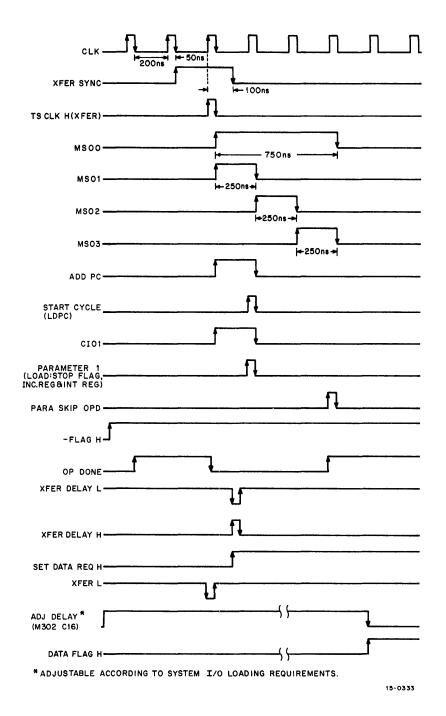

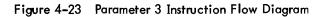

| 4-21       | Instruction Basic Timing Diagram                                     | 4-27 |

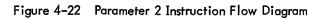

| 4-22       | Parameter 2 Instruction Flow Diagram                                 | 4-29 |

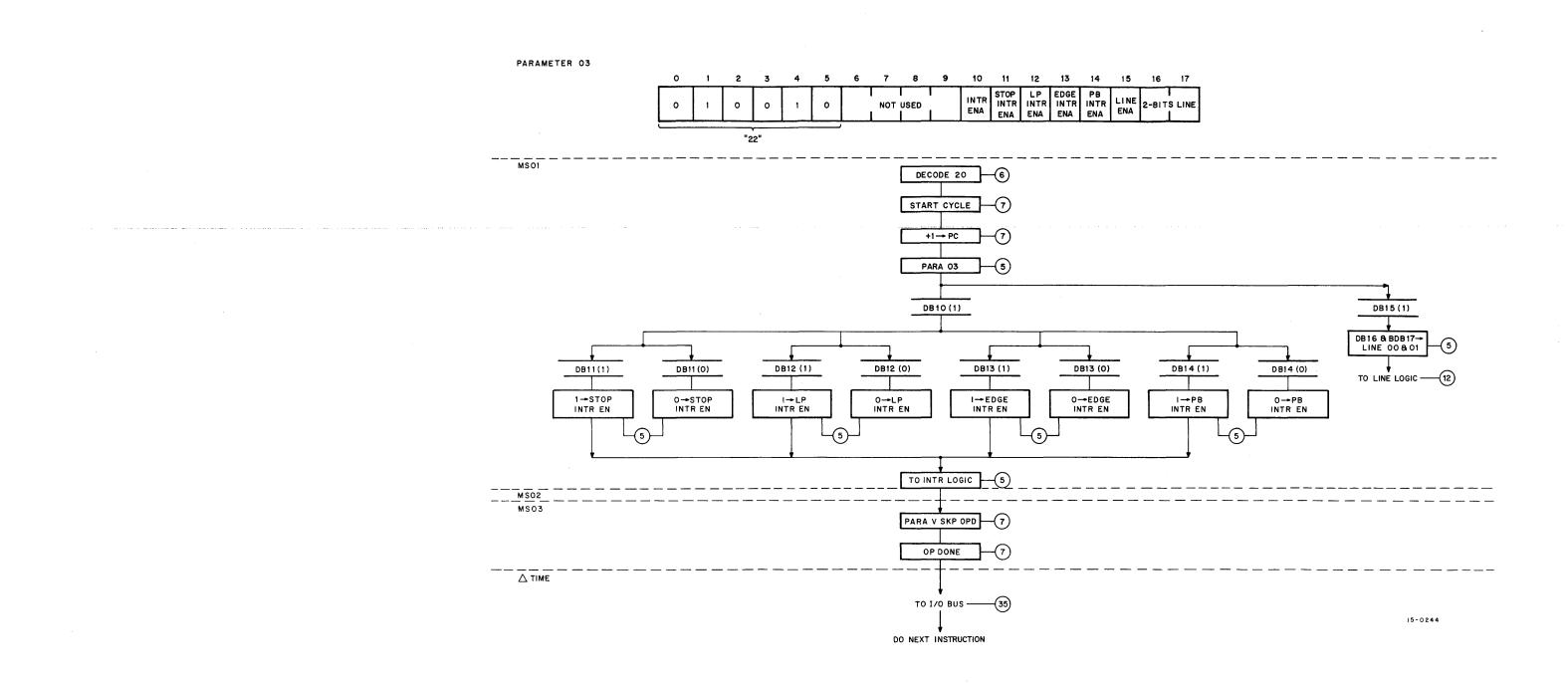

| 4-23       | Parameter 3 Instruction Flow Diagram                                 | 4-33 |

| 4-24       | Line Function Timing                                                 | 4-34 |

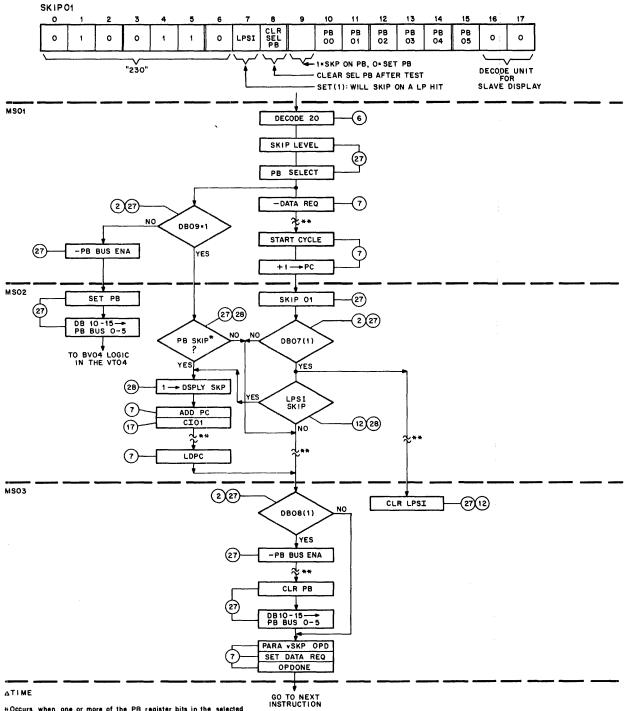

| 4–25       | Skip 1 Instruction Flow Diagram                                      | 4-36 |

| 4-26       | Skip 2 Instruction Flow Diagram                                      | 4-38 |

ILLUSTRATIONS (Cont)

| Figure No.    | Title                                                | Page        |

|---------------|------------------------------------------------------|-------------|

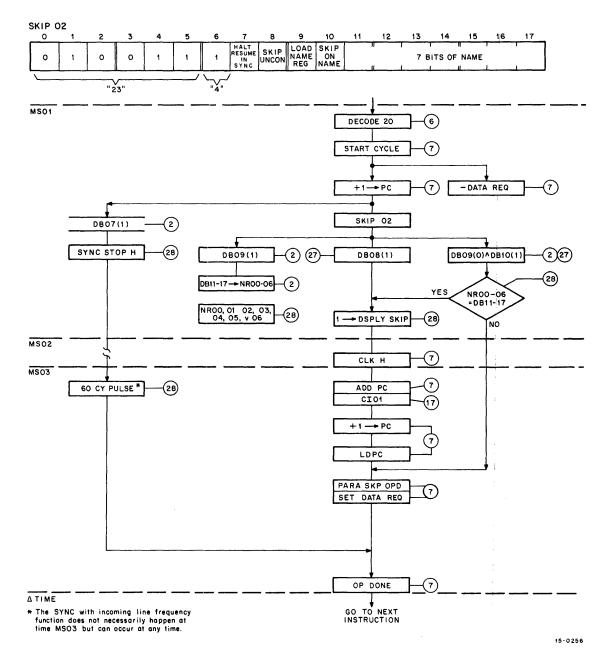

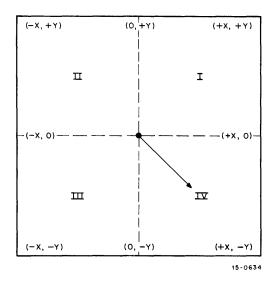

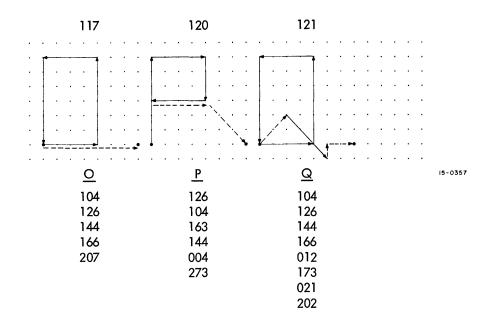

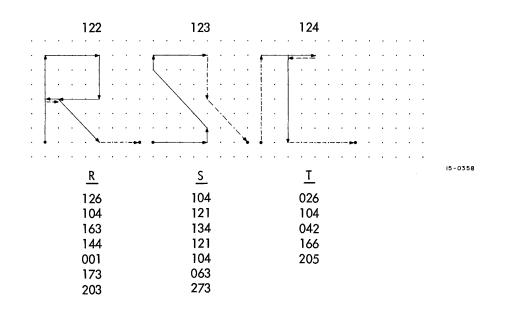

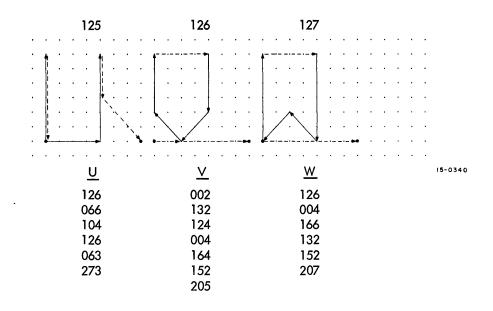

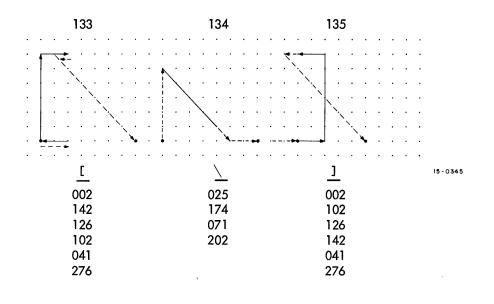

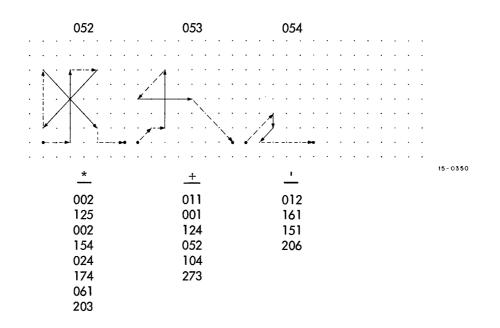

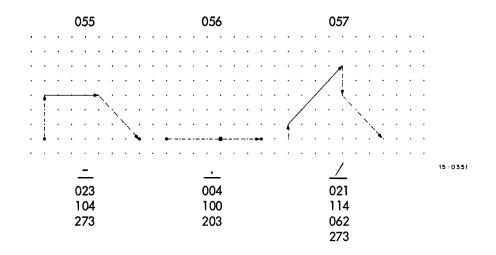

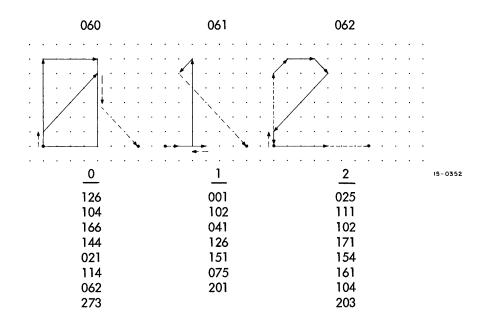

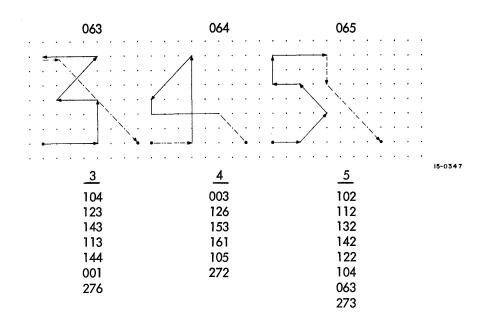

| 4-27          | Eight Basic Vector Directions                        | 4-39        |

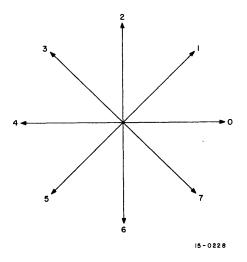

| 4-28          | Basic Vector Instruction Flow Diagram                | 4-41        |

| 4-29          | Basic Short Vector Instruction Format                | 4-42        |

| 4-30          | Basic Short Vector Instruction Flow Diagram          | 4-43        |

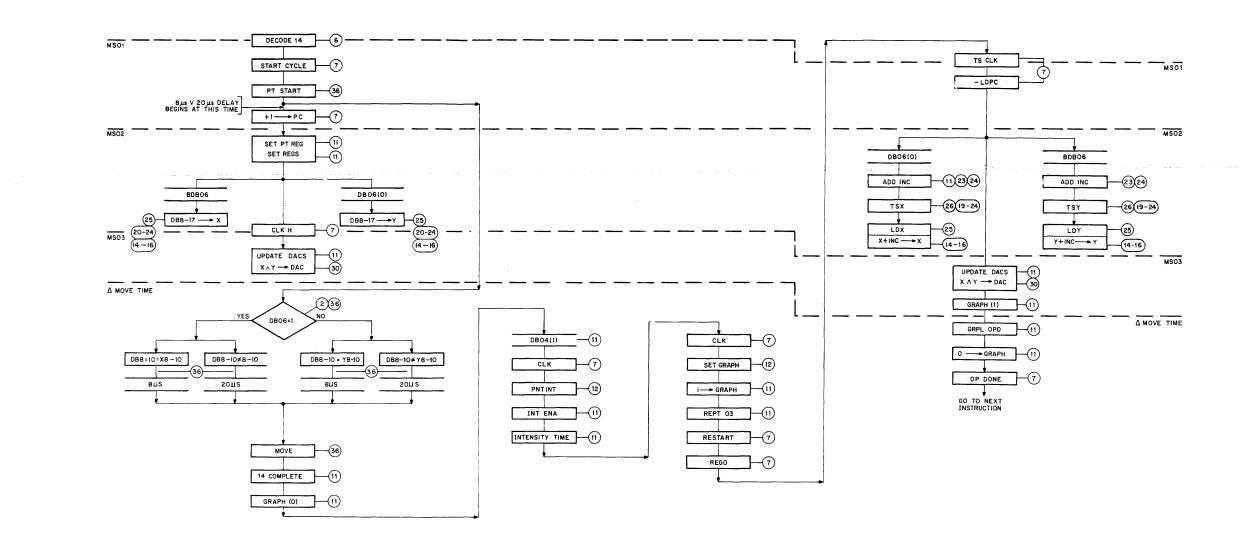

| 4-31          | Point Plot Instruction Flow Diagram                  | 4-45        |

| 4-32          | Graph Plot Instruction Flow Diagram                  | 4-47        |

| 4-33          | Jump Instruction Flow Diagram                        | 4–50        |

| 4-34          | Jump Indirect Instruction Flow Diagram               | 4-51        |

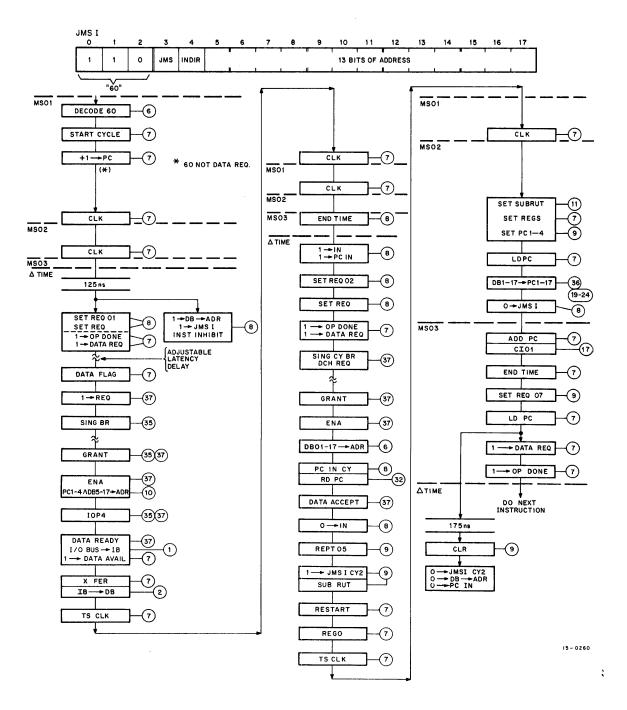

| 4-35          | DJMS Instruction Flow Diagram                        | 4-52        |

| 4-36          | JMS Indirect Instruction Flow Diagram                | 4-53        |

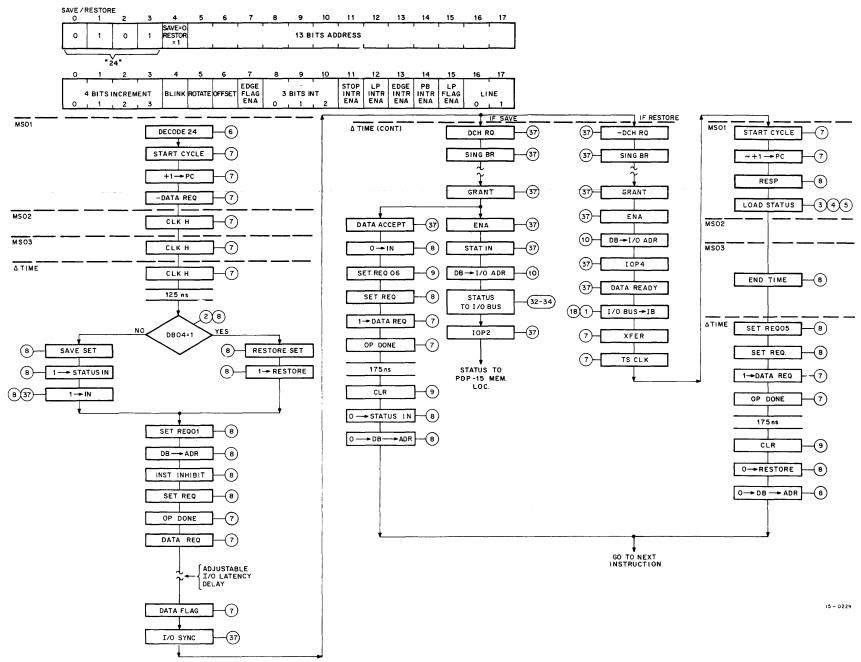

| 4-37          | Save/Restore Instruction Flow Diagram                | 4–55        |

| 4-38          | Character Input Instruction Flow Diagram             | 4-58        |

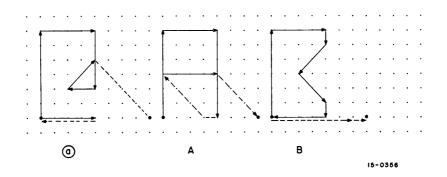

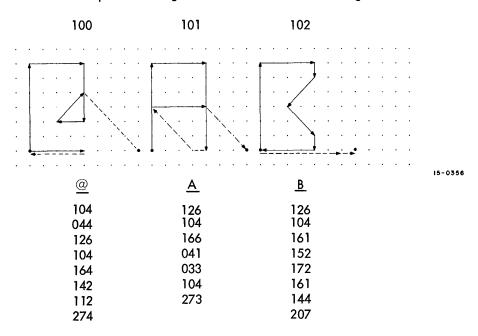

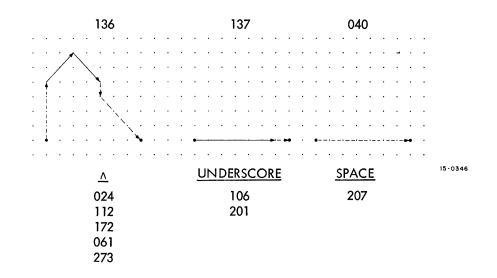

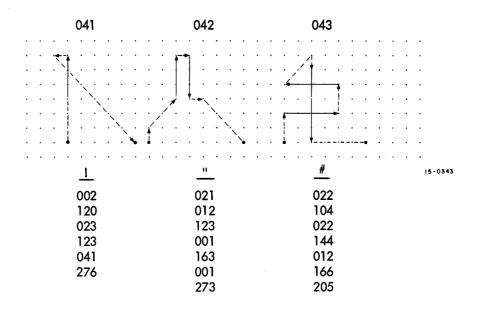

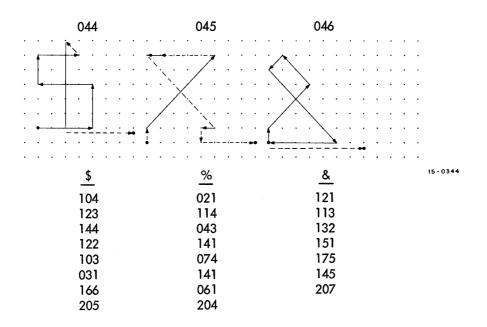

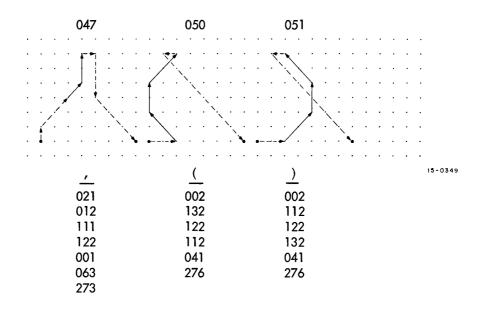

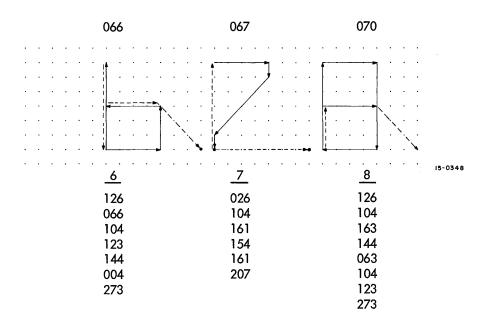

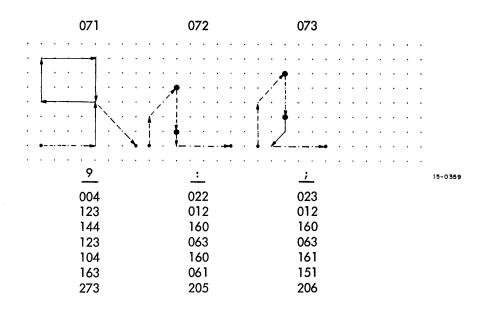

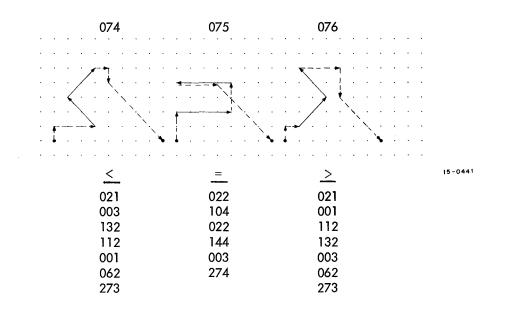

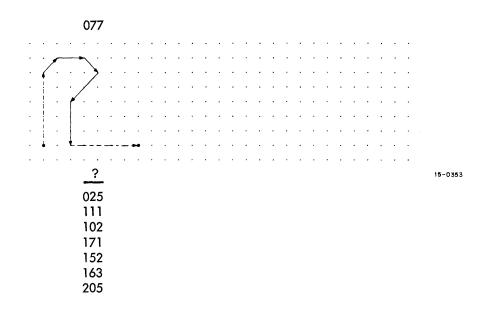

| 4-39          | ASCII Character Generation                           | 4–59        |

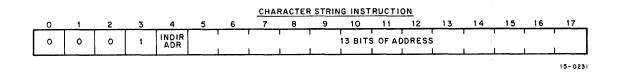

| 4-40          | Character String Instruction Format                  | 4-60        |

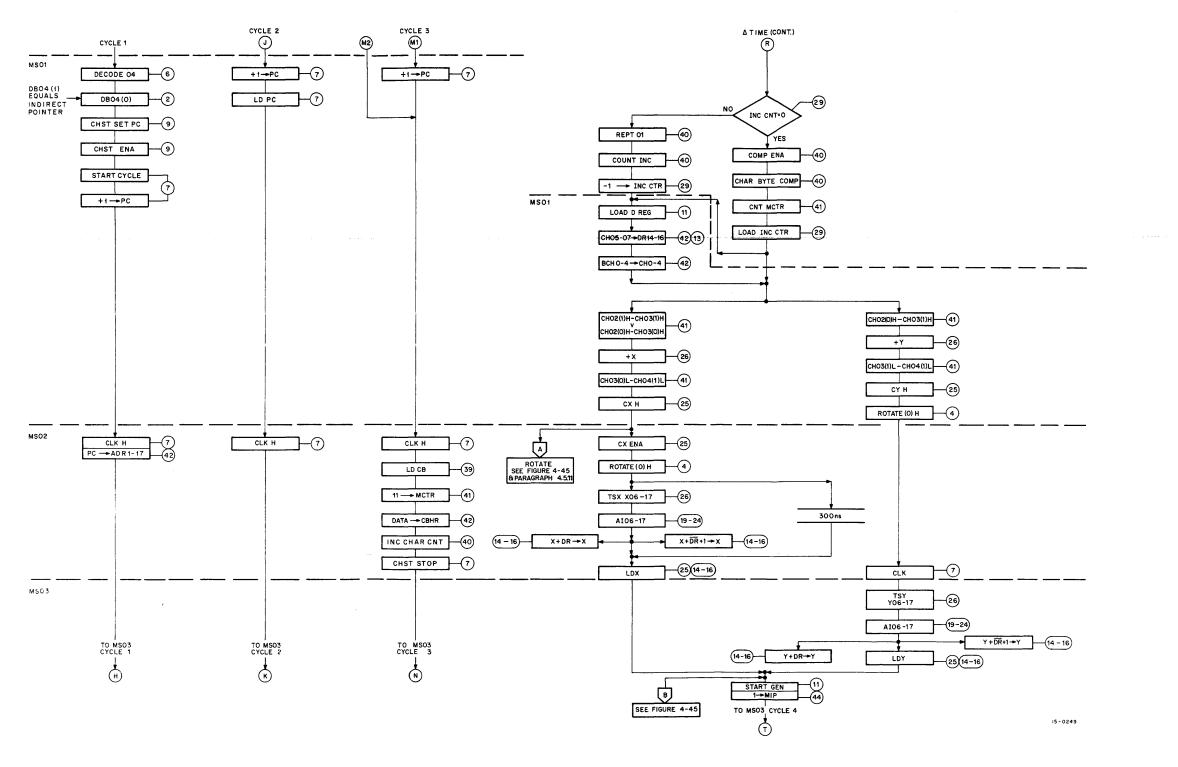

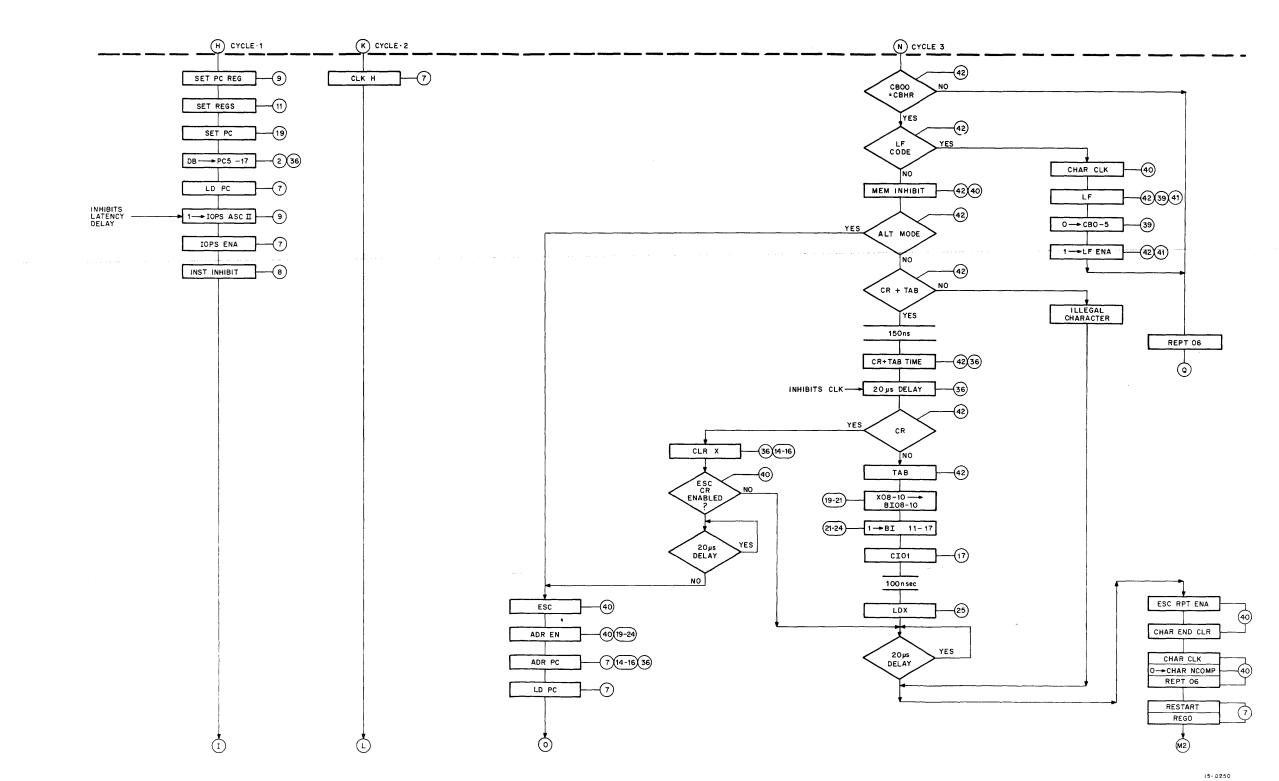

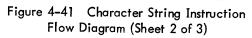

| 4-41          | Character String Instruction Flow Diagram (3 Sheets) | 4-61        |

| 4-42          | IOPS Character Format                                | 4-67        |

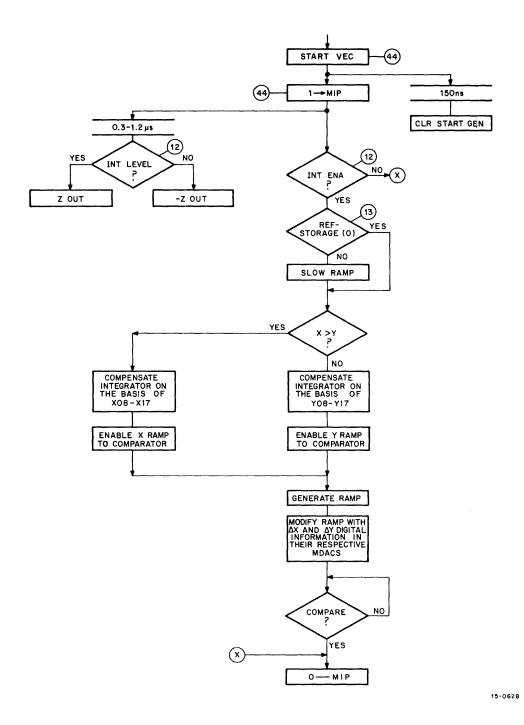

| 4-43a         | Arbitrary Vector Functional Flow Diagram             | 4-70        |

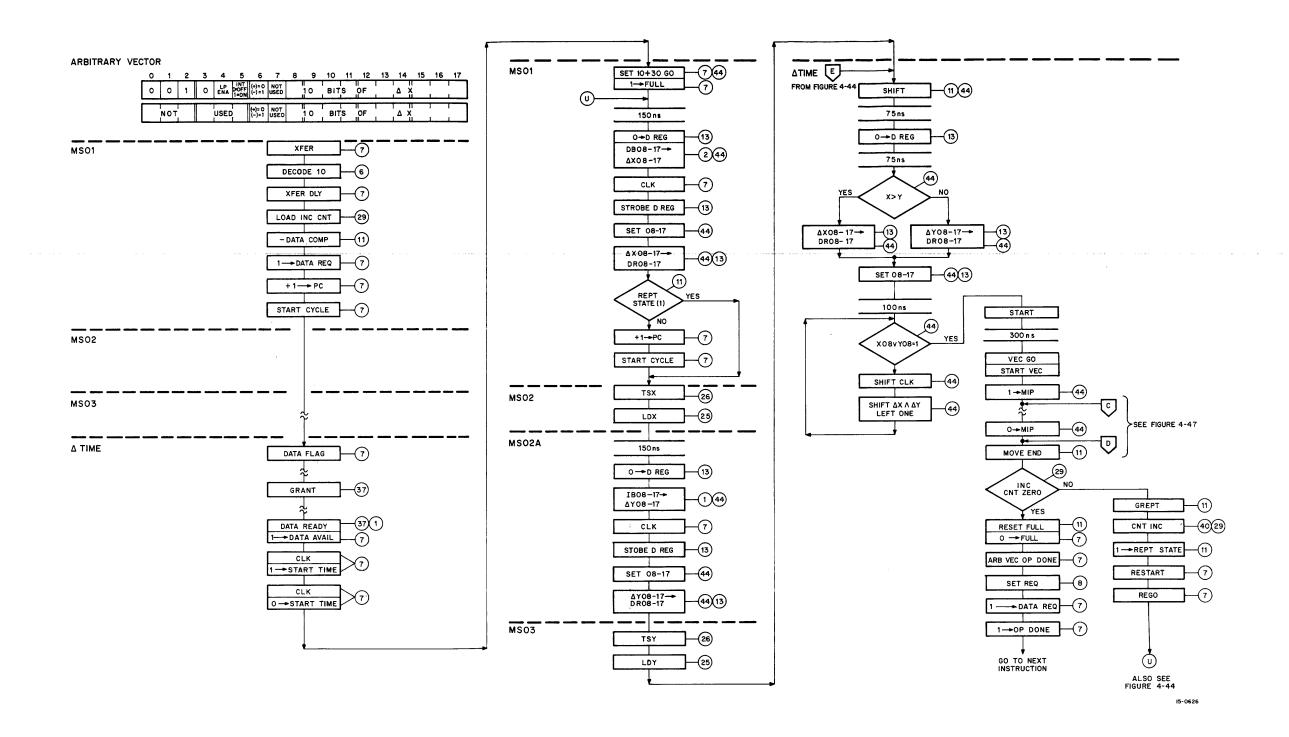

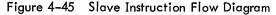

| <b>4-43</b> b | Arbitrary Vector Flow Diagram                        | 4-71        |

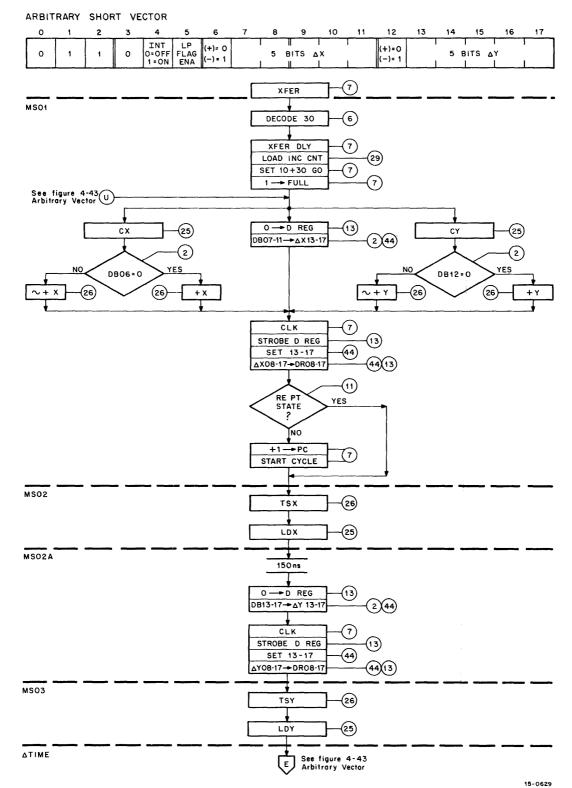

| 4-44          | Arbitrary Short Vector Flow Diagram                  | 4-74        |

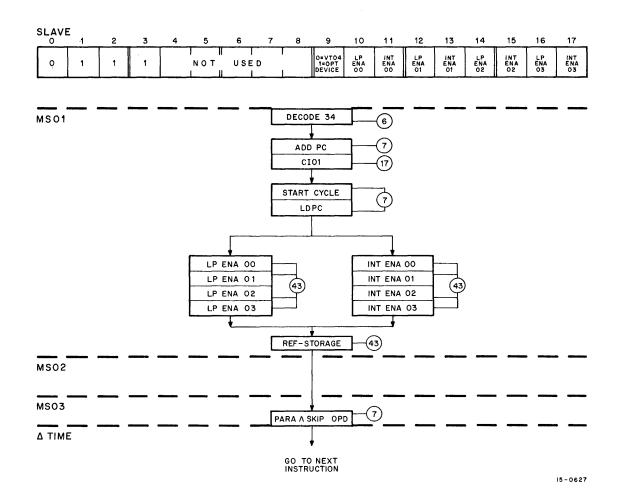

| 4-45          | Slave Instruction Flow Diagram                       | 4-75        |

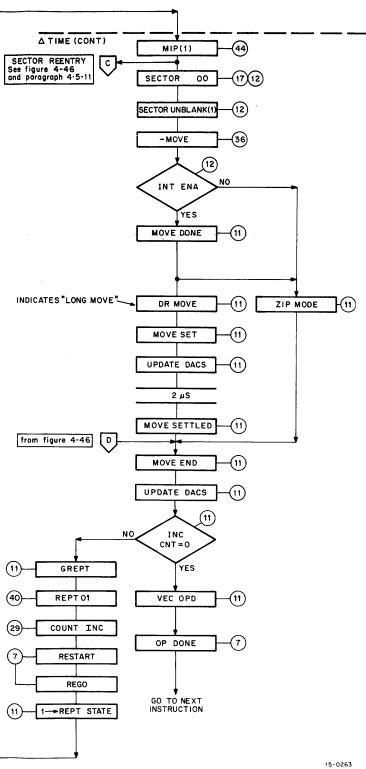

| 4-46          | Rotate Flow Diagram                                  | 4-77        |

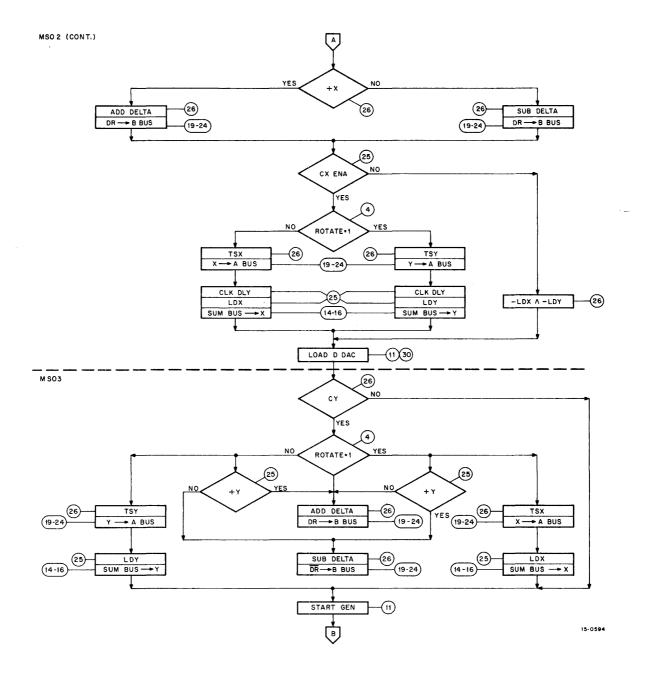

| 4-47          | Sector Re–Entry Flow Diagram                         | 4-78        |

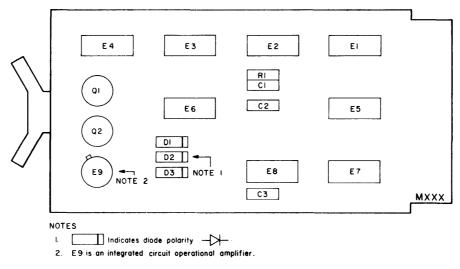

| 5 <b>-1</b>   | Parts Location – Example Diagram                     | 5 <b>-2</b> |

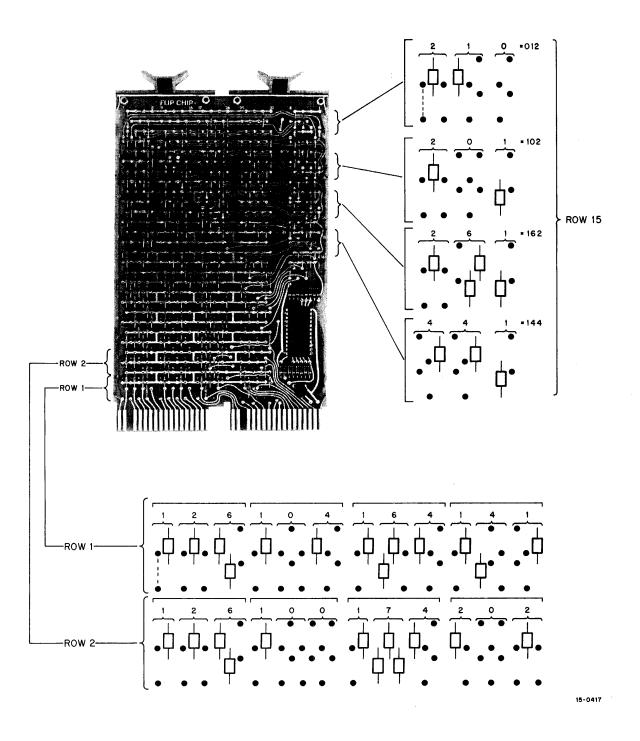

| 5 <b>-2</b>   | Character "YA" Board and Character Selection         | 5-5         |

| 5-3           | G618 Diode Matrix                                    | 5 <b>-7</b> |

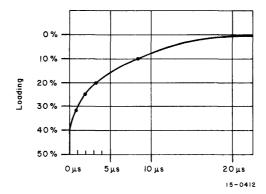

| 6-1           | I/O Loading Delay Characteristics                    | 6-5         |

|               |                                                      |             |

# TABLES

| Table No. | Title                           | Page |

|-----------|---------------------------------|------|

| 2-1       | Wiring Jumper Table             | 2-3  |

| 2-2       | Power Cable Line Identification | 2-3  |

| 2-3       | System Checks and Adjustments   | 2-7  |

| 4-1       | VT15 Paper Area Sizes           | 4-7  |

| 4-2       | Line Pattern Codes              | 4-34 |

TABLES (Cont)

| Table No.   | Title                                          | Page |

|-------------|------------------------------------------------|------|

| 4-3         | Pushbutton Bank Address Codes                  | 4-37 |

| 4-4         | Basic Vector Directions                        | 4-42 |

| 4-5         | Save/Restore Parameters                        | 4-54 |

| 4-6         | Character String Parameters                    | 4-60 |

| 4-7         | ASCII Character Control Codes                  | 4-68 |

| 5-1         | Special Module Drawing Reference Numbers       | 5-1  |

| 5 <b>-2</b> | ASCII Character Decoding                       | 5-4  |

| 5-3         | Hardware Generated Characters                  | 5-4  |

| 5-4         | ROM Memory G618 Module Selection               | 5-5  |

| 5-5         | Character "A" Byte and Bit Decoding            | 5-6  |

| 5-6         | M761 Byte Counter                              | 5-9  |

| 5-7         | Module Output Designations                     | 5-10 |

| 5-8         | M761 Module Output Designations and Parameters | 5-10 |

| 6-1         | Equipment Required                             | 6-2  |

| 6-2         | Power Supply Output Checks                     | 6-4  |

| 6-3         | Drawing Number Index                           | 6-13 |

#### FOREWORD

The VT15 Graphic Display Processor Maintenance Manual is part of a two volume set. Volume 1 is a basic description of the VT15 Graphic Processor system and related logic circuits; Volume 2 is a complete engineering drawing set for the VT15 Graphic Processor.

This publication consists of six chapters that cover the following general topics:

Chapter 1 consists of a general description, functional and physical characteristics, options, terminology, etc.

Chapter 2 consists of a variety of installation procedures, for example: unpacking, initial setup, power-up, diagnostic programs, etc.

Chapter 3 contains a detailed description of the operation of the VT15 Graphic Processor to the functional group level.

Chapter 4 is a discussion of instruction flow analyses.

Chapter 5 contains a detailed description of the special modules contained in the VT15 Graphic Processor system.

Chapter 6 consists of maintenance procedures for the VT15 Graphic Processor. A variety of topics are discussed including diagnostic programming, preventive maintenance, mechanical and electrical checks, and troubleshooting.

Additional reference documents and programs supplied with the Graphic-15 Display System or previously with the PDP-15 computer are as follows:

#### **Reference Documents**

| Document No.  | Title                                                   | Source |

|---------------|---------------------------------------------------------|--------|

| 042 00370 AKO | Logic Handbook                                          | DEC    |

| 142 00970 APH | Control Handbook                                        | DEC    |

| DEC-15-GWSB-D | Graphic–15 Reference Manual                             | DEC    |

| DEC-15-H2DA-D | PDP-15 Users Handbook                                   | DEC    |

| DEC-15-H2AB-D | PDP-15 Installation Manual                              | DEC    |

| DEC-15-BRZA-D | PDP-15 Reference Manual                                 | DEC    |

| DEC-15-HOAB-D | PDP–15 Interface Manual                                 | DEC    |

| DEC-15-H2EA-D | PDP-15 Module Manual                                    | DEC    |

| DEC-15-H2GB-D | VT04/VT07 Graphic Display Console<br>Maintenance Manual | DEC    |

#### Maintenance Programs

| Document No.     | Description                                                             |

|------------------|-------------------------------------------------------------------------|

| MainDEC-15-DAVTB | Display Instruction Test (VT15 IT) Part 1                               |

| MainDEC-15-DAVTA | Display Instruction Test (VT15 IT) Part 2<br>(Manual Intervention Test) |

| MainDEC-15-D6DD  | Display Visual Test (VT15 VT)                                           |

| MainDEC-15-D6EC  | Little Pictures Test (VT15 LP)                                          |

# CHAPTER 1 VT15 BASIC DESCRIPTION

This manual is one of two documents related to the VT15 Graphic Display Processor (see Figure 1-1). The VT15 Graphic Processor and a Graphic Display Console comprise the Graphic-15 Display System. This manual provides a basic understanding of VT15 Graphic Processor operation and capabilities and assumes that the user is familiar with the technology of the PDP-15 Computer and similar systems. For a complete list of maintenance program documents for the PDP-15 Programmed Data Processor and the Graphic-15 Display System, the user should refer to the list provided in the Foreword of this manual. In-depth operation and programming information for the Graphic-15 Display System is contained in the Graphic-15 Reference Manual.

#### 1.1 PURPOSE AND SCOPE

Installation, operation, maintenance, and troubleshooting information for the VT15 Graphic Processor is provided in Volumes 1 and 2 of this manual. Volume 1 describes the basic VT15 Graphic Processor system and discusses the logic circuits in terms of the program instruction repertoire at the functional group level; modules that are unique to the VT15 are described and discussed in greater detail. Volume 2 contains a complete set of engineering drawings for the VT15 Graphic Processor.

#### 1.2 FUNCTIONAL DESCRIPTION

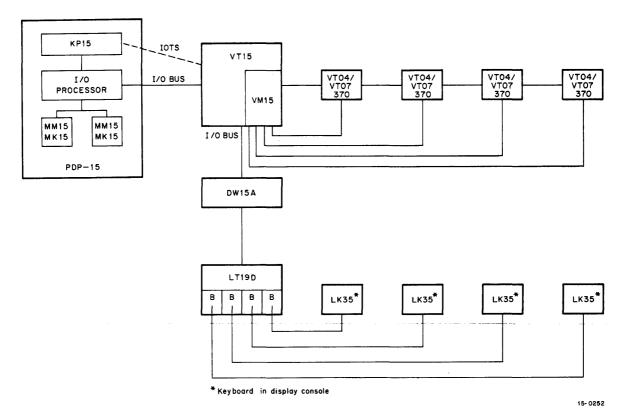

The VT15 Graphic Processor is an 18-bit, general-purpose, graphic processor, which, combined with the PDP-15 Programmed Data Processor and a display console, comprises the total, basic Graphic-15 Display System (see Figure 1-2).

The VT15 provides the digital-to-analog interface between the PDP-15 Computer and the display console; this interface accelerates the exchange of instructions and data between the user, the PDP-15 Computer, and the display console. The VT15 interacts with the PDP-15 through the system hardware to display immediate solutions to a broad range of complex electrical, physical, and mechanical design and analysis problems.

Figure 1–1 VT15 Graphic Processor

Figure 1-2 Graphic-15 Display System Interconnect Diagram

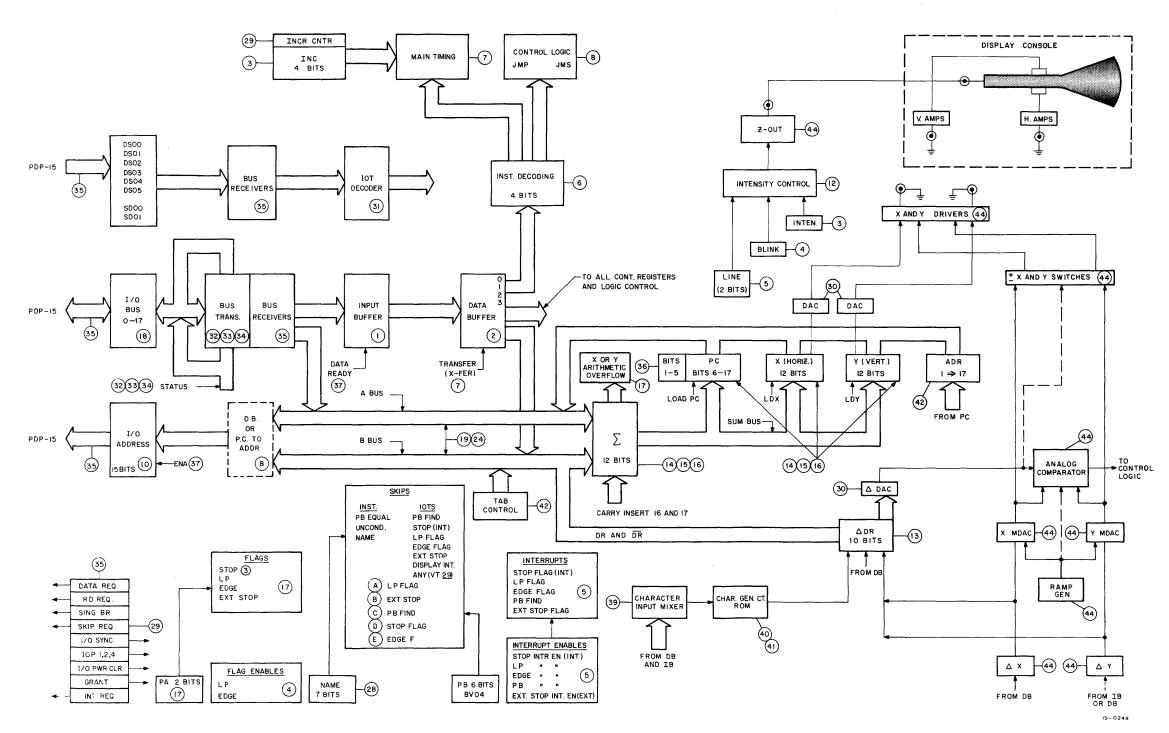

Because the VT15 and PDP-15 Computer share the same (PDP-15) core memory, their programs must interact through the system hardware. For example, the VT15 interacts through the PDP-15 I/O processor (see Figure 1-3) to obtain its operating instructions.

The VT15 program, called the Graphic-15 Display File, is sequentially stored in the PDP-15 core memory. The contents of the display file, in the form of digital instructions and data, are read from the computer core memory, decoded, and then operated on. Digital data to be displayed is converted to analog voltages by the VT15 and transmitted to the display console to drive the X- and Y-deflection circuits of the display CRT. A set of eight basic instructions gives the VT15 system exceptional versatility in the display of points, basic vectors, graph plots, figures, and ASCII characters. Access to the display file is gained by issuing an initial Input/Output Transfer (IOT) command; this instruction starts the transfer of display file instructions through the I/O processor single-cycle data break facility. Thus, the PDP-15 I/O processor controls communication between the VT15 and the PDP-15 core memory and/or central processor; although the VT15 uses the PDP-15 program-controlled IOT facilities for initializing instruction transfers, for computer skip testing, and for read status functions, the basic mode of data and instruction transfers is the single-cycle data break facility of the PDP-15 Computer. In this system, a request originates from the VT15. When the request for data is honored by the

Figure 1–3 VT15 Functional Block Diagram

PDP-15 I/O Processor, the desired instruction, located at the core memory address specified by the VT15 program counter (PC), is read into the VT15 input buffer register. The instruction is then processed by the VT15, and the VT15 program counter is incremented. At the conclusion of the operating cycle, another request is forwarded from the VT15. When the next request is honored, the cycle is repeated. The cycle continues to be repeated until all desired instructions in the display file have been processed.

Thus, on initialization of the pre-programmed display file through a program-controlled IOT command, control is transferred to the VT15, which operates autonomously with respect to the PDP-15, freeing the PDP-15 for computing and I/O operations.

Although the PDP-15 and VT15 share the same memory and the VT15 is asynchronously controlled, the VT15 interacts with the PDP-15 Computer through the IOT instructions and the data channel single-cycle data break facilities.

The VT15 consists of six major functional groups (see Figure 1-3): input/output (I/O) control, data collectors, timing and control, main registers, digital-to-analog converters, and an analog function generator.

The I/O control, data collectors, control and timing, main registers, and digital-to-analog converters (DACs) deal with digital inputs supplied from the PDP-15 Computer. The digital-to-analog converters and the analog function generator (AFG) and related circuitry interact to convert the PDP-15 derived digital data to analog voltage outputs, which are output to the display console to generate the desired image on the display console CRT.

Thus, the basic VT15 consists of the I/O control, coordinate and parameter registers, control and timing circuitry, digital-to-analog converters, an ASCII character generator, an analog function generator, and associated system power supplies. Table 6-2 lists the dc power supplies and corresponding operating voltages required for VT15 operation. Power supply schematics are provided in Volume 2.

#### 1.3 PHYSICAL DESCRIPTION

The VT15 Graphic Processor is self-contained in a single, standard DEC Type H950 cabinet; four casters permit cabinet moveability. Overall cabinet dimensions are: height 71.44 in., width 21.69 in., and depth (front to rear) 30.00 in. Drawing VT15-A-0 in Volume 2 shows the front and side dimensional views of the VT15. The top, front panel as shown in Drawing VT15-A-0 (frontview) is a 7006331-2 Peripheral Indicator Panel. The second panel is a blank panel. The next four successive panels are Type H911 module mounting panels. The logic modules are mounted in the four mounting racks immediately behind the four front panels.

#### 1.4 SYSTEM OPTIONS

The VT15 is prewired to accept the VV15 Arbitrary Vector Generator and the VM15 Display Console Multiplexer options. The VV15 Arbitrary Vector Generator option provides the capability of drawing a vector of any arbitrary angle on the display console CRT.

The VM15 Display Console Multiplexer option provides the capability to interface up to four VT04/VT07 Display Consoles and four VL04 Light Pens with one VT15 Graphic Processor.

#### 1.5 SYSTEM SPECIFICATIONS

#### **Operating Requirements**

| Operating Temperature Range                        | +40° to +95°F                                                                                 |

|----------------------------------------------------|-----------------------------------------------------------------------------------------------|

| Operating Humidity Range<br>(without condensation) | 20% to 55% (relative)                                                                         |

| Power Requirements                                 | 120V ±15%, 60 cps ±2%, single-phase, 17-30A or<br>230V ±15%, 50 cps ±2%, single-phase, 17-30A |

| Power Consumption                                  | 2 KW                                                                                          |

| Dimensions                                         |                                                                                               |

| Cabinet Height                                     | 71.44 in.                                                                                     |

| Cabinet Width                                      | 21.69 in.                                                                                     |

| Cabinet Depth                                      | 30.00 in.                                                                                     |

| Shelf Width                                        | 19.00 in.                                                                                     |

| Cabinet Weight                                     | 300 lb (approximate)                                                                          |

#### 1.6 REFERENCING CONVENTIONS

The following paragraphs briefly describe the referencing conventions used in this manual.

- a. Numerical Notation Unless otherwise specified, all number representations are in octal notation.

- b. Circuit References All references to logic signals include the module-type designation, module location code, and output pin designation; e.g., D-Type Flip-Flop M206-F30-E1 indicates that Module M206 is located in rack F, slot 30, and the output signal is taken from pin E1. All racks are designated alphabetically from top to bottom as viewed from the module mounting side. All module mounting slots are numbered 01 through 32 from right to left beginning with the top rack. Slots 1 through 4 of the top or first H911 mounting rack contain the analog output cables. Modules are mounted vertically in the slots. Dual width modules carry dual location designations; e.g., M761-CD13-CK2 where CK2 indicates pin K2 in the C slot of dual location CD, DK2 would indicate pin K2 in the D slot of dual location CD; e.g., M761-CD13-DK2.

- c. Signal Mnemonics Uncommon mnemonics are explained parenthetically the first time they are mentioned in the discussion; e.g., LSD (load and start display). A glossary of all signal mnemonics, their octal code and operation executed is listed in Appendix A of the Graphic-15 Reference Manual.

- d. Illustrations References to in-text illustrations include the chapter prefix number;

e.g., Figure 3-5 is the fifth illustration in Chapter 3. References to engineering drawings contained in Volume 2 will be designated by the drawing number; e.g., (VT15-0-1), indicating drawing number 1 of the VT15 Graphic Processor engineering drawing package.

#### 1.7 TERMINOLOGY

Terms used frequently throughout the text are defined below. Other terms are defined within the various discussions.

- a. Alternate Mode Alternate mode (ALT MODE) is ASCII character 1758. When the character string instruction has been initiated, it remains active until terminated by the generation of an "escape." One method of terminating a character string is through the generation of ALT MODE.

- b. Carriage Return Carriage return (CR) is ASCII character 215. The carriage return key causes the CRT beam to return to the left edge of the paper area. Carriage return can also be used to generate an "escape."

- c. Delta Move Time Delta △ move time is the time that elapses from the beginning of beam movement to the completion of movement of the beam. Therefore, because CRT beam movement time is constantly varying according to the instruction specified, the term △ move time is used.

- d. Direct Address The effective address in a memory reference instruction word of a location in core memory that contains an operand.

- e. Display File The VT15 relies on the PDP-15 core memory for storage of the VT15 display file (program), which contains the data and instructions on which the VT15 operates. The single-cycle data break facility enables the digital inputs required by the VT15 to be entered into its input buffer directly from the programmed, sequentially stored, display file (program) in the PDP-15 core memory. The display file is initially entered via an initializing program-controlled input/output transfer. When the display file has been initialized, the VT15 functions autonomously with respect to the PDP-15.

- f. Effective Address The address of an operand in core memory. It can be an actual address in core memory or an address in core memory that is designated by an indirect address in a memory reference instruction (MRI) word.

- g. Escape (ESC) Mode The escape mode is used in conjunction with the character string instruction. With ALT MODE or CR enabled, ESC is generated, terminating character string.

- h. Indirect Address The addressing in a memory reference instruction word of a location in computer core memory that contains an effective address.

- Input/Output Pulse (IOP) Code The last three bits (15, 16, and 17) of the VT15 IOT commands are the IOP codes; IOP4 (bit 15), IOP2 (bit 16), and IOP1 (bit 17). IOP4 is used to effect the transfer of data from the PDP-15 to the VT15 (or peripheral). IOP2 is used to effect the transfer of data from the device, in this case the VT15 to the PDP-15. IOP1 is used to effect I/O skip instructions to test for a device flag or other control function.

- j. Main Registers The main registers consist of four data holding registers, the Xposition and Y-position registers for the X- and Y-axes, the magnitude of change (Δ) register and the VT15 program counter (PC). Outputs from the position and Δ registers (Δ Word, X Word, and Y Word) are applied to the digital-to-analog converters.

- k. Name Register This register is a 7-bit holding register that permits the identification of up to 128 graphic constructions in the display file. Thus, 128 different 7-bit "names" can be used to name and tag 128 different display files or subroutines.

- 1. Program Interrupt An interruption in the computer program caused by a device service flag. The interrupt is granted on completion of the current instruction.

- m. TAB The ASCII code TAB is used to specify tabular columns of characters. Tabs begin nine character positions to the right of the normal first character position.

#### **1.8 ENGINEERING DRAWINGS AND CIRCUIT SCHEMATICS**

A complete set of VT15 engineering drawings, and power supply and special module schematics are provided in Volume 2 of this manual. Only schematics for special modules that are unique to the VT15 are provided. Remaining module schematics are shown in the Module Manual. A listing of the engineering drawings is provided in Table 6-3. Drawings are listed numerically by drawing code; e.g., VT15-0-01, where VT15 indicates the VT15 Graphic Processor, and 01 indicates the drawing number for the VT15 input buffer. Logic symbols used on the drawings are defined in the Logic Handbook, Document No. 042D 00370 AKO and in the PDP-15 Module Manual, DEC-15-H2EA-D.

# CHAPTER 2 INSTALLATION

This chapter provides planning, site preparation, preinstallation, and installation information and recommendations to ensure a successful VT15 Graphic Processor installation.

Digital Equipment Corporation (DEC) provides customer assistance in all phases of site planning. A final layout plan should be approved jointly by the customer and DEC regardless of whether the VT15 Graphic Processor, the PDP-15 Computer, and the display console are installed concurrently, or the VT15 and/or display console are integrated into a previously installed PDP-15 Computer layout plan that may necessitate remodeling of the selected installation site. Site preparation is keyed to the customer's applicable requirements and can range from providing the required source power to construction or remodeling of the selected installation site.

The customer should prepare a list of the actual equipment to be used in the installation. The list should include such items as storage cabinets, work tables, desks, etc., as well as any other items pertinent to the customer's computer application. From this list, the customer can accurately determine his space requirements. Integration of the work area with the storage area can be considered in relation to the work flow requirements between areas.

Additional considerations of importance are: the provision for and availability of adequate power, fire and personnel safety precautions, and proper environmental conditions. Personnel and equipment safety precautions, environmental considerations, and system installation restraints are covered in greater detail in Paragraphs 1.4, 1.5, and 1.6 of the PDP-15 Systems Installation Manual. Functional, physical, and environmental characteristics, and system specifications for the VT15 are provided in Chapter 1 of this manual.

#### 2.1 UNPACKING

#### CAUTION

Do not attempt to install the system until DEC has been notified, and a Field Service Representative is present. Carefully inspect the VT15 for damage. Any damage should be reported immediately. Unpack the system according to the following procedures:

# Step

#### Procedure

1

# Remove the outer shipping container.

#### NOTE

The container may be either heavy corrugated cardboard or plywood. In either case, first remove all metal straps, then remove any fasteners and cleats securing the container to the skid. When applicable, remove wood framing and supports from around the cabinet perimeter.

- 2 Remove the polyethylene cover from the cabinet.

- 3 Remove tape and/or plastic shipping pins as applicable from the cabinet rear access door.

- 4 The cabinet is secured to a type 7605469-1 skid with retaining bolts. Access to these bolts can be obtained by opening the cabinet rear access door and locating the bolts on the lower supporting siderails. Remove the retaining bolts.

- 5 Ensure that the cabinet leveling feet are raised above the level of the roller-casters.

- 6 Using wooden blocks and planks, form a ramp from the shipping skid to the floor and carefully roll the cabinet off the skid onto the floor.

- 7 Roll the system to the proper location for installation.

- 8 When the cabinet is in the desired position, lower the leveling feet so that the cabinet weight rests on the leveling feet and not on the roller-casters.

- 9 Use a spirit level to level the cabinet; make certain that all leveling feet are seated firmly on the floor.

#### 2.2 PRIMARY AC POWER CABLES

The primary ac power cable is a three-wire cable that interconnects the site power source to the VT15 Graphic Processor power supplies. The cable is connected at the factory to the VT15 841C Power Controller for either 110V or 220V operation.

#### CAUTION

Before proceeding, ensure that the VT15 power transformer primary windings are correctly connected (for 110V or 220V operation) to correspond to the installation site source power voltage (Table 2-1). System wiring diagrams (Drawings VT15-A-0 and VT15-A-2) are provided in Volume 2.

| Power Supply<br>or Control | Input | From                      | То                                          |  |

|----------------------------|-------|---------------------------|---------------------------------------------|--|

| H721                       | 220∨  | TB1-2<br>TB1-4            | TB1-3<br>TB1-5                              |  |

|                            | 110V  | TB1-1<br>TB1-2<br>TB1-3   | TB1-3<br>TB1-4<br>TB1-5                     |  |

| 841C                       | 220V  |                           | (2) Orange 110 Vac<br>INPUT jumpers removed |  |

|                            | 110   | (2) Orange ju<br>in place | umpers                                      |  |

Table 2–1 Wiring Jumper Table

A jumper connection chart is also provided on the top cover of the H721 main power supply. Each wire in the power cable is color coded as shown in Table 2–2.

| Pigtail Information            |       | Touring Strip Neuropolaturos |

|--------------------------------|-------|------------------------------|

| Line Wire Color Terminal Strip |       | Terminal Strip Nomenclatures |

| Frame Ground                   | Green | Frame Ground                 |

| Neutral/Line 2                 | White | Neutral or Line 2            |

| Line 1                         | Black | Line 1                       |

Table 2-2Power Cable Line Identification

#### WARNING

The green wire is the cabinet frame ground and does not carry load current but must be connected for personnel safety. It must be securely connected between the VT15 cabinet and the primary power source grounding point.

The white (or light gray) wire is the neutral, common, ac return, or cold load and should never be used for VT15 cabinet grounding purposes.

The VT15 is normally supplied with a 30A Hubbel connector. The ac service outlet to be used must be capable of at least 20A ac, 110V, 60 Hz single phase or 10A ac, 220V, 50 Hz single phase.

#### 2.3 INITIAL SETUP

### 2.3.1 VT15 Power Connections

Use rhe following procedure for the initial power check of the VT15:

| Step |                                                  | Procedure                                                                                                                                                                                             |                 |  |

|------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|

| 1    | •                                                | Switch the power control circuit breaker to OFF. Set the power control LOCAL-REMOTE switch to LOCAL.                                                                                                  |                 |  |

| 2    | receptacle to ensure that the                    | Refer to Figure 3-4 of the <u>PDP-15 Installation Manual</u> . Meter the wall receptacle to ensure that the hot, neutral, and ground connections con-<br>form to the description given in Figure 3-4. |                 |  |

| 3    | •                                                | Connect the power cord to the wall receptacle and ensure that the orange indicator lamp on the 841C Power Control Lights.                                                                             |                 |  |

| 4    | Locate and remove the 4 fuse<br>the logic rack.  | Locate and remove the 4 fuses from the logic panel located on the front of the logic rack.                                                                                                            |                 |  |

| 5    | Set the power control circuit                    | breaker to ON                                                                                                                                                                                         | •               |  |

| 6    | With a multimeter or voltmet<br>output voltages: | With a multimeter or voltmeter, check the following pins for the specified output voltages:                                                                                                           |                 |  |

|      | From                                             | To                                                                                                                                                                                                    | Voltage Reading |  |

|      | Pin A20D2                                        | Pin A20F2                                                                                                                                                                                             | +15.0V          |  |

|      | Pin A20E2<br>Any pin A2 on Logic Rack            | Pin A20F2<br>Ground                                                                                                                                                                                   | -15.0V<br>0V    |  |

| 7    | ,, .                                             | Set the power control circuit breaker to OFF.                                                                                                                                                         |                 |  |

| 8    | Replace top fuse.                                |                                                                                                                                                                                                       |                 |  |

| 9    |                                                  | Set the power control circuit breaker to ON.                                                                                                                                                          |                 |  |

| 10   |                                                  | Measure $+5V \pm .1V$ from pin A20A2 to ground.                                                                                                                                                       |                 |  |

| 11   | Set the power control circuit                    | Set the power control circuit breaker to OFF.                                                                                                                                                         |                 |  |

| 12   | Replace the lower 3 fuses.                       | Replace the lower 3 fuses.                                                                                                                                                                            |                 |  |

|      |                                                  |                                                                                                                                                                                                       |                 |  |

#### 2.3.2 Cable Installation

The VT15 is normally the last device on the PDP-15 Computer I/O bus. Figure 2-1 shows the various cable lengths and corresponding cable delay settings. To connect the VT15 to the positive I/O bus, reference drawing D-IC-VT15-A-2 and perform the following procedure:

| Step | Procedure                                                                                                                                                             |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Determine the last positive I/O device connected to the positive I/O bus in the present configuration.                                                                |

| 2    | Remove the four M909 I/O Bus Terminator Modules (68 ohm) from the I/O bus output slots of the last positive I/O device. This applies for "add-on" installations only. |

|      | (continued on next po                                                                                                                                                 |

(continued on next page)

| Step | Procedure                                                                                                                             |

|------|---------------------------------------------------------------------------------------------------------------------------------------|

| 3    | Insert one end of the $I/O$ bus cable into the slots from which the M909 Modules were removed.                                        |

| 4    | Insert the opposite end of the I/O bus cable into slots H–J–29 and H–J–30 of the VT15 I/O receptacle.                                 |

| 5    | Insert the four M909 Terminator Modules into slots H31, H32, J31 and J32 of the VT15.                                                 |

| 6    | The X, Y and Z analog cables must be terminated with 100 ohms (part no. 1300229) at the end of each cable run.                        |

| 7    | Connect the VT15 remote power cord from the VT15 (841C) power control to the nearest PDP-15 system power control.                     |

| 8    | Connect the data and control cable to slot H–J–3 of the VT15.<br>Connect the opposite end of the cable to slot AB06 in the VT04/VT07. |

Figure 2-1 Delay Setting vs Cable Lengths

# 2.3.3 System Power-Up

After all power checks and cabling have been completed, perform the following power-up procedure:

| Step | Procedure                                                                                                                                                                                                                     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Set the VT15 LOCAL-REMOTE switch and display console power con-<br>trols to REMOTE.                                                                                                                                           |

| 2    | Locate the intensity control on the back of the display console and turn<br>the control fully counterclockwise to the minimum position. Set gain<br>fully counterclockwise to minimum and the centering controls to midrange. |

| 3    | Set the PDP-15 POWER switch to ON.                                                                                                                                                                                            |

|      | (continued on next page)                                                                                                                                                                                                      |

| Step | Procedure                                                                                                                                                                                                                                        |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 4    | Load and run MainDEC–15–D6EC–D, Little Pictures Test, beginning with Routine 0.                                                                                                                                                                  |  |

|      | CAUTION                                                                                                                                                                                                                                          |  |

|      | Exercise extreme care when adjusting intensity<br>controls to avoid burning the CRT screen. If<br>adjustments are such that the screen cannot be<br>seen, another person should be present to ob-<br>serve the CRT during intensity adjustments. |  |

| 5    | Increase the intensity control slowly until a pattern is seen. If a bright spot should appear, immediately decrease the intensity. Ad-<br>just the CRT X- and Y-gain and centering to correctly position the images on the screen.               |  |

| 6    | Select Routine 5 and run the Intensity Level Test. Adjust the intensity<br>level until level 1 can barely be seen. Intensity level 0 should not be<br>visible (under ambient lighting conditions).                                               |  |

#### 2.4 CUSTOMER ACCEPTANCE

Customer acceptance of the VT15 consists of system operation by running all diagnostic programs provided, an operating test of the system software, inspection of the shipping list, inspection of the software kit, and a physical inspection of the system. No physical damage should be observed, and the shipping list and software kit should be complete.

#### 2.4.1 Checklist

A checklist is provided with each system to ensure that the following have been accomplished and/or included. Refer to the Foreword for document reference numbers.

- a. QC Check

- b. Manuals

Graphic-15 System Reference Manual VT15 Graphic Processor Maintenance Manual, Volumes 1 and 2

c. Other Documents

Key Sheet ECO Sheet d. Cables

(1 ea) BC09B, BS01A(2) ac Remote Turn-on power cords

e. Diagnostic Software

The diagnostic software is described in Paragraph 2.4.2.

#### 2.4.2 Diagnostic Programs

Following are the diagnostic programs provided with the VT15 Graphic Processor. Detailed program and test descriptions are provided with each diagnostic program.

| a. | MAINDEC-15-DAVTB                 |                                                                                      |

|----|----------------------------------|--------------------------------------------------------------------------------------|

|    | Display Instruction Test, Part 1 | 15 minutes error free.                                                               |

| b. | MAINDEC-15-DAVTA                 |                                                                                      |

|    | Display Instruction Test, Part 2 | No time limit, manual intervention required.                                         |

| c. | MAINDEC-15-D6DD                  |                                                                                      |

|    | Display Visual Test              | 15 minutes error free.                                                               |

| d. | MAINDEC-15-D6EC                  |                                                                                      |

|    | Little Pictures Test             | No time limit, each individual routine is checked against test photographs supplied. |

#### 2.5 SYSTEM CHECKS AND ADJUSTMENTS

If a malfunction occurs during system checkout, the fault or problem must be isolated. Fault isolation and troubleshooting procedures are provided in Paragraph 6.5. A listing of system checks and adjustments is provided in Table 2-3.

| Checks and Adjustments             | Paragraph<br>Number | Purpose                                                              |

|------------------------------------|---------------------|----------------------------------------------------------------------|

| H721 Logic Power Supply Adjustment | 6.4.1               | Allows adjustment of the logic power sup-<br>ply voltages.           |

| System Clock Adjustment            | 6.4.2               | Checks the M401 basic clock timing.                                  |

| I/O Loading Delay                  | 6.4.3               | Allows adjustment of the time delay be-<br>tween VT15 data requests. |

Table 2–3 System Checks and Adjustments

(continued on next page)

| Checks and Adjustments     | Paragraph<br>Number | Purpose                                                                                                                                                                           |

|----------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Display Console Bus Delay  | 6.4.4               | Allows adjustment of the time delay used to<br>adjust the duration of MS02 and MS03 to<br>compensate for signal latency in the VT15<br>to display console data and control cable. |

| Move Settle Delay          | 6.4.5               | Allows adjustment of settling delay time<br>for vectors of 17 units or longer in sector<br>zero. This adjustment is also used for CR<br>and TAB.                                  |

| Blink Delay                | 6.4.6               | Allows adjustment of the blink rate (blink timing).                                                                                                                               |

| Long Point Settle Delay    | 6.4.7               | Allows adjustment of the settling time (of<br>approximately 20 µs) which is used during<br>point moves greater than 200g and for<br>sector reentry, CR, and TAB.                  |

| Short Point Settle Delay   | 6.4.8               | Allows adjustment of the settling time<br>(approximately 8 μs) used during point<br>moves less than 177 <sub>8</sub> .                                                            |

| Analog Voltage Adjustments | 6.5.1               | Checks the voltages used in the analog section.                                                                                                                                   |

| Analog Adjustments         | 6.5.2               | Provides initial setup and final adjustment of the analog section.                                                                                                                |

Table 2–3 (Cont) System Checks and Adjustments

#### 2.6 VM15 DISPLAY MULTIPLEX OPTION INSTALLATION PROCEDURE

The VM15 option allows up to four VT04/VT07s to be connected to a single VT15 Graphic Processor. A common bus, comprised of three coaxial cables, is used to output the X, Y, and Z (unblanking) signals, in parallel, to each of the VT04/VT07 displays. An additional cable, designated the "D" and "C" cable, is used to input and output the INT SEL (Intensity Select), PB SEL (Pushbutton Select), and LP PULSE (Light Pen Pulse) signals between the VT15 and the VT04/VT07(s) (see Figure 2–2).

Figure 2-2 VM15 Interconnect Diagram

The standard bus cable length between the VT15 and the first VT04/VT07 (unit 0) is 30 ft. Cables connected between additional VT04/VT07s (units 1, 2, and 3) also have a standard length of 30 ft. Thus, total bus length is 120 ft, with four VT04/VT07s connected to the VT15. A skip 1 latency delay adjustment is required when bus lengths greater than 120 ft are used.

Installation and initial setup procedures for the VT04/VT07 unit 0 are provided in the <u>VT04/VT07</u> <u>Graphic Display Console Maintenance Manual</u>. The following procedures are provided for installation and checkout of the VM15 Display Multiplexer option:

| Step | Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Remove the $100\Omega$ terminator plugs from the X and Y "T" connectors on the rear of unit 0 and connect the X and Y coaxial cables to the corresponding X and Y "T" connectors.                                                                                                                                                                                                                                                                                 |

| 2    | Connect the opposite ends of the X and Y cables to the X and Y "T" connectors on the rear of unit 1. If only the two VT04/VT07s are connected to the VT15, the $100\Omega$ terminator plugs should be installed in the unit 1 X and Y "T" connector outputs.                                                                                                                                                                                                      |

| 3    | Remove the 100 $\Omega$ terminator from the BNC connector designated Z OUT<br>located on the BV04 logic rack of unit 0 and connect the Z coaxial<br>cable. Connect the opposite end of the Z coaxial cable to the BNC<br>connector designated Z IN on the BV04 logic rack of unit 1. If only<br>two units are to be connected to the VT15, install a 100 $\Omega$ terminator<br>plug in the BNC connector designated Z OUT on unit 1.<br>(continued on next page) |

| Step | Procedure                                                                                                                                                                                                                                                |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | NOTE<br>Regardless of the number of VT04/VT07s connected<br>to the VT15, $100\Omega$ terminators must be installed in<br>the X, Y, and Z outputs of the last unit.                                                                                       |

| 4    | Connect the data and control (D and C) cable from slot AB08 in unit 0<br>to slot AB06 in unit 1. If only two units (0 and 1) are to be connected,<br>insert the two M909 Terminator Modules, removed from unit 0, into<br>slots A08 and B08 of unit 1.   |

| 5    | If more than two VT04/VT07s are to be connected to the VT15, unit 2 is<br>connected to unit 1 in the same manner that unit 1 was connected to<br>unit 0, etc. All terminators will be installed in the last VT04/VT07<br>that is electrically connected. |

There are two W719 Unit Select Modules in each VT04/VT07. The W719 Module located in slot B18 is used to select the light pen and intensity enable for each unit. The W719 Module, located in slot A10, is used to select the console pushbuttons (see drawing BV04-0-2 in Volume 2 of the VT04/VT07 Graphic Display Console Maintenance Manual). The W719 Unit Select Module is shown in Figure 2-3.

Figure 2-3 W719 Unit Select Module

When running the VM15 Multiplexer Test under normal conditions, the unit select switches should be set so that each display console has a different logical unit select number (address); i.e., 00, 01, etc. However, during alignment the intensity select switches should all be set to unit 0 to allow the test patterns produced by the VT15 Little Pictures diagnostic to be displayed simultaneously on all display CRTs.

# CHAPTER 3 SYSTEM OPERATION

#### 3.1 SYSTEM ORGANIZATION

The primary function of the VT15 Graphic Processor is to convert digital instruction inputs from the PDP-15 Computer into analog signals to drive the X- and Y-deflection circuits of the display console CRT. The inputs are basically two types: program input/output transfer (IOT) instructions and display file instructions. IOTs are program-controlled whereas the display file instructions are obtained via the single-cycle data break facility. The VT15 Graphic Processor consists of six major functional groups: I/O control, data collectors, timing and control, main registers, digital-to-analog converters, and analog function generator.

These six major functional groups (see Figures 3-1 and 3-2) combine to control the interactive functions of the VT15 Graphic Processor, the PDP-15 Computer, and the graphic display console(s). The VT15 has an indicator panel that can be referenced during operation and maintenance to indicate the operational status of the VT15 Graphic Processor.

Figure 3-1 Major Functional Groups, Interconnect Diagram

15-0268

#### 3.1.1 I/O Control

3.1.1.1 Data Channel (DCH) Control and Automatic Priority Interrupt (API) Multiplexer – The DCH control consists of an M104 Data Channel Multiplexer Module, associated gating, and pulse amplifiers. A VT15 data request and I/O SYNC initiate a single-cycle break (SING BR) request. If a higher priority device has not requested use of the I/O bus, the VT15 will receive a GRANT from the computer. With GRANT and REQ coincident, enable A (ENA) will be set indicating the VT15 has use of the I/O address (ADR) lines. ENA gates the address off the VT15 address lines and onto the I/O address lines of the I/O bus, clears the data request and REQ flip-flops, and gates the read or write request lines. DCH control is depicted in greater detail in Figure 4-12 of the PDP-15 Systems Interface Manual.

3.1.1.2 Read Cycle – If the VT15 requests a read cycle as a result of a jump-to-subroutine (DJMS) or SAVE instruction, data is gated on the bus at the time ENA occurs. A pulse called DATA ACCEPT is produced on the (1) to (0) transition of GRANT, indicating to the VT15 that the computer has accepted its data, and the VT15 may proceed with its timing.

3.1.1.3 Write Cycle – If the VT15 requests a write cycle, a pulse called DATA READY will be produced by the (1) to (0) transition of IOP4 in coincidence with ENA. The DATA READY pulse indicates that the computer has placed the requested data onto the I/O bus, and it may be accepted by the VT15. The DATA READY pulse is primarily used to strobe input data into the input buffer and, under certain circumstances, to continue main timing.

#### 3.1.2 Data Collectors

3.1.2.1 Bus Receivers - The VT15 Graphic Processor receives inputs from the computer and supplies outputs from the graphic processor to the computer via a bus receiver interface consisting of M510 Bus Receivers. The M510 has an input threshold of approximately 1.5V and supplies both the true and complemented TTL levels for a given input signal. All data and control signals received on the I/O bus are processed via these receivers. For more detailed information concerning the M510 Bus Receiver, refer to Paragraph 2.3.4 of the PDP-15 Systems Interface Manual.

3.1.2.2 Bus Drivers – Data is gated onto the computer I/O bus by a series of two-input gating structures and is enabled by either issuing the proper IOT or by a DJMS or SAVE instruction. Noninverting M622 Bus Drivers are used. 3.1.2.3 Input Buffer Register – The VT15 is a double-buffered system that maintains two levels of data registers: an active register and a holding register. The input buffer serves as a holding register and, as previously mentioned, the DATA READY pulse strobes the incoming data from the I/O bus into the input buffer. Nevertheless, the input buffer plays no active part in operation of the VT15 except during the character string instruction, in which case, the second 18-bit word is taken directly from the input buffer.

3.1.2.4 Data Buffer Register – The second level of input buffering occurs in the data buffer. The data buffer always acquires its data from the input buffer and is considered an active register. The instruction decoder operates directly from the data buffer, decoding the first three or four high-order bits of the incoming data.

#### 3.1.3 Timing and Control

The timing and control functional group processes the data acquired by the data collectors; more specifically, the data acquired by, and contained in, the data buffer register.

3.1.3.1 Main Timing – The data processing functions are controlled by main timing circuits that are operated by a basic clock, which generates pulses at a 250-ns repetition rate. Each 250-ns interval is considered one time state. In general, at least three time states, designated MS01, MS02, and MS03, are required to process instruction-word functions. Examples of main timing are shown in Figures 3-3 and 3-4. As shown in Figure 3-3, various instruction-word functions and signals are generated as follows, with respect to the various time states:

| a. Time state 1 (MS01) | Is used to increment the program counter and<br>to load the various registers located in the<br>control logic. |

|------------------------|----------------------------------------------------------------------------------------------------------------|

| b. Time state 2 (MS02) | Is used for modification of the X-position register.                                                           |

| c. Time state 3 (MS03) | Is used for modification of the Y-position register.                                                           |

The fourth time state (MS00) indicates that the particular cycle is complete. Various signals or functions such as digital-to-analog functions, save/restore, beam movements, incrementing the increment count register, enabling intensity, and repeats (REPT) usually occur during the fourth time state or time state 0 (MS00). Another term used in conjunction with beam movement time is Delta ( $\Delta$ ) Move Time (see Paragraph 1.7, c).

The main timing circuitry of the VT15, designated the main time state generator (VT15-0-07), consists of a 4-bit shift register and a 250-ns basic clock. The main time state generator can be gated on by an XFER or a RESTART-REGO condition. All display instructions, except character string, use OP DONE in conjunction with DATA AVAIL to generate an XFER (transferring the contents of the input buffer to the data buffer) and restart the timing generator.

Character string generates an OP DONE only on the completion of an entire string of ASCII characters through the detection of an escape (ESC) code (ALT MODE or CR). Another level, designated IOPS ENA is used to generate an XFER to transfer new character information from the input buffer to the data buffer and to restart the main timing generator. RESTART-REGO permits re-execution of a graphic instruction and is normally used in conjunction with the increment register.

3.1.3.2 Control and Graphic Timing – In addition to the main timing, the VT15 contains control timing and graphic timing circuitry. The control timing chain controls the display file memory reference and graphic instructions: jump, jump indirect, jump-to-subroutine, jump-to-subroutine indirect, save/restore, character input, and character string.

Basically, the JMP, JMS, or any of the indirect memory reference instructions are executed by temporarily switching the PC off the address lines, putting the address portion of the instruction, con-tained in the data buffer, onto the address lines and generating another request.

The graphic timing chain is primarily concerned with loading the "magnitude of delta" into the X and Y registers, receiving the "move in progress" (MIP) signal from the analog-function generator (AFG) and processing the proper OP DONE or RESTART-REGO signal(s) when the vector is completed.

3.1.4 Instruction Register and Logic

3.1.4.1 Parameter and Skip Registers – The parameter instruction is further divided into three subinstructions as described in Paragraph 4.5.1. The instruction operating code is decoded in coincidence with a timing pulse (START CYCLE), which is derived from the main timing generator. Certain parameter registers can also be set through the display file RESTORE instruction or from certain IOTs.

The skip instruction is divided into two subinstructions as described in Paragraph 4.5.1. The instruction operating code, in coincidence with a START CYCLE pulse derived from the main timing generator, tests the specified skip conditions. With a skip condition, a display skip (DSPLY SKP) will be generated, and the VT15 program counter will be incremented.

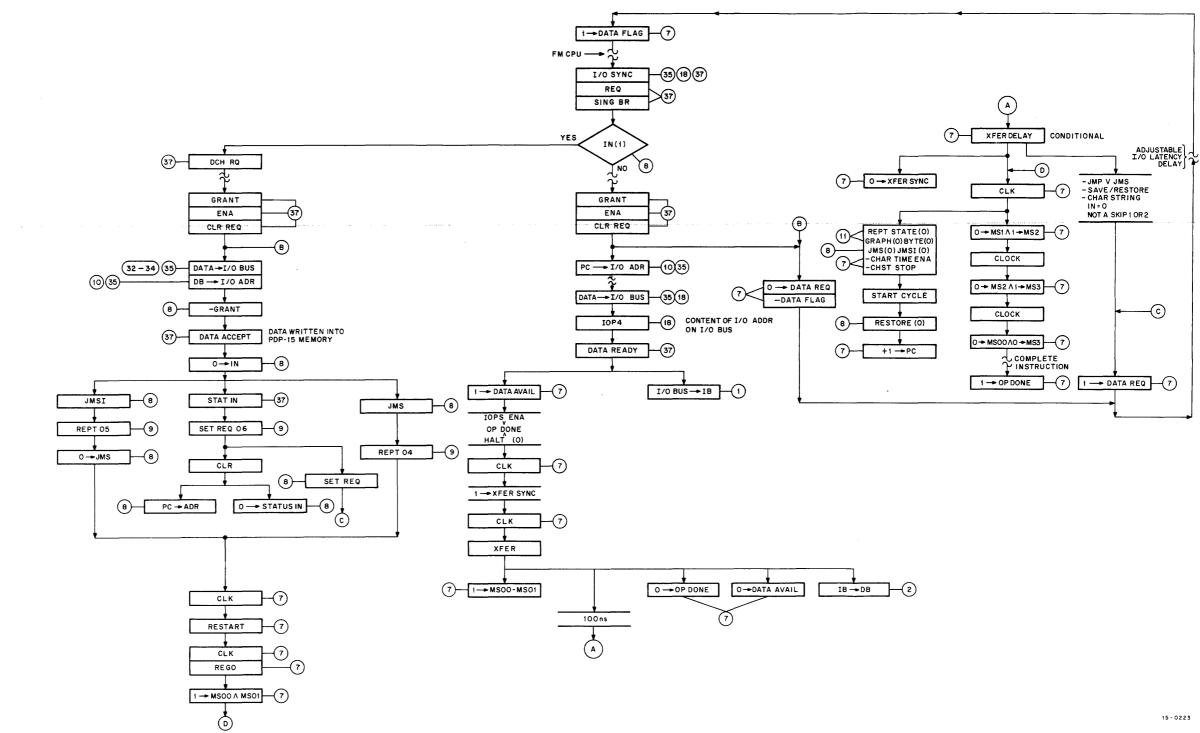

## Figure 3–3 VT15 Main Timing Flow Diagram

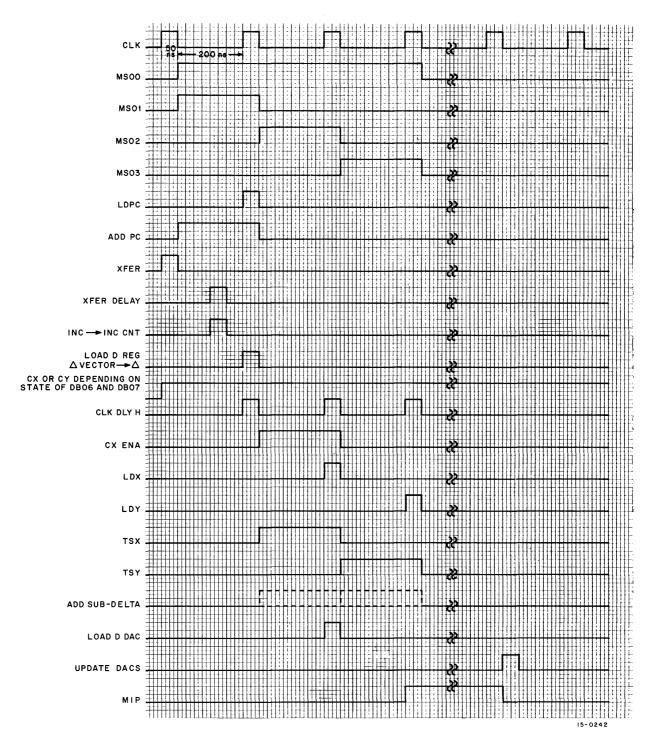

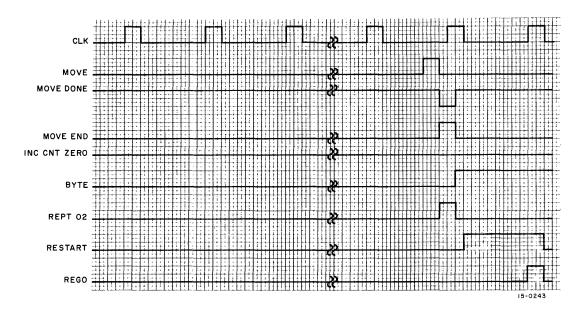

Figure 3-4 VT15 Main Timing Diagram (Sheet 1 of 2)

Figure 3-4 VT15 Main Timing Diagram (Sheet 2 of 2)

3.1.4.2 Direction and Rotate Logic - The direction parameter may be specified by bits 5 through 7 of the basic vector instruction, and bits 5 through 7 and 12 through 14 of the basic short vector instruction. The vector, graph plot, and character instructions enable a section of the direction and rotate logic (drawings VT15-0-25 and -26) that is used for decoding beam direction data for subsequent movement. In addition to the decoding bits, the logic also processes an interchange of direction data and adder gated enable time states to allow 90° counterclockwise rotation of basic vectors and characters, when specified. This feature is enabled through bits 12 and 13 of the parameter 2 instruction (Figure 4-22).

3.1.4.3 Increment Register – The increment register or counter is a four-bit register that is loaded from bits 14 through 17 of the parameter 1 instruction (see Figure 4-20) and is used for scaling. The increment register is used in conjunction with the graph plot instruction (see Figure 4-32) to specify beam displacement for the unspecified axis, described in Paragraph 4.5.4.2, d.

3.1.4.4 Intensity – Eight levels of intensity, INTO through INT7, can be specified by bits 8 through 10 of the parameter 1 instruction (see Figure 4–20) and refer to Paragraph 4.5.1.1. Bit 4 is used as the intensity enabling (INT ENA) bit in all of the above-mentioned instructions. With the desired 3-bit intensity word (level) specified through the parameter 1 instruction, the 3-bit intensity register is loaded with the 3-bit field, setting the intensity level for all intensified points, vectors, and characters generated thereafter. If a different intensity level is desired to emphasize a particular point, vector, or character, the new intensity level must be specified through the parameter 1 instruction.

3.1.4.5 Status – Six read IOTs are used to check the contents and/or condition of various flags, parameter registers, program counter (PC), and X- and Y-axis position registers.

Various parameters can also be collected by issuing a display file save/restore instruction (see Figure 4-37). When the various parameters have been assembled into the save/restore status format and stored in the computer core memory, the content can be examined easily by issuing a load accumulator (LAC) instruction that examines the status word.

3.1.4.6 Adder Gating – The adders to the main registers are gated by AND/OR gate circuits (VT15-0-19 through -24). The gating provides an addition or subtraction capability, through 2's complement, of up to a 10-bit word (number) that is gated into the X- and/or Y-registers. A given 12-bit number can be transferred into the PC, X- or Y-registers directly from the data buffer. The program counter can be set by an IOT. Provision is also made to increment the program by 1 (+1→PC). A gate is provided to give a "carry insert" into the least significant adder for both incrementing the PC and for the 2's complement subtract operation.

#### 3.1.5 Main Registers

The major registers contained in the VT15 Graphic Processor are the program counter, the X-axis position register, the Y-axis position register, and the  $\Delta$  register.

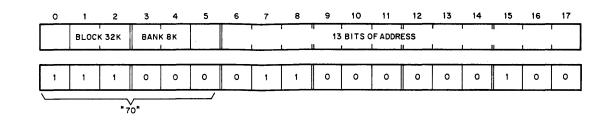

3.1.5.1 PC, X- and Y-Registers - Three M215 Modules, each module containing a 4-bit section of the PC, X- and Y-registers, combine to form the 12-bit X- and Y-registers. The 10 least significant bits from the position registers are applied to the position (X- and Y-) DACs. The three M215 Modules also handle the 12 low-order bits (bits 6 through 17) of the PC. A separate five-bit register is used to handle the remaining PC high-order bits.