# User Hardware Handbook — Computer CENTRAL PROCESSOR UNIT INSTRUCTION SET

The information presented herein is, to the best of our knowledge, true and accurate. No warranty or guarantee, expressed or implied, is made regarding the accuracy of information supplied or capacity, performance or suitability of any product or service since the manner of use is beyond our control.

You are advised that you should ensure that the information contained herein has not been superseded.

All our products, materials and services are sold subject to our Conditions of Sale, available on request.

GEC COMPUTERS LIMITED

Elstree Way, Borehamwood, Hertfordshire.

Telephone No. 01-953-2030

Holding Company - the General Electric Company Limited of England

#### **CPU INSTRUCTION SET**

# CONTENTS

|     |              |                     |          |       |      |          | • 4   |     |     | ٠.    |     |     | Page |

|-----|--------------|---------------------|----------|-------|------|----------|-------|-----|-----|-------|-----|-----|------|

| 1.  | INTRO        | DDUCTION            |          |       | 112  |          |       |     |     |       |     |     |      |

|     |              |                     |          |       |      |          |       |     |     |       |     |     |      |

|     | 1.1          | Notation Used       | •••      | •••   | •••  | •••      | •••   | ••• | *** | •••   | *** | *** | 1    |

|     |              |                     |          |       |      |          |       |     |     |       |     |     |      |

| 2.  | PROG         | RAM ACCESSIBLE RE   | CISTE    | 20    |      | ā        |       |     |     |       |     | 88  | 2    |

| ۷.  | rnod         | NAM ACCESSIBLE NE   | .0101 E1 | 10    | •••  | •••      | •••   | ••• | ••• | •••   | ••• | ••• | 2    |

|     |              |                     |          |       |      |          |       |     | *c  |       |     |     |      |

| 3.  | <b>O</b> PER | ANDS                |          |       |      |          |       |     |     |       |     |     |      |

|     | 3.1          | Operand Lengths     |          |       | * *  | •        |       |     |     |       |     |     | 3    |

|     | 3.1          | Operand Lengths     | •••      | •••   | ***  | •••      | •••   |     | ••• | •••   | ••• | ••• | 3    |

|     | 3.2          | Operand Addresses   |          | •••   | •••  | •••      |       |     | ••• | •••   | ••• | × * | 3    |

|     |              |                     |          | 47    |      |          |       |     |     |       |     |     |      |

| 4.  | INCTE        | NOTION FORMATO      |          |       |      | T):<br>P |       |     |     |       |     |     |      |

| 4.  | INSIF        | RUCTION FORMATS     |          |       | 1 14 | 10       |       |     | •   |       |     |     |      |

|     | 4.1          | Format A            | •••      |       |      |          |       |     | ••• |       | ••• |     | 4    |

|     |              |                     |          |       |      |          |       |     |     |       |     |     |      |

|     | 4.2          | Format L            |          | ***   |      | •••      | •••   |     | *** | •••   | ••• |     | 8    |

|     | 4.3          | Format B            |          |       | •••  |          |       |     | 100 |       | 95  |     | 8    |

|     |              |                     |          | •••   | •••  | •••      | •••   | ••• | ••• | •••   | 0.  | -   | 7 3  |

|     | 4.4          | Format RR           | •••      | •••   | •••  | •••      | •••   | ••• | ••• | •••   | ••• | ••• | 9    |

|     |              |                     |          |       |      |          |       |     |     |       |     |     |      |

| 5.  | MODE         | S OF OPERATION      |          |       |      |          |       |     |     |       |     |     |      |

| , e |              |                     |          |       |      |          |       | •   |     |       |     |     |      |

| P1  | 5.1          | Basic Test          |          | •••   | •••  |          | •••   | ••• | ••• | •••   | ••• | ••• | 11   |

|     |              | P 11 A1 - 1         |          |       |      |          |       |     |     |       |     |     |      |

|     | 5.2          | Full Nucleus        | •••      | •••   | •••  | •••      | •••   | ••• | ••• | •••   | ••• | ••• | 11   |

|     | 5.3          | Fixed Point Mode    | •••      |       | •••  | •••      | •••   | ••• | ••• |       | *** | *** | 11   |

|     |              |                     |          | 8     |      |          |       |     | 100 |       |     |     |      |

|     | 5.4          | Floating Point Mode | *        | ***   | •••  | •••      | •••   |     |     | •••   | ••• | ••• | 11   |

|     | 5.5          | Mode Control        |          |       |      |          |       |     |     |       |     |     | 11   |

|     | 5.5          | Mode Control        | 20       | ***   |      | 18.      | • ••• | ••• | ••• | ***   |     | ••• | • •  |

|     |              |                     |          |       |      |          |       |     |     |       |     |     |      |

| 6.  | FIXE         | POINT OPERATIONS    | 3        |       |      |          |       |     |     |       |     |     |      |

| (8) | 6.1          | Number Representat  | ion      |       |      |          |       | 8   |     |       |     |     | 12   |

|     | 0.1          | Manufactuchiesentar | IOII     | , *** | •••• | •••      | 17.   | W   | *** | •••   | ••• | ••• | 12   |

|     | 6.2          | Mixed Length Operat | tion     |       | •••  | •••      | ***   | ••• | ••• | ***   |     | ,   | 12   |

|     | 8            |                     |          |       |      |          |       |     |     |       |     |     |      |

|     | 6.3          | Condition Markers   | •••      | •••   | •••  | •••      | •••   | *** | ••• | •••   | ••• | ••• | 12   |

| Wi- | 6.4          | Logical Operations  | •        | •••   |      |          |       |     |     | ~ ~ ~ | ••• | ••• | 14   |

|     | <b>.</b> .   | _03.4m. Dha.ac.a.ia |          |       |      |          |       |     |     |       |     |     | 17   |

# THE FIXED POINT INSTRUCTION SET: FORMATS A1-A5

| 7.1    | Operations on the 32 Bit Accumulator    | •••   | ••• |      |     | ••• | •••       |     | 15 |

|--------|-----------------------------------------|-------|-----|------|-----|-----|-----------|-----|----|

| 7.2    | Operations on Operands in Store         |       |     |      |     |     |           |     | 21 |

| 7.3    | Operations on the X Register            |       |     |      |     |     |           |     | 23 |

| 7.4    | Operations on Y and Z Registers         |       |     |      |     | ••• | · 1       |     | 26 |

| 7.5    | Multiple Load and Store Instructions    |       |     |      |     | ••• |           |     | 29 |

| 7.6    | Indirect Branches                       |       |     |      | ž   |     |           | ••• | 30 |

|        |                                         |       |     |      |     |     |           |     |    |

| INSTRU | JCTIONS AVAILABLE IN FORMAT B           | •••   | •   | •••  |     |     | ै.<br>••• | ••• | 32 |

|        |                                         |       |     |      |     |     |           |     |    |

| INSTRU | ICTIONS AVAILABLE IN FORMAT L           |       |     |      |     |     |           |     |    |

| 9.1    | Operations on the 32 Bit Accumulator    |       | ••• |      |     |     | •••       |     | 33 |

| 9.2    | Literal Operations on the X Register    | •••   |     |      | ••• |     |           |     | 35 |

| 9.3    | Literal Operations on the Y and Z Regis | sters |     |      |     | ••• |           |     | 38 |

| 9.4    | Condition Branch Instructions in Form   | at L  | ••• |      |     |     |           |     | 40 |

| 9.5    | Shift Instructions                      |       |     |      |     | ••• |           |     | 43 |

| 9.6    | Bit Manipulation Instructions           |       |     |      |     | *** | •         | ••• | 47 |

| 9.7    | String Manipulation                     | •••   | ••• |      | ••• |     | •••       | ••• | 50 |

| 9.8    | Miscellaneous Instructions in Format L  |       |     |      |     |     | · *       |     | 53 |

|        |                                         |       |     |      |     |     |           |     |    |

| INSTRU | ICTIONS AVAILABLE IN FORMAT R           | R     | ••• | •••  |     | ••• | ***       | *** | 56 |

|        |                                         |       |     |      |     |     |           |     |    |

| FLOATI | ING POINT OPERATION                     |       |     |      |     |     |           |     |    |

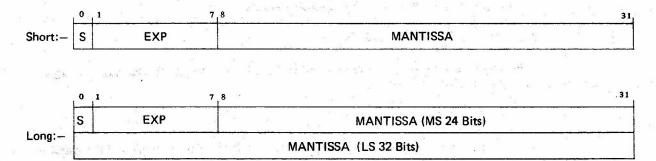

| 11.1   | Floating Point Number Representation    |       | *** |      |     |     |           |     | 61 |

| 11.2   | Floating Point Store Format             | •••   |     |      |     | *   | •••       | ••• | 61 |

| 11.3   | Floating Point Register Format          | · :   | 44. |      |     |     | - ii.     |     | 61 |

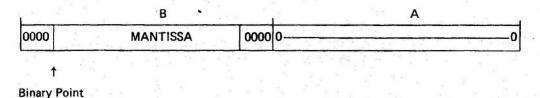

| 11.4   | Normal Representation                   |       |     |      | *** | *** |           |     | 62 |

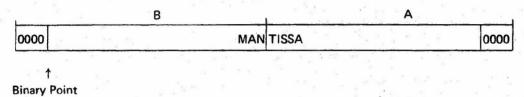

| 11.5   | Floating Point Zero                     | ×     |     |      |     | *** |           | ••• | 62 |

| 11.6   | Mixed Precision Operation               |       |     |      |     |     |           |     | 62 |

| 11.7   | Overflow and Underflow                  |       |     | •••• | ••• | ••• |           |     | 63 |

|        |                                         |       |     |      | 4.1 |     |           |     |    |

|     |       |                                 |           |        | 8   |     |     |      |     |    |

|-----|-------|---------------------------------|-----------|--------|-----|-----|-----|------|-----|----|

| 12. | THE F | LOATING POINT INSTRUCTION       | ON SET    |        |     |     |     |      |     |    |

|     | 12.1  | Normal Length Operations .      |           |        |     |     |     | •••  |     | 64 |

|     | 12.2  | Extended Operations             |           |        |     |     | ••• | •••  |     | 66 |

|     | 12.3  | Floating Point Conversion Inst  | tructions |        |     | *** | *** |      | ••• | 69 |

|     | 12.4  | Floating Point Instructions in  | Format L  | ***    |     | *** | ••• | **** | *** | 69 |

|     | Appen | dix 12A: Floating Point Arithme | itic      |        |     | ••• | ••• | •••  | ••• | 71 |

| 13. | CONT  | ROL INSTRUCTIONS AVAILA         | BLE IN BA | ASIC M | ODE | ••• |     | •••  |     | 74 |

Pag€

# SUPPLEMENT

Supplement 1: Summary of Instructions

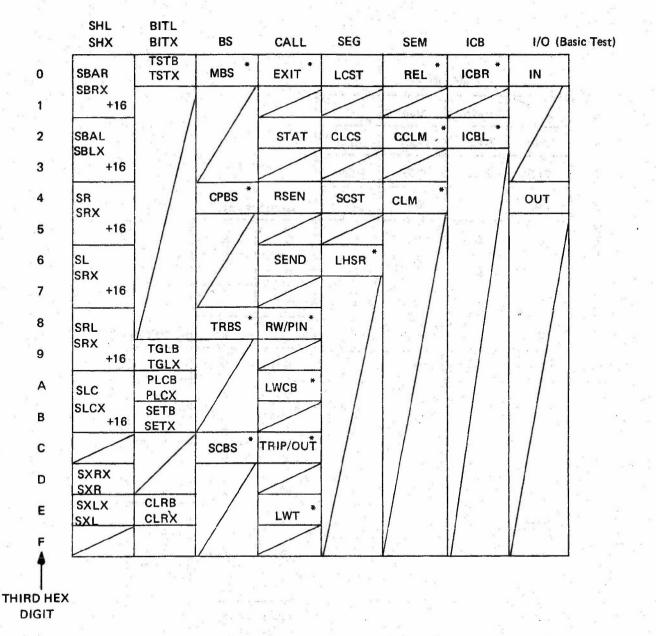

This manual describes the instruction set of the GEC 4000 Series computers, except for Nucleus instructions CALL, ICB, SEM and SEG described in detail in CPU NUCLEUS MANUAL.

Excluding the above Nucleus instructions the instruction repertoire of the computers contains some 155 different instructions. Certain of these instructions may be specified in 1 of 5 operand addressing formats.

The processor is capable of performing both integer and floating point arithmetic and instructions are provided for both modes of operation.

# 1.1 NOTATION USED

In this manual, the following notation is used to describe the instruction set.

- a denotes the content of the 32 bit Accumulator A.

- da denotes the content of the 64 bit Extended Accumulator BA.

- ha denotes the content of the least significant 16 bits of A.

- ba denotes the content of the least significant 8 bits of A.

- b denotes the content of the 32 bit Accumulator Extention B.

- x denotes the content of the 16 bit Index register X.

- y denotes the content of the 16 bit Y register.

- z denotes the content of the 16 bit Z register.

- s denotes the content of the 16 bit Sequence Register S.

- denotes the content of the 16 bit Local Workspace Register L.

- fa denotes the short floating point number in the Floating Accumulator.

- ea denotes the long floating point number in the Floating Accumulator.

- Q denotes the operand address generated by an instruction.

- wq denotes the fullword store operand of an instruction.

- hg denotes the halfword store operand of an instruction.

- bq denotes the byte store operand of an instruction.

- fq denotes the short Floating Point operand of an instruction.

- eq denotes the long Floating Point operand of an instruction.

The following program accessible registers are provided.

32 bit Accumulator, A

The accumulator is divided into two 16 bit registers AM and AL. This accumulator is used to hold the result of fixed point arithmetic and logical operations. It is also used to hold the least significant 32 bits of the mantissa in the case of long floating point operations.

32 bit Accumulator Extension, B

This register is divided into two 16 bit registers BM and BL and is used to hold remainders in integer divide instructions and the mantissa of the result in normal length floating point operations.

BM and BL may be used in conjunction with AM and AL to provide a 64 bit register and in this case the most significant register is BM and the least significant is AL. This 64 bit register is used to hold products in fixed point multiply instructions and to hold the mantissa of the result in extended-length, floating-point operations.

16 bit X Register

The X register is used as an index register to address array elements in store. It may also be used as a secondary accumulator and a comprehensive set of instructions is provided for this purpose.

16 bit Y and Z Registers

Both Y and Z registers are used to hold the base address of areas of data such as records. A restricted instruction repertoire is provided for operations on Y and Z.

16 bit L Register

This is a local workspace pointer register and holds the base address of the area of store containing the local workspace of a program. The L register is operated on by Nucleus branch instructions and by instructions using data held in other registers.

16 bit S Register

This is the sequence control register and normally contains the address of the next instruction in sequence. All instructions are 16 bit halfwords and this register is incremented by 2 for each instruction executed. The S register is operated on by branch instructions and by instructions using data held in other registers.

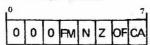

8 bit C Register

This is the control register and contains various flags that may be set by a program at any time.

These flags are referred to as 'Condition Markers' and are fully described in section 6.

The register holds condition markers as follows:-

FM - FLOATING MARKER

N - NEGATIVE CONDITION MARKER

Z - ZERO CONDITION MARKER

OF - OVERFLOW CONDITION MARKER

CA - CARRY CONDITION MARKER

## **OPERANDS**

# 3.1 OPERAND LENGTHS

Information is manipulated in multiples of eight bits. Each 8 bit unit of information is called a Byte.

Bytes may be handled separately or grouped together as follows.

# (a) Halfwords

A Halfword comprises two consecutive bytes. The low addressed byte of the item must be held at a byte address divisible by two in main store. Instructions and single precision integer operands are held as Halfwords.

## (b) Fullword

A Fullword comprises 4 consecutive bytes. The low addressed byte of the item must be held at a byte address divisible by 4 in main store. Double length integer operands and short Floating Point operands are held as Fullwords.

## (c) Double Word

A Double word comprises 8 consecutive bytes. The low addressed byte of the item must be held at a byte address divisible by 8 in main store. Long Floating Point operands are held as Double words.

# 3.2 OPERAND ADDRESSES

Each store reference instruction specifies directly or indirectly the required operand address and the type of operand i.e. Byte, Halfword, Fullword or Double Word. The operand addresses are formed as described in section 4 and the hardware ensures that an operand address of the correct form is presented to the main store at every access. i.e. If a Halfword is requested from store the least significant bit will be forced to zero. Similarly, for other store addresses:—

| TYPE OF STORE ACCESS | LEAST SIGNIFICANT<br>3 STORE ADDRESS BITS |

|----------------------|-------------------------------------------|

| Byte                 | xxx                                       |

| Halfword             | X X O                                     |

| Fullword             | X 0 0                                     |

| Double Word          | 000                                       |

#### INSTRUCTION FORMATS

Eight instruction formats are provided, known as formats A1, A2, A3, A4, A5, B, RR and L. The 16 bits of an instruction are divided into several fields which together specify the operation to be performed and where necessary the operand address.

Formats A1 to A5 are referred to as format A instructions and have a common instruction set. Each format provides a different method of forming the operand address. A separate set of instructions is available in each of the formats B, RR and L.

## 4.1 FORMAT A

Instructions specified in this format are used for arithmetic, and logical operations. Some instructions in this format may be performed in either integer mode or floating mode under control of the FM flag (section 6).

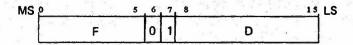

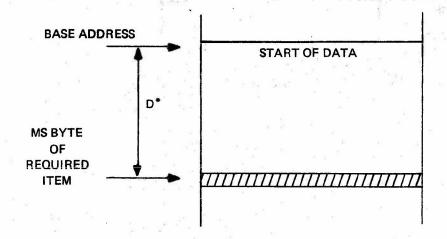

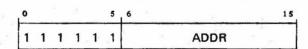

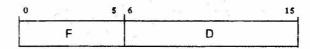

## Format A1

Of the 16 bits used to define the instruction the most significant 6 bits (0-5) are used to specify one of 64 possible instructions. The next 2 bits (6 and 7) specify the format and the final 8 bits are the displacement field that defines the address.

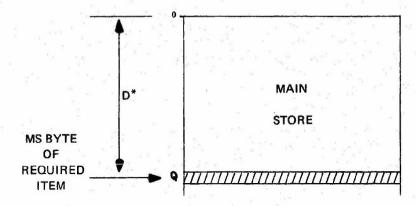

In this format the displacement is used to form the operand store address, after scaling as described below. D\* denotes the scaled displacement.

The displacement field is scaled according to operand length. If a byte operand is required no scaling takes place and the eight bits of the displacement field are able to access any of the first 256 bytes of virtual store. An instruction requiring a halfword operand may access 256 halfwords in the first 512 bytes of virtual store. Similarly 256 full words in the first 1024 bytes of virtual store or 256 double words in the first 2048 bytes of virtual store. This format is used for accessing global simple variables.

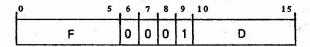

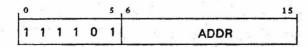

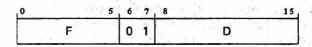

# Format A2

| 0 |   | 5 | 6 | 7 8 | 15 |

|---|---|---|---|-----|----|

|   | F |   | 1 | M   | D  |

The most significant 6 bits specify the function as in format A1. Bit 6 specifies the format whilst bits 7 and 8 (M Field) define how the D Field is to be used, to define the operand address. In this format the scaled displacement field is added to a base register specified by the M Field.

The displacement field is scaled as for format A1 and the 7 bits of this field may be used to access one of 128 items (bytes, halfwords, words, or double words) in the area defined by a base register.

Operand addresses are formed as tabulated with the value of the M field selecting base registers L, S, Y or Z.

In the following table D\* denotes the scaled displacement field.

| M | OPERAND ADDRESS |

|---|-----------------|

| 0 | I + D*          |

| 1 | s + D*          |

| 2 | y + D*          |

| 3 | z + D*          |

The L register normally holds a pointer to the local data needed in a program chapter. Mode 0 is thus used to access local simple variables.

Mode 1 is used to access constants held in the same area of store as the code for a particular program chapter. These constants must be at a higher address in store than the instruction that accesses them.

Registers Y and Z normally hold pointers to records, and therefore modes 2 and 3 are used to access general simple variables.

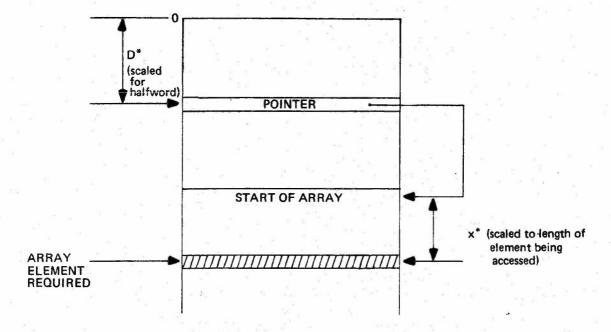

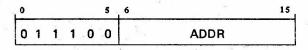

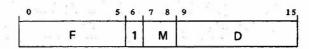

# Format A3

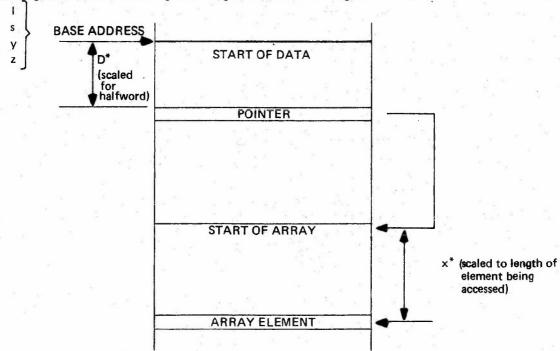

The most significant six bits are used to specify the function as in format A1. Bits 6,7,8 and 9 specify the format and the final 6 bits are the displacement field that defines the store address. In this format a halfword in store is accessed and used to form the base address of an array. This base address is then indexed to form the address of a selected array element. The index register x is scaled according to the length of the element being accessed.

This format is used to access global arrays, the 6 bits of the displacement field allowing up to 64 array pointers to be used.

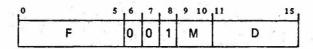

# Format A4

The most significant six bits are used to specify the function as in format A1. Bits 6,7 and 8 specify the format whilst 9 and 10 define the way in which the displacement field is to be used, to form the operand address. In this format the displacement field is always scaled for a halfword and then added to a base register specified by M. The address so formed is used to access a halfword operand from store, which forms the base address of an array. The operand is indexed with x to form the address of an individual array element. The index register x is scaled according to the length of the element being accessed.

The 5 bit displacement field may be used to access one of 32 array pointers in an area of store defined by a base register.

Operand addresses are formed as tabulated with the value of the M field selecting base registers L, S, Y or Z.

In the following table D denotes the value of the displacement field in the instruction and x\* denotes the scaled value of the x register.

| M | OPERAND ADDRESS  |

|---|------------------|

| 0 | (I + 2D) + x*    |

| 1 | $(s + 2D) + x^*$ |

| 2 | $(y + 2D) + x^*$ |

| 3 | (z+2D)+x*        |

Mode 0 is used to access local arrays of data.

Mode 1 is used to access arrays of constants that are held in the same area of store as the code for a particular program chapter, these constants being at higher store addresses than the instructions accessing them.

Modes 2 and 3 are used to access arrays of data held in records.

Format A5

| 0 |   | - 5 | 6 | 7 | 8 | 9 | 10 | 1112 | 15 |

|---|---|-----|---|---|---|---|----|------|----|

|   | F | a . | 0 | 0 | 0 | 0 | М  |      | D  |

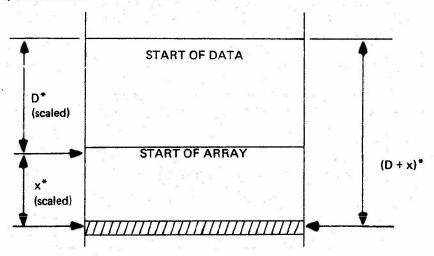

The most significant six bits are used to specify the function as in format A1. Bits 6,7,8 and 9 specify the format whilst 10 and 11 define the way in which the operand address is formed. This format is similar to the A2 format except that the scaled displacement field is added to a base register and then indexed, before forming the operand address.

The displacement field and x are scaled according to the length of the item to be accessed from store. The four bits of displacement field enable 16 items (bytes halfwords, words or doublewords) to be accessed from store in the area defined by a base register and the index register x.

Operand addresses are formed as tabulated with the value of M field selecting base registers L, Y or

In the following table D\* denotes the scaled displacement field and x\* denotes the scaled value of the x register.

| M | OPERAND ADI | DRESS |

|---|-------------|-------|

| 0 | I+D*+x*     |       |

| 1 | D* + x*     |       |

| 2 | y+D*+x*     |       |

| 3 | z + D* + x* |       |

Mode 0 is used to access local arrays of data.

Mode 1 is used to access global arrays of data.

Modes 2 and 3 are used to access arrays of data such as records and vectors.

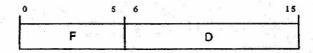

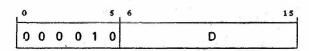

## 4.2 FORMAT L

The instructions specified in this format are literal instructions and generally do not require an operand from store.

MS LS 0 1 2 7 8 15 D

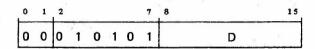

For this format the two most significant bits (0-1) are always zero. The next 6 bits (2-7) specify the function and the remaining 8 bits are used as follows:—

- (a) As an 8 bit unsigned literal operand. Any number between 0 and 255 can be represented.

- (b) Some conditional branch instructions are specified in this format and here the displacement field is treated as a signed integer, to specify a branch destination. This destination may be within 127 halfwords (i.e. instructions) forward or 128 halfwords backward relative to the next instruction in sequence.

Thus: Operand address = S ± 2D

(c) Where a literal operand is not required and the instruction is not a conditional branch, bits 8–15 are used in conjunction with the F bits to further define the instruction (e.g. shifts and control functions).

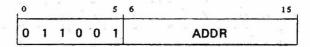

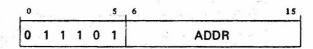

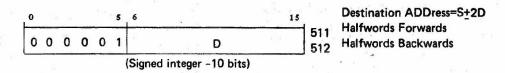

# 4.3 FORMAT B

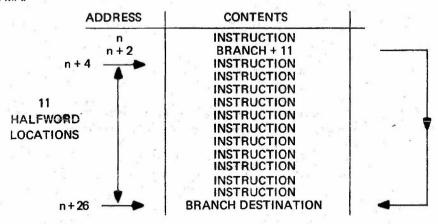

Two instructions only are specified in this format and both are unconditional branches.

The two instructions in this format are defined by the F bits, the most significant 4 bits (bits 0-3) are always zero. The remaining 10 bits are used as a signed integer to specify the branch destination. This destination address may be within 511 halfwords (i.e. instructions) forwards or 512 halfwords backwards relative to the next instruction in sequence.

Thus: Destination Address = S ± 2D

Since instructions are always 16 bit halfwords the displacement field in format B instructions is always multiplied by 2. At the start of the execution of any instruction, the sequence control register (S) always points to the next instruction in sequence. Therefore all branches are relative to the next instruction in sequence and not the current instruction.

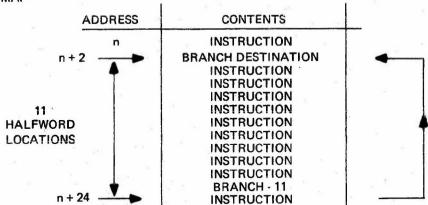

## EXAMPLE 1

#### STORE MAP

## **EXAMPLE 2**

## STORE MAP

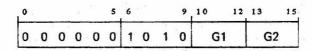

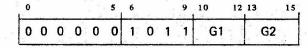

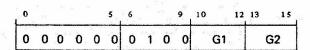

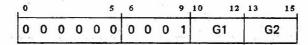

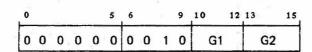

# 4.4 FORMAT RR

The instructions specified in this format are register to register instructions.

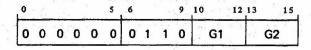

| 0 | 1 | 2 | 3 | 4 | 5 | 6 9 | 10 | 12 | 13 | 15 |

|---|---|---|---|---|---|-----|----|----|----|----|

| 0 | 0 | 0 | 0 | 0 | 0 | F   | G  | 1  | G  | 2  |

The first 6 bits (0-5) are always zero. The next 4 bits (6-9) define 16 possible instructions, which are further defined by bits 10-15.

Format RR instructions are used for operations between registers. The two registers taking part in an operation are defined by G1 and G2. G1 specifies the destination register and G2 specifies the source register as follows:—

| G1,G2 | REGISTER      |

|-------|---------------|

| 0     | 0 (see below) |

| 1     | A (32 bits)   |

| 2     | B (32 bits)   |

| 3     | X (16 bits)   |

| 4     | L (16 bits)   |

| 5     | S (16 bits)   |

| 6     | Y (16 bits)   |

| 7     | Z (16 bits)   |

Register 0 is a non-existent dummy register. If used as a source it appears to contain zero; if used as a destination the result is lost but the condition markers record the result of the operation.

# MODES OF OPERATION

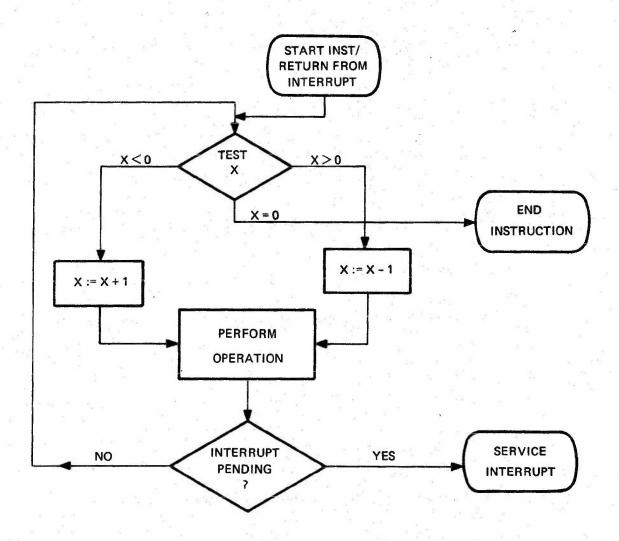

The CPU has two different modes of operation, basic test and full nucleus. Within these two modes of operation, two further modes are provided, integer mode and floating point mode.

# 5.1 BASIC TEST

5.

This mode of operation is provided in order to more easily test the central processor basic instruction set. Most of the microprogram controlling the nucleus is disenabled and the computer becomes a machine capable of running only 2 programs simultaneously. One is the normal operating program, the other being entered on receipt of an interrupt as described in section 13. All addresses are 16 bit absolute addresses and thus 64kBytes of store may be accessed. Certain additional instructions are provided in this mode to facilitate input/output and interrupt handling. These instructions are described in section 13.

Should these instructions be specified when the machine is in full nucleus mode they are treated as undefined instructions (refer to CPU Nucleus Manual).

Further modifications to the functioning of the CPU are:

- (1) The action taken when an Input Output Processor or Error interrupt occurs (refer to section 13).

- (2) The action taken as a result of depressing certain switches on the front panel (IPL1, IPL2, START/ STOP). This is described in CPU Controls and Monitor Unit Manual.

- (3) The 'TRIG C.P.' facility becomes available enabling a program to be restarted at a selected point (see CPU Controls and Monitor Unit Manual).

## 5.2 FULL NUCLEUS

In this mode, addresses generated by the program are 16 bit virtual addresses and are mapped into absolute addresses by the mechanism described in the CPU Nucleus Manual. Control instructions in this mode are:

CALL. SEMAPHORE INTER-CHAPTER BRANCH and SEGMENT and these are fully described in the CPU Nucleus man

# 5.3 FIXED POINT MODE

In this mode of operation the fixed point instruction set described in sections 7-10 is provided.

## 5.4 FLOATING POINT MODE

In this mode of operation certain instructions are treated as floating point instructions as described in section 11.

## 5.5 MODE CONTROL

The modes of operation described in 5.1 and 5.2 above are controlled by a switch on the CMU front panel (see CMU Document) and under certain conditions by the SFN instruction (see section 9).

The modes of operation described in 5.3 and 5.4 are controlled by the FM flag in the control register which can be manipulated by the program as described in section 6.

The fixed point instruction set performs binary arithmetic on operands serving as addresses and index quantities as well as fixed point data. Operands may be 16 bits or 32 bits long and may be held in one of the program accessible registers or in the main store. Both operands are signed 16 or 32 bits long, negative quantities being held in two's complement form. Condition markers are set as a result of most arithmetic and logical operations. Addresses are sometimes treated as positive 16 bit integers.

## 6.1 NUMBER REPRESENTATION

Fixed point operands are treated as 16 or 32 bit signed binary integers.

Positive integers in the range  $0:2^{15}-1$  (16 bit) or  $2^{31}-1$  (32 bit) are represented directly. The most significant bit of an operand representing a positive integer will therefore be zero.

Negative integers in the range  $-2^{15}$ : -1 (16 bit) or  $-2^{31}$ : -1 (32 bit) are represented by subtracting the magnitude of the number from  $2^{16}$  (16 bit) or  $2^{32}$  (32 bit). The most significant bit of a negative operand will therefore be a one.

Since the most significant operand bit can be used to distinguish the sign of an operand, it is referred to as the sign bit. This representation is known as 2s complement notation. The range of numbers which can be represented is therefore

$$-2^{15} \le N \le 2^{15} - 1$$

(halfword operands)

or  $-2^{31} \le N \le 2^{31} - 1$  (fullword operands)

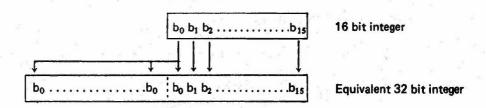

# 6.2 MIXED LENGTH OPERATIONS

A 16 bit 2s complement integer can be converted into the equivalent 32 bit representation as follows:—the least significant 16 bits of the 32 bit integer are the same as the original 16 bit integer, and the sign bit of the 16 bit integer is replicated throughout the most significant 16 bits of the 32 bit integer.

This process is referred to as 'sign extending'. It is therefore possible to perform operations between 32 bit and 16 bit integers provided 16 bit operands are sign extended to 32 bits before the operation is performed.

# 6.3 CONDITION MARKERS

There are four condition markers N, Z, OF and CA which are used to record information about an operation. This information may subsequently be tested with a conditional branch instruction, in considering the information conveyed by these markers it is necessary to distinguish between two results that an operation may produce. The first is the TRUE result, obtained by applying the rules of binary arithmetic to the operation, the second is the APPARENT result obtained by taking the least significant n bits of the true result, where n is the number of bits available for recording the result.

The meanings of the condition markers are as follows:-

The Negative Condition Marker (N)

This is a single bit set to the sign of the true result of the last operation performed. Thus, it is set to a logical 1 if the true result is negative and to a logical 0 if the true result is positive.

# The Zero Condition Marker (Z)

This is a single bit set to a logical 1 if the apparent result of the last operation performed is zero, and is reset to logical 0 if the apparent result of the last operation performed is non-zero.

The Overflow Condition Marker (OF)

This is a single bit set to a logical 1 if an operation produced overflow since the flag was last reset i.e. the apparent result is different from the true result. This flag is reset by obeying the instruction 'Branch on Overflow'.

The Carry Condition Marker (CA)

This is a single bit which, following an add operation is set to logic 1 if the operation produced a carry out of the most significant bit position, and is otherwise reset to 0, and following a subtract operation is set to logic 1 if the operation produced a borrow out of the most significant bit position, and is otherwise reset to zero.

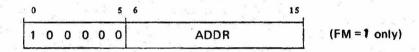

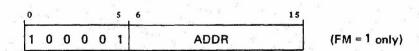

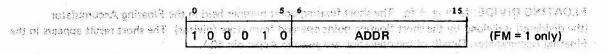

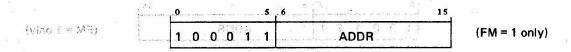

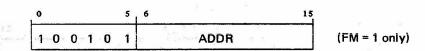

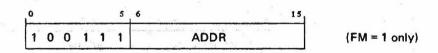

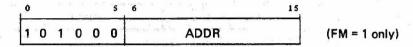

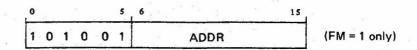

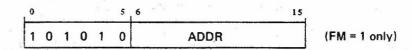

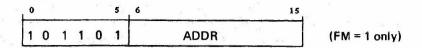

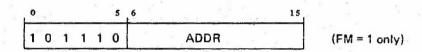

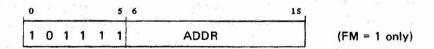

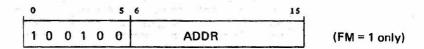

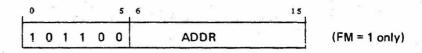

# Floating Marker

This is a single bit that controls the floating point feature of the computer. When this flag is reset to a logical 0 certain instructions operating on the accumulator are interpreted as Integer Operations. When this flag is set to a logical 1 these instructions are interpreted as Floating Point Operations and a small set of additional instructions are made available.

The flag may be set or cleared by control instructions in format L (see section 9) or by use of the Load Multiple Instruction. A further way to clear the FM flag is by use of one variant of the Call instruction (described in CPU Nucleus Manual).

During input/output these flags are used for special purposes.

Examples of negative, zero and overflow and carry conditions are given below assuming eight bits are available to hold the result of the calculation. The carry out bit is also shown, in parentheses:—

## Addition

| (a) | +57<br>+35 | =        | 00111001<br>00100011 |   | Negative reset Zero reset                              |

|-----|------------|----------|----------------------|---|--------------------------------------------------------|

|     | +92        | <u> </u> | (0)01011100          | } | Overflow not set Carry reset                           |

| (b) | +57<br>-35 | =        | 00111001<br>11011101 |   | Negative reset Zero reset                              |

|     | +22        | =        | (1)00010110          | } | Overflow not set Carry set                             |

| (c) | -57<br>-92 | =        | 11000111<br>10100100 | } | Negative set Zero reset                                |

|     | - 149      | =        | (1)01101011          | J | Overflow set (Out of range, Result < -128).  Carry set |

| (d) | +57<br>+92 | =        | 00111001<br>01011100 |   | Negative reset. Zero reset                             |

|     | +149       | =        | (0)10010101          |   | Overflow set (neg,result) Carry reset                  |

# Multiplication (Carry Not Affected)

| (a) | +35  | = | 00100011    | Negative reset   |

|-----|------|---|-------------|------------------|

|     | +3   | = | 00000011    | Zero reset       |

|     | +105 | = | 01101001    | Overflow not set |

| (b) | +35  | = | 00100011    | Negative set     |

|     | 3    | = | 11111101    | Zero reset       |

|     | -105 | = | 10010111    | Overflow not set |

| (c) | +35  | = | 00100011    | Negative reset   |

|     | + 4  | = | 00000100    | Zero reset       |

|     | +140 | = | 10001100    | Overflow set     |

| (d) | +32  | = | 00100000    | ) Negative reset |

| (-, | +16  | = | 00010000    | Zero set         |

|     | +512 | = | 10 00000000 | Overflow set     |

|     |      |   |             |                  |

# 6.4 LOGICAL OPERATIONS

The condition markers are used in the same way as for integer arithmetic operations, except that carry and overflow stats are unaffected by logical operations.

# 7. THE FIXED POINT INSTRUCTION SET: FORMATS A1-A5

The following describes the basic fixed point instruction set of the computer, i.e. those instructions provided when FM is set to logic 0. The Floating point instructions in section 12 are not available.

# 7.1 OPERATIONS ON THE 32 BIT ACCUMULATOR

The following instructions are available: -

LDB - LOAD BYTE

LD - LOAD HALFWORD

LDW - LOAD WORD

STB - STORE BYTE

ST - STORE HALFWORD

STW - STORE WORD

AD - ADD HALFWORD

ADW - ADD WORD

SB - SUBTRACT HALFWORD

SBW - SUBTRACT WORD

CPB - COMPARE BYTE

CP - COMPARE HALFWORD

CPW - COMPARE WORD

N - AND HALFWORD

NW - AND WORD

M - MULTIPLY HALFWORD

MW - MULTIPLY WORD

D - DIVIDE HALFWORD

DW - DIVIDE WORD

LDB

LOAD BYTE: a := bq. The byte is loaded into the A register from store and is extended to 32 bits by most significant zeros before the operation. This instruction therefore loads the least significant byte of the accumulator and clears the most significant 24 bits. The final value in A will lie in the range 0 to 255.

## Condition Markers

N - is cleared by the instruction

Z - is set if the 32 Bit accumulator is zero otherwise it is cleared

CA – not affected OF – not affected

LD

LOAD: a := hq. The halfword operand is loaded from store and is sign extended to 32 bits before the operation. The instruction therefore loads the least significant 16 bits  $(A_L)$  of the accumulator with the operand and loads the most significant 16 bits  $(A_M)$  with the operand extension.

## **Condition Markers**

N - is set to the sign of the 32 bit accumulator after the load

Z - is set if the accumulator is zero after the operation otherwise it is cleared

CA – not affected OF – not affected

LDW

LOAD WORD: a := wg. The 32 bit operand is loaded from store.

#### **Condition Markers**

N - is set to the sign of the 32 bit accumulator after the load

Z - is set if the accumulator is zero after the operation otherwise it is cleared

CA – not affected OF – not affected

**STB**

STORE BYTE: bq := ba. The least significant byte of the 32 bit accumulator is stored.

# **Condition Markers**

N - is cleared by the instruction

Z - is set if the byte to be stored is zero otherwise it is cleared

CA - not affected OF - not affected

ST

STORE: hq:=ha. The least significant 16 bits of the accumulator (A<sub>1</sub>) are stored.

## Condition Markers

N - is set to the most significant bit of the halfword stored

Z - is set if the halfword stored is zero otherwise it is cleared

CA - not affected

OF - is set if the 16 bit halfword stored is not equal in value to the original 32 bit

content of A.

STORE WORD: Wq := a. The 32 bit accumulator ( $A_M$  and  $A_L$ ) is stored.

## **Condition Markers**

N - is set to the sign of the 32 bit accumulator

Z - is set if the 32 bit accumulator is zero otherwise it is cleared

CA – not affected OF – not affected

AD

ADD: a := a + hq. The halfword operand from store is sign extended to 32 bits before being added to the contents of the accumulator. Arithmetic is performed over 32 bits.

# **Condition Markers**

N - is set if the true result is negative

Z - is set if the result in the 32 bit accumulator is zero, otherwise it is cleared

CA - is set if there is a carry out of the most significant bit of the 32 bit accumulator

otherwise it is cleared

OF - is set if arithmetic overflow occurs otherwise it remains unchanged.

SB

SUBTRACT: a := a - hq. The halfword operand from store is sign extended to 32 bits before being subtracted from the contents of the accumulator. Arithmetic is performed over 32 bits.

# **Condition Markers**

N - is set if the true result is negative

Z - is set if the result in the 32 bit accumulator is zero, otherwise it is cleared

CA – is set if there is a borrowout of the most significant bit of the 32 bit accumulator

otherwise it is cleared.

OF - is set if arithmetic overflow occurs otherwise it remains unchanged.

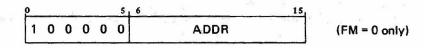

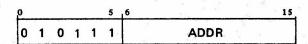

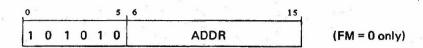

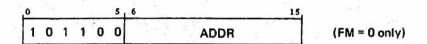

| 0 |   |   |   |   | 5 | 6   | 15   |               |

|---|---|---|---|---|---|-----|------|---------------|

| 1 | 0 | 1 | 0 | 0 | 1 | , X | ADDR | (FM = 0 only) |

ADD WORD: a := a + wq. The 32 bit operand from store is added to to contents of the 32 bit accumulator.

## Condition Markers

N - is set if the true result is negative

Z - is set if the result in the 32 bit accumulator is zero, otherwise it is cleared

CA - is set if there is a carry out of the most significant bit of the 32 bit accumulator otherwise it is cleared.

OF - is set if arithmetic overflow occurs otherwise it remains unchanged.

SBW

SUBTRACT WORD: a := a - wq. The 32 bit operand from store is subtracted from the contents of the 32 bit accumulator.

# Condition Markers

N - is set if the true result is negative

Z - is set if the result in the 32 bit accumulator is zero, otherwise it is cleared

CA — is set if there is a borrow out of the most significant bit of the 32 bit accumulator

is set if arithmetic overflow occurs otherwise it remains unchanged.

otherwise it is cleared

**CPB**

COMPARE BYTE: form ba - bq. The byte from store is extended to 32 bits by most significant zeros before being compared with the contents of the 32 bit accumulator. The contents of the accumulator are unaffected by this instruction.

# Condition Markers

N - is set if the 32 bit accumulator is less than the zero extended byte from store, otherwise it is cleared.

Z - is set if the 32 bit accumulator is equal to the zero extended byte from store, otherwise it is cleared.

CA - not affected

OF - not affected

COMPARE: form a - hq. The halfword operand from store is sign extended to 32 bits before being compared with the contents of the 32 bit accumulator. The contents of the accumulator are unaffected by this instruction.

## Condition Markers

N - is set if the 32 bit accumulator is less than the sign extended halfword operand from store, otherwise it is cleared.

Z - is set if the 32 bit accumulator equals the sign extended operand from store, otherwise it is cleared.

CA - is set if there is a borrow out of the most significant bit of the function unit as a result of the comparison otherwise it is cleared.

OF - is set if arithmetic overflow occurs otherwise it remains unchanged.

**CPW**

COMPARE WORD: form a - wq. A 32 bit operand from store is compared with the contents of the 32 bit accumulator.

# **Condition Markers**

N - is set if the 32 bit accumulator is less than the 32 bit operand from store.

Z - is set if the 32 bit accumulator is equal to the 32 bit operand from store, otherwise it is cleared.

CA - is set if there is aborrow out of the most significant bit of the function unit as a result of the comparison otherwise it is cleared.

OF - is set if arithmetic overflow occurs otherwise it remains unchanged.

N

AND: a := a  $\land$  hq. The halfword operand from store is sign extended to 32 bits before being used to form the logical AND function with the contents of 32 bit accumulator. The result is placed in the accumulator.

## Condition Markers

N - is set to the sign of the 32 bit accumulator after the operation.

Z - is set if the 32 bit accumulator is zero after the operation, otherwise it is cleared.

CA - not affected.

OF - not affected.

AND WORD: a :=  $a \land wq$ . The 32 bit operand from store is used to perform the logical AND function with the contents of the 32 bit accumulator. The result is placed in the accumulator.

## Condition Markers

N - is set to the sign of the 32 bit accumulator after the operation.

Z - is set if the 32 bit accumulator is zero after the operation, otherwise it is cleared.

CA – not affected. OF – not affected.

M

MULTIPLY: a := a \* hq. The halfword operand from store (Multiplier) and the contents of the 32 bit accumulator (multiplicand) are multiplied together to form a 48 bit product. The result (in the accumulator) is the least significant 32 bits of the true product.

## Condition Markers

N - is set if the true product in A is negative.

Z - is set if the least significant 32 bits (i.e. the result in the accumulator) is zero, otherwise it is cleared.

CA - not affected.

OF - is set if significant bits are lost by truncating the product from 48 to 32 bits.

MW

MULTIPLY WORD: da := a \* wq. The 32 bit operand from store (Multiplier) and the contents of the 32 bit accumulator (multiplicand) are multiplied together to form a 64 bit product. The result is held in the 64 bit extended accumulator (BA) with the most significant bits in B and the least significant 32 bits in A.

## Condition Markers

N - is set if the true result in A is negative.

Z - is set if the result in BA is zero, otherwise it is cleared.

CA - not affected.

OF - cannot occur since the result in BA is the true 64 bit integer product.

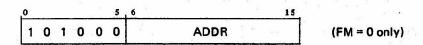

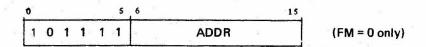

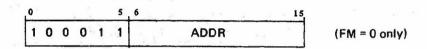

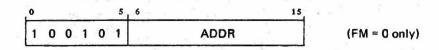

| 0 |   | 1 | ٩ | - 3 | 5 | 6   | 17 FE 2 | 15 |               |

|---|---|---|---|-----|---|-----|---------|----|---------------|

| 1 | 0 | 0 | 1 | 1   | 0 | 187 | ADDR    |    | (FM = 0 only) |

DIVIDE: a:= a ÷ hq b := remainder. The contents of the 32 bit accumulator (dividend) are divided by a halfword from store (divisor) and the result in the accumulator is the 32 bit integer quotient. The 32 bit remainder is held in B. The sign of the remainder is always equal to the sign of the dividend.

## For example:-

| DIVIDEND | DIVISOR | QUOTIENT | REMAINDER |

|----------|---------|----------|-----------|

| +5       | +2      | +2       | +1        |

| -5       | +2      | -2       | -1        |

| +5       | -2      | -2       | +1        |

| -5       | -2      | +2       | -1        |

## Condition Markers

N - is set if the quotient in A is negative.

Z - is set if the 32 bit result is zero, otherwise it is cleared.

CA - not affected

OF - is set if the divisor is zero or if the divisor is -1 and the dividend is 231.

Under these circumstances A, B, N and Z are undefined.

DW

DIVIDE WORD:  $a := da \div wq \ b :=$  remainder. The contents of the 64 bit extended accumulator BA (dividend) are divided by the 32 bit operand from store (divisor). The result, in the accumulator, is the least significant 32 bits of the quotient and the 32 bit remainder is held in B. As in DIVIDE the sign of the remainder is always equal to the sign of the dividend.

## Condition Markers

N - is set if the quotient in A is negative.

Z - is set if the 32 bit accumulator is zero otherwise it is cleared

CA - not affected

OF - is set if the quotient is out of range i.e. if more than 32 bits are required to hold the resulting quotient. An example is all numbers greater than 2<sup>31</sup> divided by +1. If overflow occurs A, B, N and Z are undefined.

## 7.2 OPERATIONS ON OPERANDS IN STORE

The following instructions are available:-

NBS - AND BYTE IN STORE

OBS - OR BYTE IN STORE

XBS - EXCLUSIVE OR BYTE IN STORE

DECS - DECREMENT STORE INCS - INCREMENT STORE

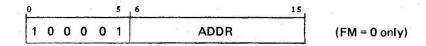

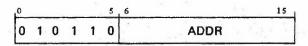

| 0   | 5 |   |   |   | 6 | 10   | 15 |  |  |

|-----|---|---|---|---|---|------|----|--|--|

| 0 1 | 0 | 1 | 0 | 0 |   | ADDR | #2 |  |  |

AND BYTE IN STORE: bq:= bq  $\land$  ba. A byte operand from store is used to perform the logical AND function with the least significant byte of the accumulator (i.e. bits 8–15 of A<sub>L</sub>). The result is returned to store and the accumulator is unchanged.

# **Condition Markers**

N - is cleared by the instruction.

Z - is set if the result of the operation (that is returned to store) is zero,

otherwise it is cleared.

CA - not affected.

OF - not affected.

OBS

OR BYTE IN STORE: bq := bq V ba. A byte operand from store is used to perform the logical OR function with the least significant byte of the accumulator (i.e. bits 8-15 of A<sub>L</sub>). The result is returned to store and the accumulator is unchanged.

## Condition Markers

N - is cleared by the instruction.

Z - is set if the result of the operation (that is returned to store) is zero,

otherwise it is cleared.

CA - not affected.

OF - not affected.

XBS

EXCLUSIVE OR BYTE IN STORE: bq := bq  $\neq$  ba. A byte operand from store is used to perform the logical EXCLUSIVE OR function with the least significant byte of the accumulator (i.e. bits 8–15 of A<sub>L</sub>). The result is returned to store and the accumulator is unchanged.

## **Condition Markers**

N - is cleared by the instruction

Z - is set if the result of the operation (that is returned to store) is zero,

otherwise it is cleared.

CA - not affected.

OF - not affected.

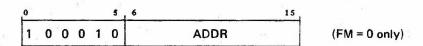

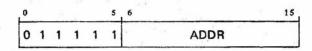

| 0 |   | 5 | Yes 1 |   | 5 | 6       | t the state of | 15 |

|---|---|---|-------|---|---|---------|----------------|----|

| 0 | 1 | 0 | 0     | 1 | 0 | (a) (a) | ADDR           |    |

DECREMENT STORE: hq := hq -1. The halfword operand from store is decremented by 1 and returned to the store. None of the registers in the central processor are affected.

## **Condition Markers**

N - is set to the true sign of the decremented operand

Z - is set if the decremented operand is zero, otherwise it is cleared.

CA - is set if the subtraction causes a borrow out of the most significant bit of

the halfword operand.

OF - is set if the subtraction causes arithmetic overflow.

**INCS**

INCREMENT STORE: hq := hq + 1. The halfword operand from store is incremented by 1 and returned to the store. None of the registers in the central processor are affected.

## Condition Markers

N - is set to the true sign of the incremented operand.

Z - is set if the incremented operand is zero, otherwise it is cleared.

CA - is set if the addition causes a carry out of the most significant bit of

the halfword operand.

OF - is set if the addition causes arithmetic overflow.

# 7.3 OPERATIONS ON THE X REGISTER

The following instructions are provided:-

LDX - LOAD X REGISTER

LBX - LOAD BYTE TO X REGISTER

STX - STORE X REGISTER

ADX - ADD X REGISTER

SBX - SUBTRACT X REGISTER

MX – MULTIPLY X REGISTER

DX – DIVIDE X REGISTER

NX - AND X REGISTER

CPX - COMPARE X REGISTER

LDX

## Condition Markers

N - is set to the sign of the 16 bit X register after the operation.

Z - is set if X is zero after the operation otherwise it is cleared.

CA - not affected.

OF - not affected.

## LBX

LOAD BYTE TO X REGISTER: x := bq. A byte operand from store is loaded into the least significant byte of the X register. The operand byte is expanded to 16 bits by most significant zeros before being loaded into the X register.

## **Condition Markers**

N - is cleared by the instruction.

Z - is set if the X register is zero after the operation, otherwise it is cleared.

CA - not affected.

OF - not affected.

# STX

STORE X REGISTER: hq := x. The 16 bit register is stored at a halfword address.

## Condition Markers

N - is set to the sign of the stored operand.

Z - is set if the stored operand is zero, otherwise it is cleared.

CA - not affected.

OF - not affected.

# ADX

ADD TO X REGISTER: x := x + hq. The halfword operand from store is added to the contents of the 16 bit X register.

#### Condition Markers

N - is set to the true sign of the X register after the operation.

Z - is set if the X register is zero after the operation otherwise it is cleared.

CA - is set if there is a carry out of the most significant bit of the X register,

otherwise it is cleared.

OF - is set if arithmetic overflow occurs due to the operation on X.

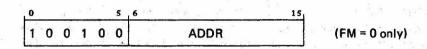

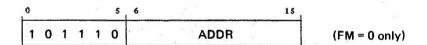

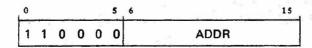

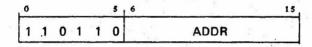

| Ò |   | 11 | n 1 | i. | 5 | 15   |

|---|---|----|-----|----|---|------|

| 1 | 1 | 0  | 0   | 1  | 0 | ADDR |

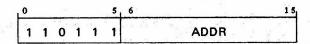

SUBTRACT FROM X REGISTER: x := x - hq. The halfword operand from store is subtracted from the contents of the 16 bit X register.

## **Condition Markers**

N - is set to the true sign of the X register after the operation.

Z - is set if the X register is zero after the operation, otherwise it is cleared.

CA - is set if there is a borrow out of the most significant bit of the X register,

otherwise it is cleared.

OF - is set if arithmetic overflow occurs due to the operation on X.

**CPX**

COMPARE X REGISTER: form x - hq. The halfword operand from store is compared with the contents of the 16 bit X register. The X register is unaffected by this instruction.

## Condition Markers

N - is set if the X register is less than the 16 bit operand from store

Z - is set if the 16 bit operand from store is equal to the X register, otherwise it is cleared.

CA - is set if there is aborrow out of the most significant bit of the function unit as a result of the comparison, otherwise it is cleared.

OF - is set if arithmetic overflow occurs as a result of the comparison.

NX

AND X REGISTER:  $x := x \land hq$ . The halfword operand from store is used to form the logical AND function with the contents of the X register. The result is replaced in the X register.

# Condition Markers

N - is set to the sign of the 16 bit X register after the operation.

Z - is set if X is zero after the operation otherwise it is cleared.

CA - not affected.

OF - not affected.

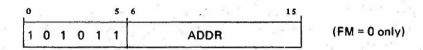

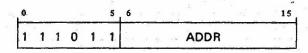

| 1 | 0 |   | - 1 |   |   | 5 | 16   | 15 |

|---|---|---|-----|---|---|---|------|----|

|   | 1 | 1 | 0   | 1 | 0 | 1 | ADDR |    |

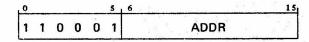

MULTIPLY X: x := x \* hq. The halfword operand from store (multiplier) and the contents of the 16 bit X register (multiplicand) are multiplied together to form a 32 bit product. The result (in the X register) is the least significant 16 bits of the true product.

#### Condition Markers

N - is set to the sign of the true product

Z - is set if the result in the X register is zero, otherwise it is cleared.

CA - not affected

OF - is set if significant bits are lost as a result of truncating the product from 32 to 16 bits.

DX

DIVIDE X REGISTER:  $x := x \div hq$ . The contents of the 16 bit X register (Dividend) are divided by a halfword operand from store (divisor) and the result in X is the integer quotient. All remainders are discarded, the result being rounded towards zero.

#### Condition Markers

N - is set to the sign of the quotient in X.

Z - is set if the quotient in X is zero otherwise it is cleared.

CA - not affected.

OF - is only set if the operand from store is zero or if the divident =  $-2^{15}$  and the divisor = -1. In this case N, Z and X are undefined.

# 7.4 OPERATIONS ON Y AND Z REGISTERS

The following instructions are available: -

LDY - LOAD Y REGISTER

STY - STORE Y REGISTER

ADY - ADD Y REGISTER

SBY - SUBTRACT Y REGISTER

HAY - LOAD ADDRESS INTO Y REGISTER

LDZ - LOAD Z REGISTER

STZ - STORE Z REGISTER

ADZ - ADD Z REGISTER

SBZ - SUBTRACT Z REGISTER

HAZ - LOAD ADDRESS ITO Z REGISTER

# LDY

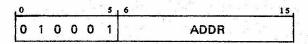

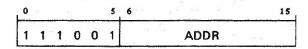

| 0   |   |   |   |   | 5 | 6  | Tar Very | 15 |

|-----|---|---|---|---|---|----|----------|----|

| 1 1 | 1 | 1 | 0 | 0 | 0 | A. | ADDR     |    |

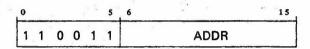

LOAD Y REGISTER: y := hq. The 16 bit register Y is loaded with a halfword operand from store.

**Condition Markers**

Not affected.

STY

STORE Y REGISTER: hq := y. The content of the 16 bit Y register is stored at a halfword address.

Condition Markers

Not affected.

ADY

ADD Y REGISTER: y := y + hq. The halfword operand from store is added to the contents of the 16 bit Y register.

**Condition Markers**

Not affected

**SBY**

SUBTRACT Y REGISTER: y := y - hq. The halfword operand from store is subtracted from the contents of the 16 bit Y register.

**Condition Markers**

Not affected

# HAY

| 0 | 0 5 |   |   |   | 5 | 6 |      | 15 |  |

|---|-----|---|---|---|---|---|------|----|--|

| 0 | 1   | 1 | 0 | 0 | 0 |   | ADDR |    |  |

LOAD HALFWORD ADDRESS INTO Y REGISTER: y := Q. The halfword operand address specified by the instruction is loaded into Y.

Condition Markers

Not affected

# LDZ

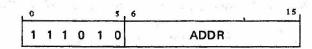

| 0 |   |   |   |   | 5 | 6     |     | (i) |   | 15 |

|---|---|---|---|---|---|-------|-----|-----|---|----|

| 1 | 1 | 1 | 1 | 0 | 0 | * * * | ADI | DR  | + |    |

LOAD Z REGISTER: z := hq. The 16 bit register Z is loaded with a halfword operand from store.

Condition Markers

Not affected

STZ

STORE Z REGISTER: hq := z. The content of the 16 bit Z register is stored at a halfword address.

Condition Markers

Not affected

ADZ

ADD Z REGISTER: z := z + hq. The halfword operand from store is added to the contents of the 16 bit Z register.

Condition Markers

Not affected

| . 0 | +450 |   |   |   | 5 | 6 | ** | 10 E |     | 1   | 15 |

|-----|------|---|---|---|---|---|----|------|-----|-----|----|

| 1   | 1    | 1 | 1 | 1 | 0 | * | 20 | ADD  | ₹ , | * 1 |    |

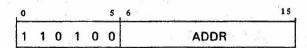

SUBTRACT Z REGISTER: z := z - hq. The halfword operand from store is subtracted from the contents of the 16 bit Z register.

**Condition Markers**

Not affected

HAZ

LOAD HALFWORD ADDRESS INTO Z REGISTER: z := Q. The halfword operand address specified by the instruction is loaded into Z.

**Condition Markers**

Not affected

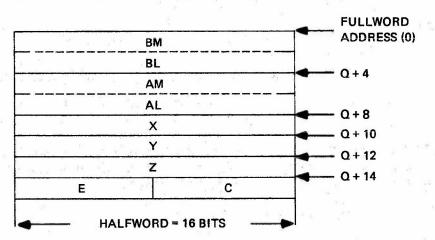

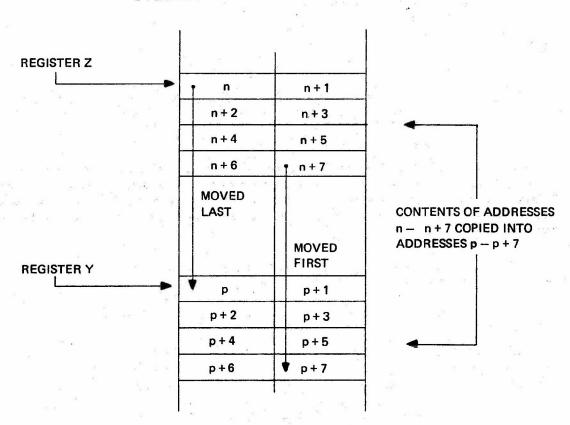

# 7.5 MULTIPLE LOAD AND STORE INSTRUCTIONS

Two instructions are available:-

STM - STORE MULTIPLE LDM - LOAD MULTIPLE

9 registers take part in each of these instructions and the store layout is as below.

| 0 |   |   |   | 1 | 5 | 6   | 1    | 15             |

|---|---|---|---|---|---|-----|------|----------------|

| 0 | 1 | 1 | 0 | 1 | 0 | Co- | ADDR | and the second |

STORE MULTIPLE: The displacement field of the instruction is scaled to provide a fullword address. The address formed by instructions in formats A1—A5 will be truncated to a fullword address. Register BM is stored at this fullword location followed by the registers shown above in successive halfword locations.

All registers are unaffected by the STORE MULTIPLE instruction.

Condition Markers

Not affected.

## LDM

LOAD MULTIPLE: The displacement field of the instruction is scaled to provide a fullword address. The address formed by instructions in formats A1—A5 will be truncated to a fullword address. Register BM is loaded from this fullword location followed by the registers shown above in successive halfword locations.

Condition Markers

The Condition Markers, including FM, are loaded from the Q + 15 store location during LDM.

# 7.6 INDIRECT BRANCHES

Two instructions are available:-

BI - BRANCH INDIRECT

BLI - BRANCH AND LINK INDIRECT

BI

BRANCH INDIRECT: s := hq. A halfword address is formed as specified by the instruction. This is an operand address formed in the same way as for any format A1—A5 instruction. The contents of this location is the branch destination, and is loaded into the sequence control register (S).

Condition Markers

Not affected.

| 0 |   |   |   |   | 5 | 6    | 15 |

|---|---|---|---|---|---|------|----|

| 0 | 1 | 1 | 1 | 1 | 0 | ADDR | 18 |

BRANCH AND LINK INDIRECT: z := s s := hq. A halfword address is formed exactly as in BI above. The contents of the sequence control register S is transferred to Z before S is loaded with the branch destination address.

This instruction is used for subroutine entry with the return link stored in Z.

Condition Markers

Not affected.

## 8

# INSTRUCTIONS AVAILABLE IN FORMAT B

Two unconditional branch instructions only are available in this format:-

B - BRANCH

BL - BRANCH AND LINK

B

BRANCH: s := Q. The sequence control register is incremented or decremented according to the displacement field specified by the instruction. As explained in section 4 (b) the instruction provides unconditional branches relative to the next instruction in sequence. The range of the branch is limited to 511 halfwords forwards and 512 halfwords backwords by the 10 bits of instruction displacement field.

Condition Markers

Not affected.

BL

BRANCH AND LINK: z := s. This instruction performs the same function as B above, and also the original value of the sequence control register is placed in Z. This provides for subroutine entry and return.

Condition Markers

Not affected.

#### 9

## INSTRUCTIONS AVAILABLE IN FORMAT I.

These instructions are called literal instructions since where an operand is required it is specified exactly by the instruction displacement field. Some instructions depend on their displacement fields to further define their function.

# 9.1 OPERATIONS ON THE 32 BIT ACCUMULATOR

The following instructions are available:-

LDL - LOAD LITERAL ADL - ADD LITERAL

SBL - SUBTRACT LITERAL

ML - MULTIPLY LITERAL

DL - DIVIDE LITERAL

NL - AND LITERAL

CPL - COMPARE LITERAL

LDL

LOAD LITERAL: a := D. The operand formed by the 8-bit displacement field is loaded into the least significant byte of the accumulator. The most significant 3 bytes of the accumulator are cleared. As described in section 4.2 it is thus possible to load numbers in the range 0-255 into the 32 bit accumulator.

# Condition Markers

N - is cleared by the operation.

Z - is set if the result in the 32 bit accumulator is zero, otherwise it is cleared.

CA - not affected.

OF - not affected.

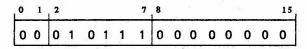

ADL

ADD LITERAL: a := a + D. The operand specified by the 8-bit displacement field is extended to 32 bits by most significant zeros before the operation. This operand is then added to the contents of the 32 bit accumulator.

#### Condition Markers

N - is set to the true sign of the result.

Z - is set if the result in the 32 bit accumulator is zero, otherwise it is cleared.

CA - is set if there is a carry out of the most significant bit of the 32 bit accumulator,

otherwise it is cleared.

OF - is set if arithmetic overflow occurs, otherwise it remains unchanged.

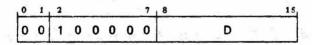

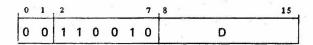

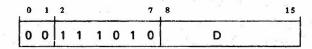

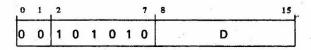

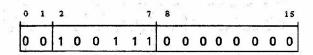

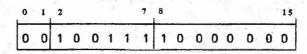

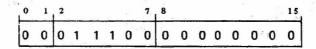

| 0 | 1 | 2 |   |     | 7   | 8 |   | 15    |

|---|---|---|---|-----|-----|---|---|-------|

| 0 | 0 | 1 | 0 | 0 0 | 1 0 |   | D | 10 11 |

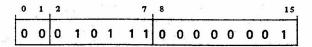

SUBTRACT LITERAL: a := a - D. The operand specified by the 8-bit displacement field is extended to 32 bits by most significant zeros before the operation. This operand is then subtracted from the contents of the 32 bit accumulator.

#### Condition Markers

N - is set to the true sign of the result.

Z - is set if the result in the 32 bit accumulator is zero, otherwise it is cleared.

CA - is set if there is aborrow out of the most significant bit of the 32 bit accumulator,

otherwise it is cleared.

OF - is set if arithmetic overflow occurs, otherwise it remains unchanged.

**CPL**

COMPARE LITERAL: form a - D. The operand specified by the instruction displacement field is extended to 32 bits by most significant zeros. This operand is then compared with the contents of the 32 bit accumulator. The accumulator is unaffected by the instruction.

#### Condition Markers

$\boldsymbol{Z}$

N - is set if the 32 bit accumulator is less than the 32 bit literal operand, otherwise it is

is set if the 32 bit accumulator equals the 32 bit literal operand, otherwise it is

CA - is set if there is a borrow out of the most significant bit of the function unit as a result of the comparison, otherwise it is cleared.

OF - is set if arithmetic overflow occurs, otherwise it remains unchanged.

NL

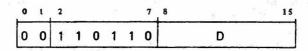

| 0 | 1 | 2 |   |   |   |   | 7 | 8 | 15 |

|---|---|---|---|---|---|---|---|---|----|

| 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | D | -  |

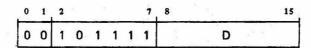

AND LITERAL: a := a \(\D\). The operand specified by the displacement field of the instruction is extended to 32 bits by most significant zeros. This 32 bit operand is used to perform the logical AND function with the contents of the 32 bit accumulator. The result is placed in the accumulator.

### Condition Markers

N - is cleared by the instruction.

Z - is set if the result in the accumulator is zero, otherwise it is cleared.

CA - not affected.

| 0 | 1 | 2 | 1 |   |    | T | 7 | 8 |   | . 1 | 15 |

|---|---|---|---|---|----|---|---|---|---|-----|----|

| 0 | 0 | 1 | 0 | 0 | -1 | 0 | 1 |   | D |     | ,  |

MULTIPLY LITERAL: a := a \* D. The 8-bit operand specified by the displacement field of the instruction and the contents of the 32 bit accumulator are multiplied together to form a 40 bit product. The result, in the accumulator, is the least significant 32 bits of the true product.

### Condition Markers

N - is set to the sign of the true 40 bit result.

Z - is set if the result in the 32 bit accumulator is zero, otherwise it is cleared.

CA - not affected.

OF - overflow is set if significant bits are lost in the truncation of the product.

DL

| ı | 0 | 1 | 2 |   |   |   |   | 7. | 8 | 15 |

|---|---|---|---|---|---|---|---|----|---|----|

|   | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0  | D |    |

DIVIDE LITERAL:  $a := a \div D$  b := remainder. The contents of the 32 bit accumulator (dividend) are divided by the 8-bit operand specified by the instruction displacement field. This 8-bit operand is extended to 16 bits before the operation by most significant zeros. The result, in the accumulator, is the 32 bit integer quotient. The result in B is the 16 bit remainder, sign extended to 32 bits. The sign of the remainder is always equal to the sign of the dividend (see section 7.1).

### Condition Markers

N - is set to the sign of the 32 bit quotient in the accumulator.

Z - is set if the quotient is zero, otherwise it is cleared.

CA - not affected.

OF - overflow is set if the divisor is zero. The content of A, B, N and Z are then

undefined.

# 9.2 LITERAL OPERATIONS ON THE X REGISTER

The following instructions are available:-

LDXL - LOAD X LITERAL

ADXL - ADD X LITERAL

SBXL - SUBTRACT X LITERAL MXL - MULTIPLY X LITERAL

DXL - DIVIDE X LITERAL

NXL - AND X LITERAL

CPXL - COMPARE X LITERAL

LDXL

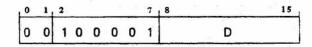

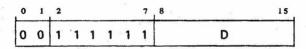

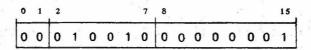

| 0 | 1 | 2 |   |   |   |   | 7 | 8 |   | 15 |

|---|---|---|---|---|---|---|---|---|---|----|

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |   | ) | 19 |

LOAD X LITERAL: x := D. The operand specified by the 8-bit displacement field is extended to halfword length (16 bits) by most significant zeros. This 16 bit operand is loaded into the 16 bit X register.

### Condition Markers

N - is cleared by the instruction.

Z - is set if the X register is made zero by the operation, otherwise it is cleared.

CA - not affected.

OF - not affected.

# ADXL

ADD X LITERAL: x := x + D. The operand specified by the 8-bit displacement field is extended to 16 bits by most significant zeros. This 16 bit operand is then added to the contents of the 16 bit X register.

### **Condition Markers**

N - is set to the true sign of the result.

Z - is set if the result in the X register is zero, otherwise it is cleared.

CA - is set if there is a carry out of the most significant bit of the X register,

otherwise it is cleared.

OF - is set if arithmetic overflow occurs due to the operation in X.

### SBXL

SUBTRACT X LITERAL: x := x - D. The operand specified by the 8 bit displacement field is extended to 16bits by most significant zeros. This 16 bit operand is then subtracted from the contents of the 16 bit X register.

### **Condition Markers**

N - is set to the true sign of the result.

Z - is set if the result in the X register is zero, otherwise it is cleared.

CA - is set if there is aborrow out of the most significant bit of the X register, otherwise it is

cleared.

OF - is set if arithmetic overflow occurs due to the operation in X.

# MXL

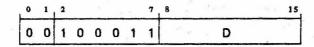

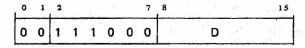

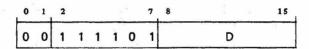

| 0 | 1 | 2 |   |   |   |   | 7 | 8 |     |    | 15   |

|---|---|---|---|---|---|---|---|---|-----|----|------|

| 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 |   | - 7 | Ď, | V-10 |

MULTIPLY X LITERAL: x := x \* D. The operand specified by the displacement field of the instruction and the contents of the 16 bit X register are multiplied together to form a 24 bit product. The result, in X, is the least significant 16 bits of this 24 bit product.

### Condition Marker

N - is set to the sign of the true 24 bit product.

Z - is set if the result in the X register is zero, otherwise it is cleared.

CA - not affected.

OF - is set if significant bits are lost in the truncation from 24 to 16 bits.

### DXL

DIVIDE X LITERAL:  $x := x \div D$ . The contents of the 16 bit X register (dividend) are divided by the 8 bit operand (divisor) specified by the instruction displacement field. This 8 bit operand is extended to 16 bits before the operation by most significant zeros. The result, in X, is the true integer quotient. Remainders are discarded, the result being rounded towards zero.

### Condition Markers

N - is set to the sign of the 16 bit quotient in the X register.

Z - is set if the result in the X register is zero, otherwise it is cleared.

CA - not affected.

OF - is set if the divisor is zero. The contents of N, Z and X are then undefined.

# NXL

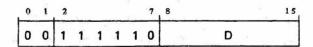

| 0 | 1 | 2 |     |   | **  | 7 | 8 | 15 |

|---|---|---|-----|---|-----|---|---|----|

| 0 | 0 | 1 | . 1 | 0 | 1 0 | 0 | D | 4  |

AND X LITERAL:  $x := x \land D$ . The operand specified by the 8 bit displacement field is extended to 16 bits by most significent zeros. This 16 bit operand is used to form the logical AND function with the contents of the 16 bit X register. The result is placed in the X register.

# Condition Markers

N - is cleared by the operation.

Z - is set if the result in the X register is zero, otherwise it is cleared.

CA - not affected.

OF - not affected.

### **CPXL**

| 0 | 1 | 2 |   |   |   |   | 7 | 8 | 15 |

|---|---|---|---|---|---|---|---|---|----|

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | D |    |

COMPARE X LITERAL: form x - D. The operand specified by the 8 bit displacement field is extended to 16 bits by most significant zeros. This 16 bit operand is then compared with the 16 bit content of the X register. The X register is unaffected by the operation.

#### Condition Markers

N - is set if the 16 bit X register is less than the 16 bit literal operand, otherwise it is cleared.

Z - is set if the 16 bit X register equals the 16 bit literal operand, otherwise it is cleared.

CA - is set if there is a borrow out of the most significant bit of the function unit as a result of the comparison, otherwise it is cleared.

OF - is set if arithmatic overflow occurs.

# 9.3 LITERAL OPERATIONS ON THE Y AND Z REGISTERS

The following instructions are available:-

LDYL - LOAD Y LITERAL ADYL - ADD Y LITERAL

SBYL - SUBTRACT Y LITERAL CPYL - COMPARE Y LITERAL LDZL - LOAD Z LITERAL

ADZL - ADD Z LITERAL

SBZL - SUBTRACT Z LITERAL CPZL - COMPARE Z LITERAL

N.B.

Before all the following operations the 8 bit displacement field of the instruction is extend to 16 bits by most significant zeros. It is then used as a 16 bit literal operand.

# LDYL

LOAD Y LITERAL: y := D. The literal operand is loaded into the 16 bit Y register.

**Condition Markers**

Not affected.

# ADYL

ADD Y LITERAL: y := y + D. The literal operand is added to the contents of the 16 Y register.

Condition Markers

Not affected.

# SBYL

SUBTRACT Y LITERAL: y := y - D. The literal operand is subtracted from the contents of the 16 bit Y register.

Condition Markers

## CPYL

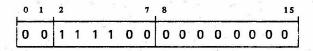

| 0 | . 1 | 2 |   |   |   |   | 7 | 8 | 15 |

|---|-----|---|---|---|---|---|---|---|----|

| 0 | 0   | 0 | 1 | 1 | 0 | 1 | 1 | D |    |

COMPARE Y LITERAL: form y - D. The literal operand is compared with the contents of the Y register. Y is unaffected by this operation.

### **Condition Markers**

N - is set if Y is less than the literal operand.

Z - is set if the result of the operation is zero, otherwise it is cleared.

CA - is set if there is a borrow out of the most significant bit of the function unit as a

result of the comparison, otherwise it is cleared.

OF - is set if arithmetic overflow occurs.

# LDZL

LOAD Z LITERAL: z := D. The literal operand is loaded into the 16 bit Z register.

**Condition Markers**

Not affected.

ADZL

ADD Z LITERAL: z := z + D. The literal operand is added to the contents of the 16 bit Z register.

Condition Markers

Not affected.

SBZL

SUBTRACT Z LITERAL: z := z - D. The literal operand is subtracted from the contents of the 16 bit Z register.

**Condition Markers**

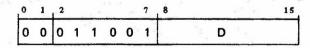

| 0 | 1 | 2 |   |   |   |   | 7 | 8 |   | 15 |

|---|---|---|---|---|---|---|---|---|---|----|

| 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |   | D | 10 |

COMPARE Z LITERAL: form z - D. The literal operand is compared with the contents of the Z register. Z is unaffected by this operation.

### **Condition Markers**

N - is set if Z is less than the literal operand.

Z - is set if the result of the operation is zero, otherwise it is cleared.

CA - is set if there is a borrow out of the most significant bit of the function unit as a

result of the comparison, otherwise it is cleared.

OF - is set if arithmetic overflow occurs.

# 9.4 CONDITION BRANCH INSTRUCTIONS IN FORMAT L

The following instructions are available: -

BN - BRANCH IF NEGATIVE

BNN - BRANCH IF NON NEGATIVE

BZ - BRANCH IF ZERO

BNZ - BRANCH IF NON ZERO

BP - BRANCH POSITIVE

BNP - BRANCH IF NON POSITIVE

BOF - BRANCH IF OVERFLOW

BNCA - BRANCH IF NO CARRY

BPAR - BRANCH ON ODD PARITY

For these instructions the branch destination is formed by scaling the literal displacement (D) for halfword (i.e. left shifting it one place), sign extending it to 16 bits and then adding it to the current contents of the sequence control register (S).

Branches of 127 instructions ahead or 128 instructions behind the next instruction in sequence may be performed (see section 4.3).

If a branch is taken then

$$S = S + 2D$$

where  $D = +127 \dots -128$

otherwise for a branch not taken the next instruction in sequence is obeyed.

BN

BRANCH IF NEGATIVE: if N then s := Q. If the negative condition marker is true the branch is taken.

**Condition Markers**

BNN

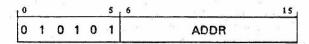

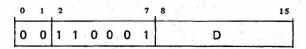

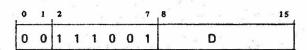

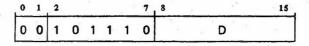

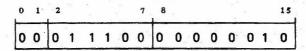

| 1 | 0 | 1 | 2 |   |   |   |   | 7 | 8  | 15 |

|---|---|---|---|---|---|---|---|---|----|----|

| 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | .4 | D  |

BRANCH IF NON NEGATIVE: if  $\overline{N}$  then s := Q. If the negative condition marker is false the branch is taken.

Condition Markers

Not affected.

ΒZ

BRANCH IF ZERO: if Z then s := Q. If the zero condition marker is true the branch is taken.

Condition Markers

Not affected.

BNZ

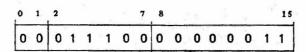

| , | 0 | 1 | 2 |   |   |   |   | 7 | 8 | 15 |   |

|---|---|---|---|---|---|---|---|---|---|----|---|

|   | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 |   | D  | 1 |

BRANCH IF NON ZERO: if  $\overline{Z}$  then s := Q. If the zero condition marker is false the branch is taken.

Condition Markers

Not affected.

BP

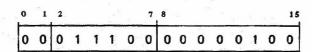

| 0 | 1 | 2 |   |   |   |   | 7 | 8   |   | 15  |

|---|---|---|---|---|---|---|---|-----|---|-----|

| 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | NT. | D | 101 |

BRANCH IF POSITIVE:  $\underline{if} \ \overline{N} \land \overline{Z}$  then s := Q. If the zero condition marker AND the negative marker are false the branch is taken.

Condition Markers

### **BNP**

| 0 | 1 | 2 |   | 12. |   |   | 7 | 8     | 2.0 | 15  |

|---|---|---|---|-----|---|---|---|-------|-----|-----|

| 0 | 0 | 1 | 0 | 1   | 1 | 0 | 1 | 11.11 | D   | -1- |

BRANCH IF NON POSITIVE:  $\underline{if} \ N \ V \ Z \ \underline{then} \ s := Q$ . If the zero condition marker OR the negative marker are true then the branch is taken.

Condition Markers

Not affected.

### BOF

BRANCH IF OVERFLOW: if OF then  $\triangleleft$  OF := 0 s := Q  $\geqslant$  If the overflow condition marker (OF) is true then the branch is taken,

### Condition Markers

N – not affected.

Z – not affected.

CA - not affected.

OF - resets to zero.

# **BNCA**

BRANCH IF NO CARRY:  $\underline{if}$   $\overline{CA}$  then s := Q. If the carry condition marker (CA) is false then the branch is taken.

**Condition Markers**

Not affected.

# **BPAR**

| 0 | 1 | 2 |     |   |   |   | 7 | 8 | 15 |

|---|---|---|-----|---|---|---|---|---|----|

| 0 | 0 | 0 | - 1 | 1 | 0 | 0 | 0 | D |    |

BRANCH ON ODD PARITY: The least significant byte of the accumulator is examined and if it has odd parity the branch is taken. The parity of the least significant byte of A is defined as odd, if the number of bits which are set to 1 are odd.

Condition Markers

# 9.5 SHIFT INSTRUCTIONS

The following instructions are available:-

SHIFT LITERAL

SHIFT INDEXED

## SHIFT LITERAL

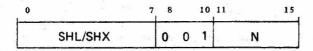

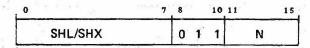

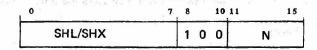

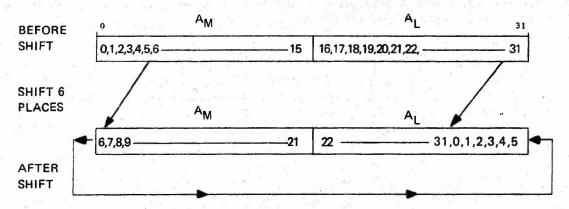

SHIFT LITERAL: D Defines Shift. The type, direction and number of places to be shifted are further defined by the displacement field of the instruction. The 8 bit literal operand directly controls the shift operation.