# a review for industry

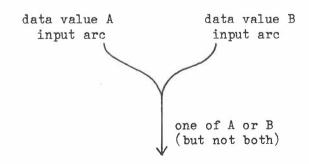

a conference sponsored by the Science and Engineering Research Council

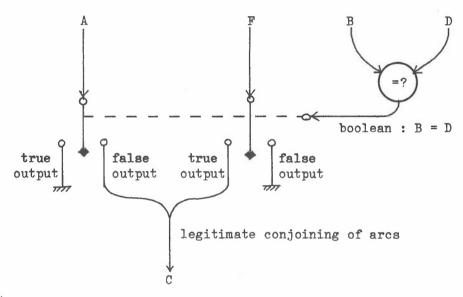

3-4 March 1983 National Computing Centre Manchester

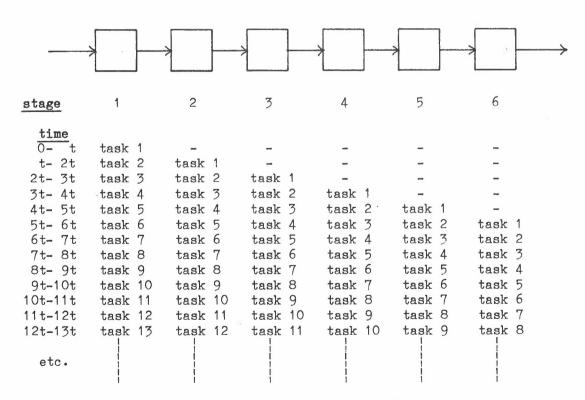

#### DISTRIBUTED COMPUTING

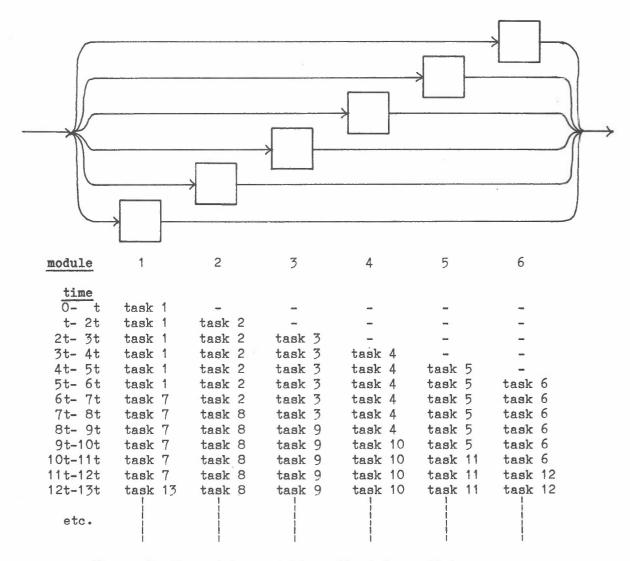

## A Review for Industry

#### Contents

| 1. | Local Area Networks                                                                                    | Dr E B Spratt<br>(University of Kent)                     |

|----|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| 2. | Evaluating Local Area Networks                                                                         | Dr D Shepherd<br>(University of Strathclyde)              |

| 3. | MININET: An Ultra-Transparent Local Area<br>Network for Service to High-Speed<br>Instrumentation Users | Prof G D Cain<br>(Polytechnic of Central<br>London)       |

| 4. | The Structuring of Distributed Computing Systems                                                       | Prof B Randell<br>(University of Newcastle-<br>Upon-Tyne) |

| 5. | Closed Coupled Systems                                                                                 | Prof R L Grimsdale<br>(University of Sussex)              |

| 6. | New Programming: Functional and Logic Languages                                                        | Dr J Darlington<br>(Imperial College, London)             |

| 7. | Novel Architectures                                                                                    | Dr M R Sleep<br>(University of East Anglia)               |

| 8. | Dataflow Computer Architecture                                                                         | Dr J R Gurd<br>(University of Manchester)                 |

Each Section contains a review report and viewgraph material which will be used in the conference presentations.

# "RINGS AND THINGS" A Report for SERC/DCS Committee on Local Area Networks (or Local Networks), by E. B. Spratt University of Kent

#### 1. Preamble

This report has been prepared on behalf of the SERC for the Industrial Distributed Computing Systems Conference in March 1983. An attempt has been made to cover the main types and applications of Local Networks in use within the U.K. with reference to the position in the last quarter of 1982 together with some discussion on comparative assessments and standards. The emphasis is on systems in use within the Academic Community i.e. sites within the SERC (Science Engineering Research Council) the Universities and Polytechnics.

The views presented in what follows are personal to the author and do not in any way reflect the policy of the SERC, the University of Kent or indeed any other official body with which the author is associated. The task of selecting suitable material from the large (and growing) amount of available information has not been easy and any omissions should be viewed in this light.

Numbers in square brackets e.g. [9], refer to individual items in the list of references given at the end of this report.

#### 2. Organisation of the report

The material in this report is organised as follows

- 3. general introduction

- 4. a note on terminology

- 5. technology for local networks

- transmission media

- access methods

- 6. comparative issues

- 7. protocols for local and wide area networks

- 8. standards

- 9. current work in the U.K.

- 10. local networks which are marketed in the U.K.

- 11. some current applications of local networks

- 12. a users survey on local networks

- 13. conclusions

- 14. references

#### 3. General Introduction

We commence by explaining what is meant by a local network. They have three distinctive properties.

- (1) A diameter of up to 2 to 3 kilometres.

- (2) A raw (or total) data rate exceeding one megabit per second.

- (3) Owned by a single organisation.

The reader who is interested in a general introduction to local networks should consult [12] or [1].

There are two main reasons why local networks are required, and these are essentially the same reasons that organisations are interested in networks in general.

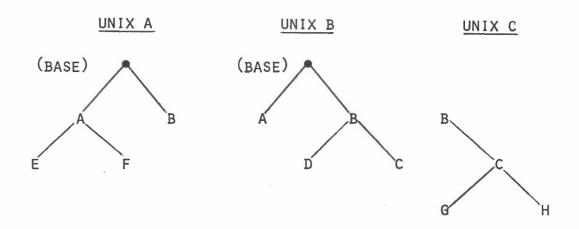

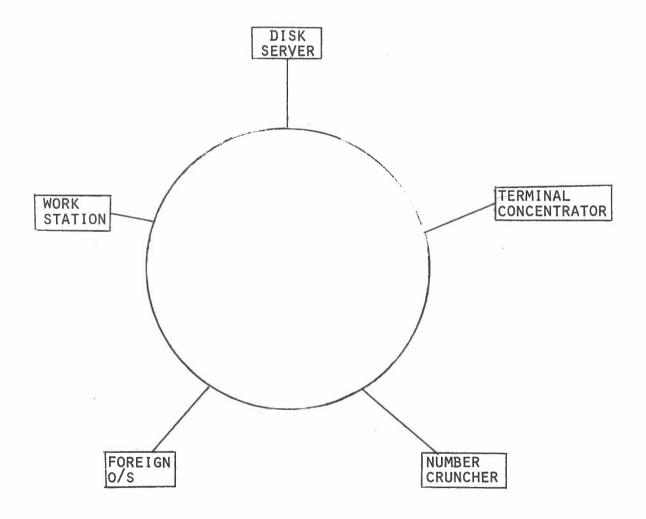

The first reason for an interest in local networks is to exploit the advantages of functionally distributed computing. Typically, if this approach is followed some of the computers are dedicated to specific functions such as terminal handling, data base management, file storage, printing or controlling industrial control equipment. This is the main relevance of local networks for the SERC Distributed Computer Systems research program. As is well known SERC made a policy decision some three years ago to standardise on one particular local network, namely the Cambridge Ring (which we consider further in a later section) to act as a common research vehicle for research groups in this area.

The second reason for the importance of local networks is to interconnect computers, terminals, and peripherals which are located either in the same building or in many cases in nearby buildings, in such a way as to enable them to intercommunicate and also to allow them all to access a remote host computer or another network. The presence of the local network makes it possible for the remote facility to connect to the local network at one particular point (which is usually called a gateway).

It is this latter reason which has led many Universities and Polytechnics to plan and in some cases to implement computer services based on local networks. The Joint Network Team of the Computer Board and the Science Engineering Research Council is finding and co-ordinating development work in this area. It will be recalled that the Computer Board is responsible for the provision of computer systems for central university computer services, whilst the Joint Network Team is funded jointly by the Computer Board and the SERC, to be responsible for co-ordinating network activities between the SERC and the universities and other sites within the Academic Community. One important aspect of this work is the implementation of standards and reference is made to this later in this report.

Local Networks are an important component of the SERC Common Base Software Policy which concentrates on two languages, Fortran 77 and Pascal on GEC and Prime minicomputers together with ICL PERQ workstations, where the latter are connected by means of Cambridge Rings.

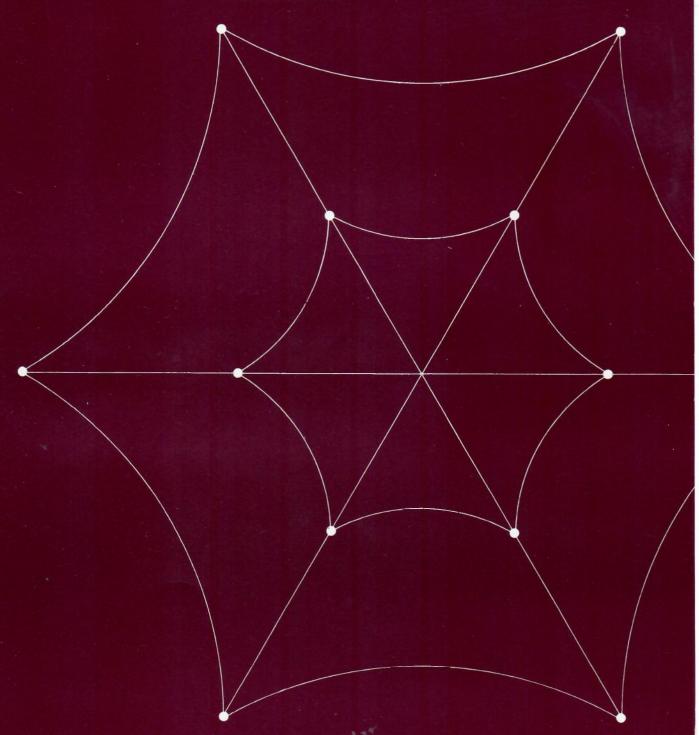

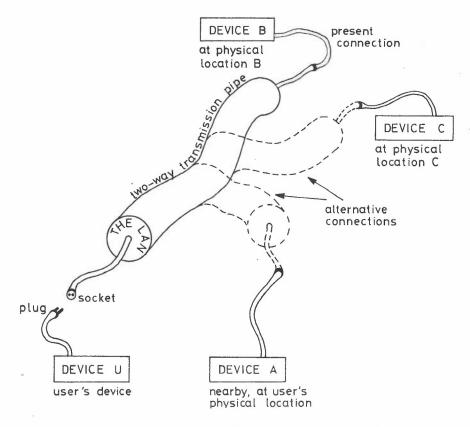

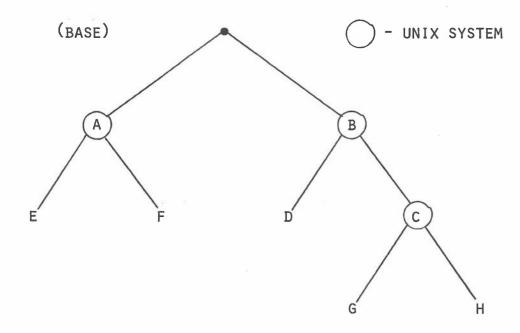

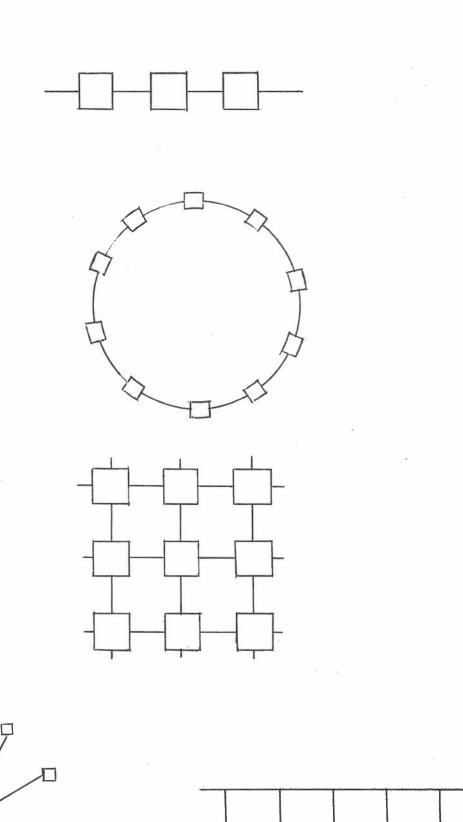

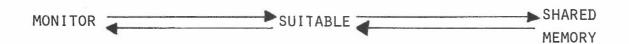

Local networks differ from the wide area (or long haul) type in several ways (Fig 1). A crucial difference is that the developers of wide area networks are often compelled by legal or economic reasons to

use the public telephone network, which is not necessarily the most suitable technical choice. On the other hand the designers of local networks can choose and even lay their own choice of high bandwidth cables. This gives them definite advantages. In particular, bandwidth (or simply the carrying capacity of the network) is not such a scarce resource as for wide area networks and thus it is not necessary to optimize its use with local networks to anything like the extent that is done in the wide area case.

#### 4. A note on terminology

Here we explain certain terms which will be used in this report.

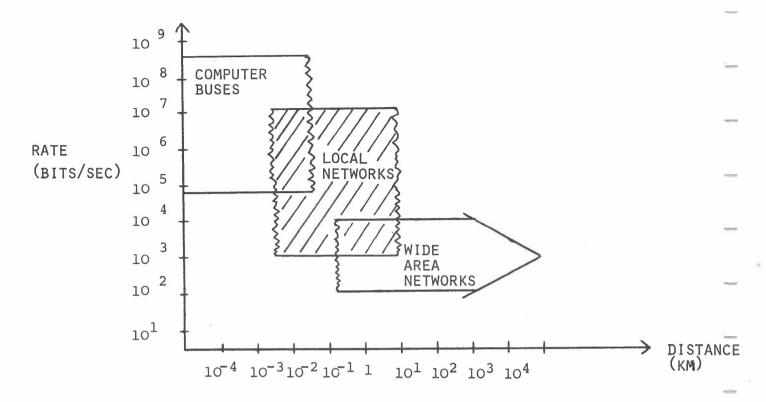

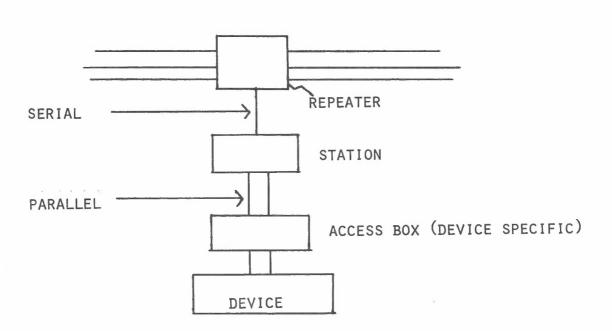

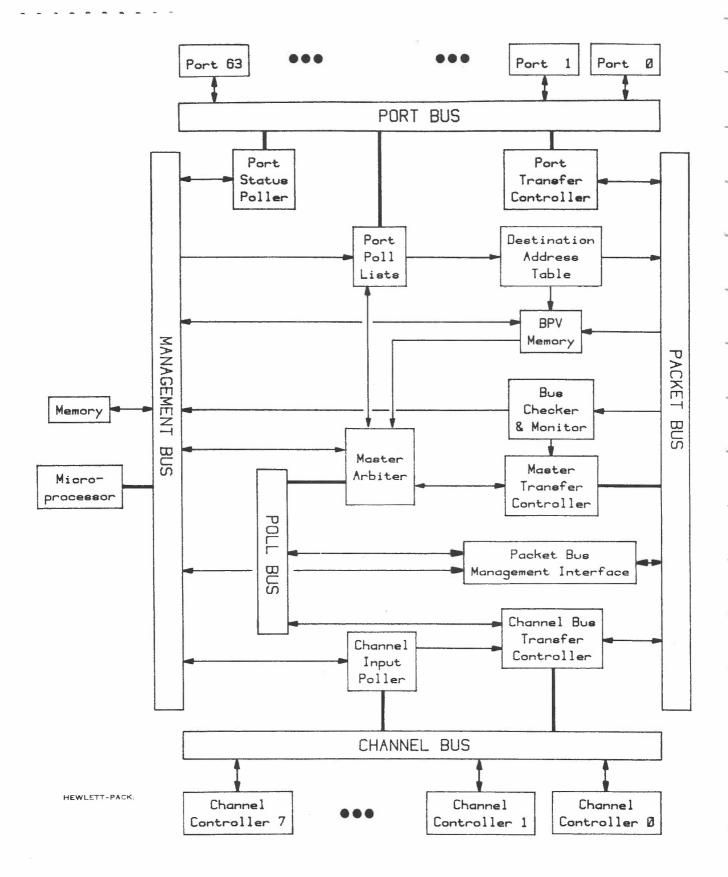

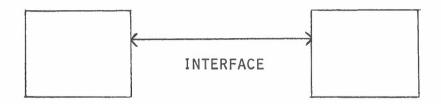

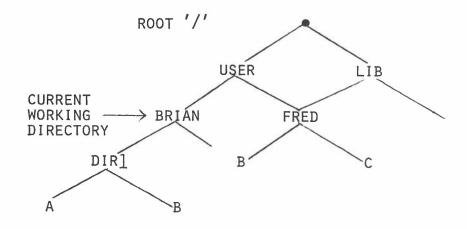

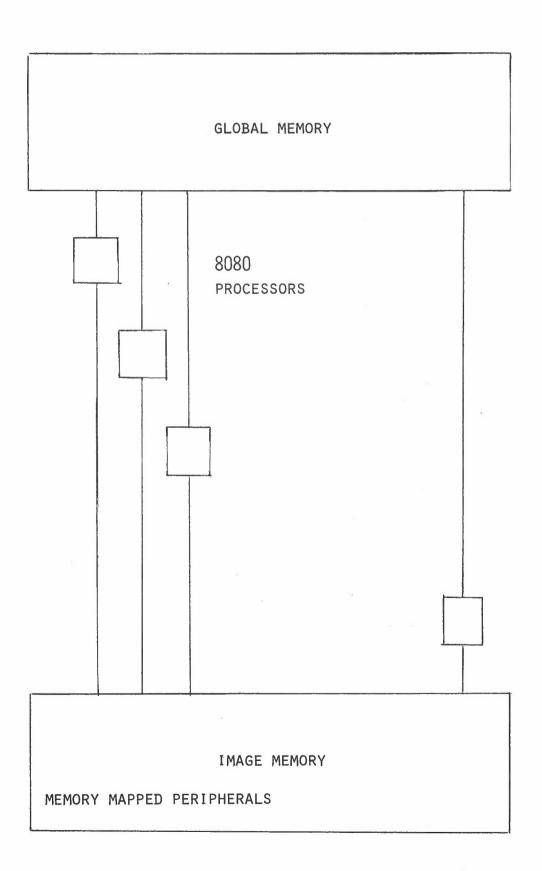

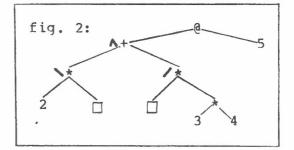

A local network (or indeed a wide area network) essentially consists of nodes which are linked together in some way by means of a transmission medium, these nodes usually consist of several logically distinct components which may or may not be physically distinct. For instance there is always a means of allowing an attachment to the transmission medium, some standard logic and device specific logic which is used to attach the actual user device. The latter could for example consist of a simple micro to operate sensory devices, a mini or even a mainframe computer (Fig 2).

One of the most crucial concepts in networking is that of a protocol. A protocol is a precise set of rules which enable computer systems to intercommunicate. It is important to realise that protocols are necessary with both the hardware and software aspects of communication and there is usually more than one level of protocol involved.

#### 5. Technologies for Local Networks

In this section we consider a number of topics concerned with technologies for local networks. Although it may be fashionable to debate the issues in this area they seldom take the same importance to the end user.

#### 5.1. Media for local networks

There are four areas to consider

- type of cabling

- broadband and baseband

- passive

- network layout

Before discussing these separately it should be noted that we assume serial transmission is being used. Although parallel transmission is feasible there appears to be no particular requirement for this at the present time due to the high speeds which are available for serial transmission and the costs of working with parallel transmission.

## Cabling

The three main cable types are twisted pair, coaxial and fibre optic. There are many different forms of both twisted pairs and coaxial

cable to meet various specifications, e.g. noise immunity, and choice of bandwidth. The important point is that both these choices are quite satisfactory for the majority of local network environments. The choice of cable type is usually determined by engineering considerations and installation issues. With environments which have high levels of electromagnetic radiation or there is a requirement for high speed serial transmission the natural choice is for fibre optic cable and there is little doubt this will come into much more common use after a year or

#### Baseband and Broadband

The difference between these two types of media is that in the baseband case there is a single channel for the information flow whereas in the broadband case there are a number of channels superimposed on a single cable using frequency division multiplexing techniques. A number of techniques are used to control access to the baseband media and these are considered in a later section. It should be noted that these techniques may also be used with individual broadband channels.

Broadband cabling is based on CATV (Cable Television) technology and has more bandwidth than a similar baseband system. However the broadband channels are independent, so it is necessary for attached devices to select channels using frequency agile modems, with special switching equipment being used to enable connections between different channels to be made. One issue which has to be faced with this technique is that modems operating at radio frequencies are required to access these channels and if the costs of such equipment are to be kept within reasonable bounds then the bandwidth of the individual channels must be roughly in the range 5 to 10 megabits/second. If this remains a serious limitation in the future then it would appear that the next generation of baseband systems which should work in the 50 to 100 megabit range would be very attractive. Although there is much debate on the broadband v baseband issue it is perhaps likely that the two media will co-exist as, to an extent, they are complementary.

### Passive or Active Systems

There has been much discussion on the advantages and disadvantages of these systems. Two comments are perhaps in order, firstly, high reliability systems can be achieved at reasonable costs and secondly, the increasing availability of LSI components for devices such as repeaters should also significantly improve reliability. In either case it is essential to be able to rapidly locate and fix faults.

## Network layout

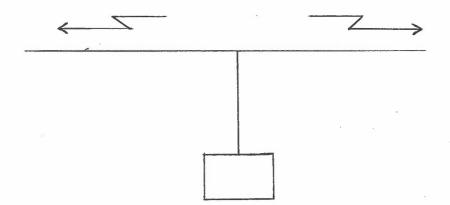

There are two related issues here. Firstly the network topography, which is the way in which the cabling is actually installed, and secondly the network topology which is a way of describing the logical links between the nodes.

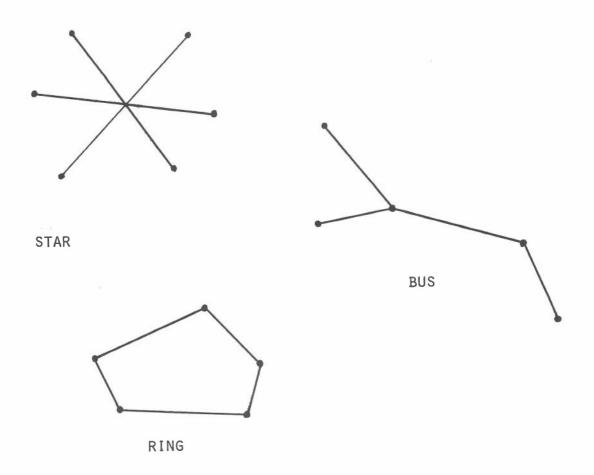

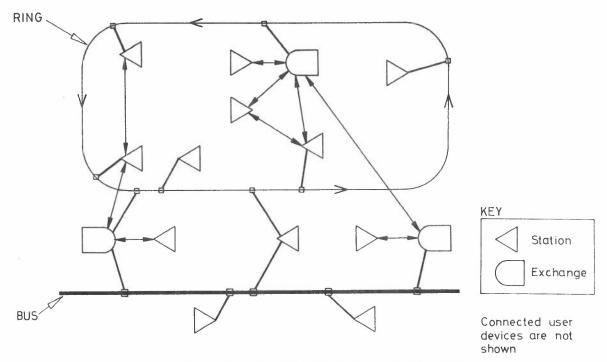

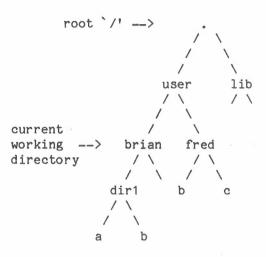

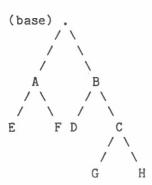

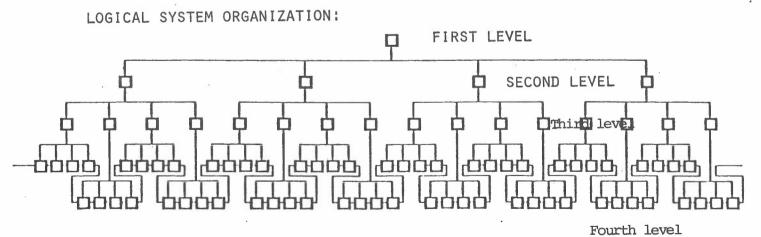

Various topologies have been proposed e.g. rings, busses and stars. However many actual networks are made up of more complex topologies. For instance it is possible to use a central ring with linked subrings and some systems consist of interconnected busses forming tree configurations. (See Fig 3). Major considerations when choosing a topology are network management, reliability and maintenance. The topography is of course directly related to the wiring costs and hence the economics of a local network.

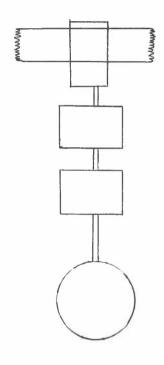

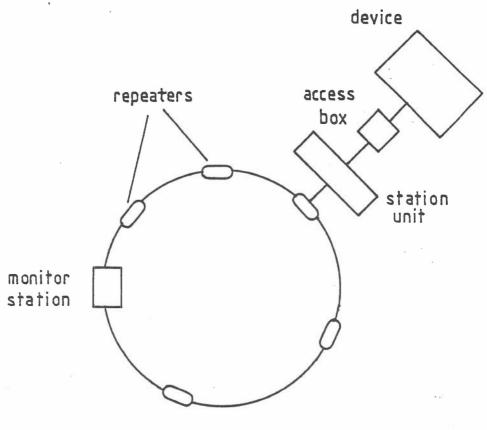

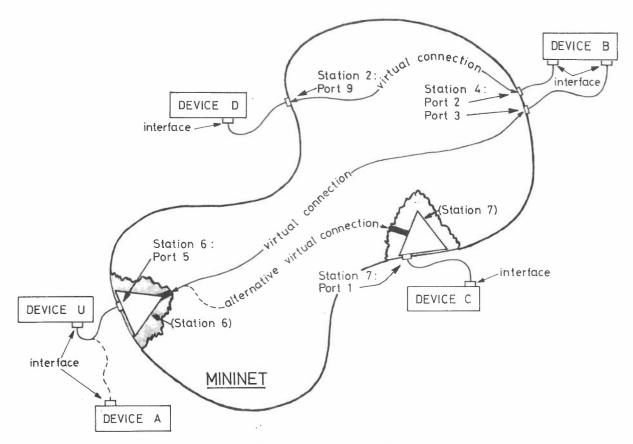

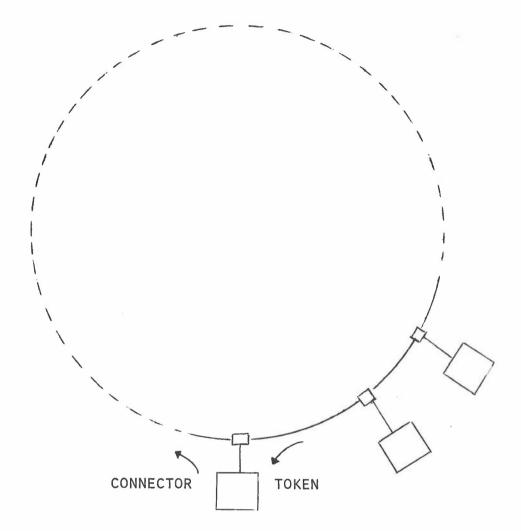

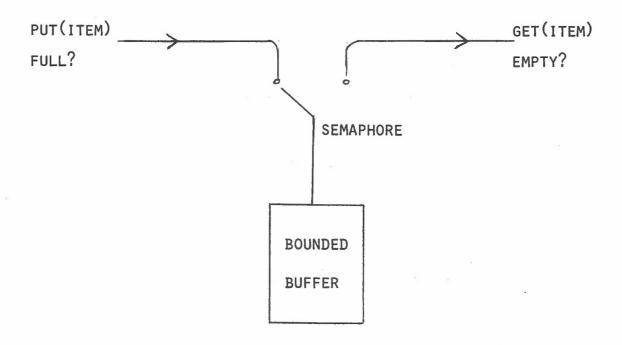

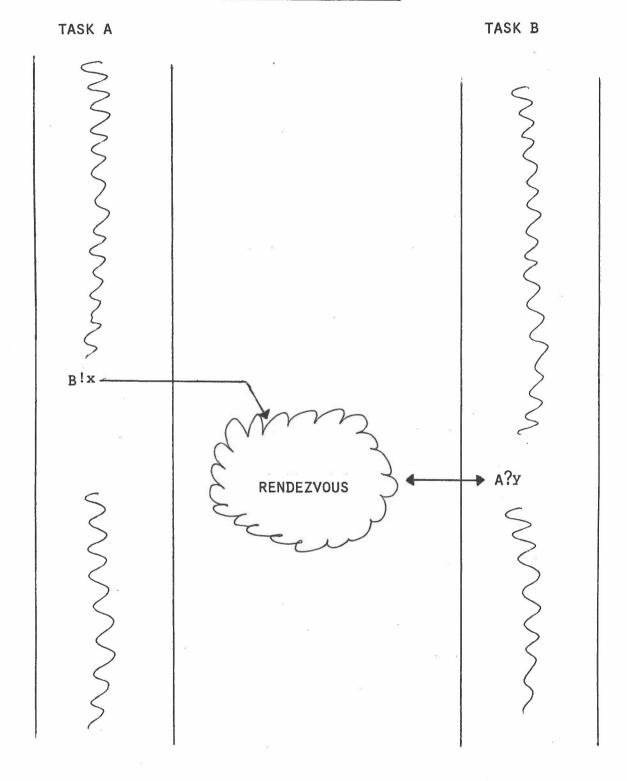

#### 5.2. Slotted Rings

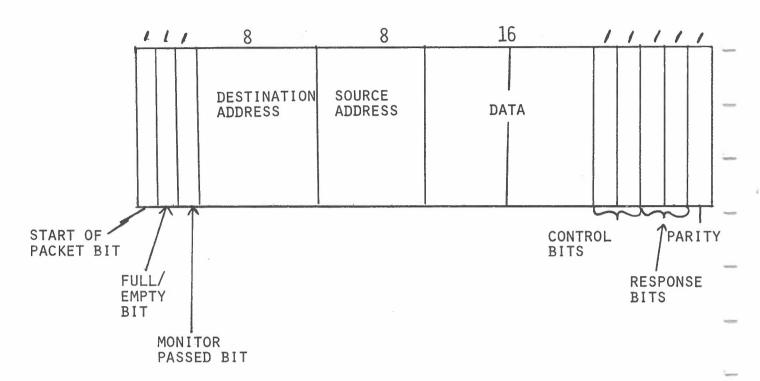

This section refers to the specific case of a Cambridge Ring rather than a general slotted ring since the former has most of the important characteristics of this particular type of local network. The ring is formed from nodes which are joined by means of suitable cabling, this can be either twisted pairs or fibre optics and it is perfectly feasible to mix these two types. With twisted pairs the length of cabling between nodes is normally about 200 metres and there must be a repeater at each node to regenerate the signal. Some nodes may consist solely of repeaters but others may have user devices attached to them. In the latter case the repeater is used for the attachment to the transmission medium as noted in an earlier section. In this case the interface between the user device and the repeater is called a station, and such a node is often referred to simply as a station (Fig 4). The operation of the Cambridge Ring is based on the setting up and subsequent use of circulating slots or fixed size packets (or units of information) which pass continuously round the ring in a undirectional manner. Clearly there must be at least one of these packets. Each packet contains data, the address of the source and destination nodes together with control information.

This slot structure is created when the ring is turned on, using a special station called the monitor. Thereafter the monitor continuously checks this structure and corrects it if necessary. For example, there is a mechanism to set a bit to show as empty packets which may have become full due to errors.

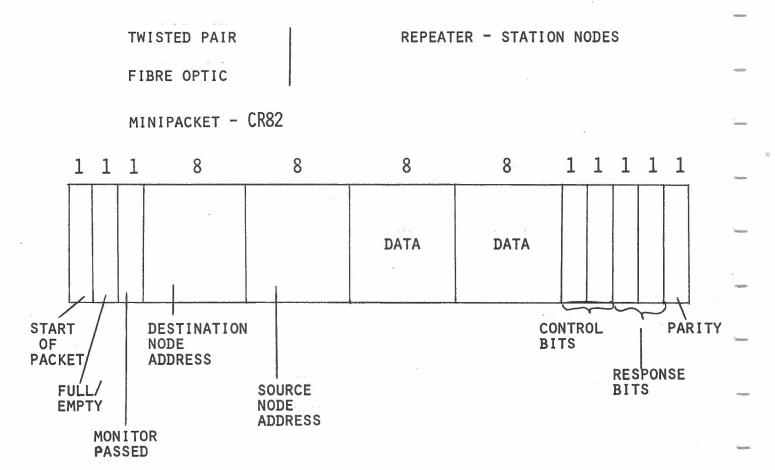

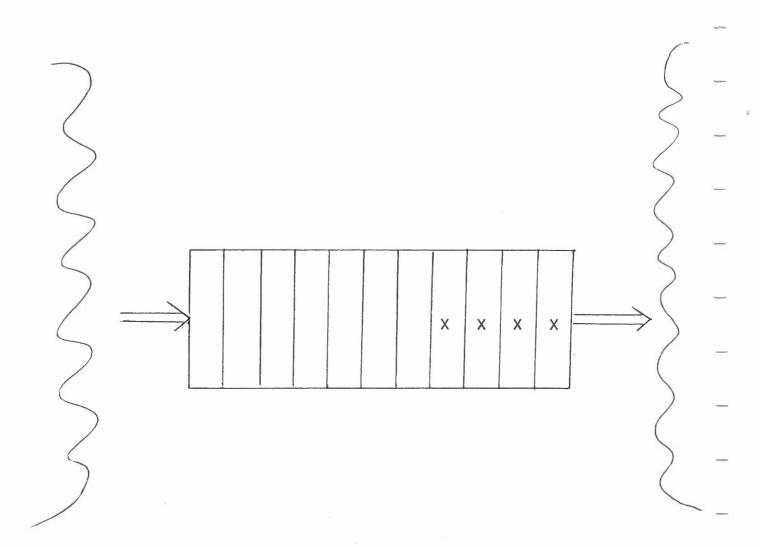

The original packet size was 38 bits but the current version (known as CR82) includes two additional control bits that may be used in the implementation of higher level protocols. Each packet contains two 8 bit fields which are for the destination and source addresses and a 16 bit field for data. The remaining bits are used for control purposes, e.g. to indicate whether the slot is full or empty and whether the data was accepted (or rejected) at the destination (see Fig 5).

The stations each have a select register which can be set to either accept (or reject) all packets which are addressed to it or receive from a specified source. This provides a selection mechanism which, together with the values of the slot response bits provides efficient low level acknowledgement and control facilities.

It is not possible for any of the network nodes to monopolise the traffic since the sender clears its own packet after it has been round the ring and is not then allowed to use it again immediately. There is also a facility to prevent a node which is transmitting at a high data rate from swamping a node with a slow receiver. The above description assumes that all the nodes have devices attached to them, in actual rings some of the nodes may just be repeaters. The reader who wishes to refer to a further treatment should consult [5].

## 5.3. Token passing

In this type of network access to the transmission medium is by means of a token which is passed from station to station according to some set of rules set up by the network designer. A station can only transmit when it is in possession of the token. When a node has finished transmitting it passes on the token to the next node in a sequence which places all the nodes of the network onto a logical ring, though the medium itself need not be a ring. As with slotted rings it is

necessary to provide suitable functions for initialisation, error recovery and monitoring the logical ring. In particular it is crucial to have procedures for restoring the token if it becomes corrupted.

With token networks the packets can be of variable length and high line utilisations are possible (see papers by Bux in [3]), but it is necessary to provide complete packet buffers.

Work is currently being carried out on the use of tokens on bus topologies and this is still at an early stage of development. In contrast many ring networks have been and are based upon token passing. An interesting recent example is the IBM experimental token ring which is described in [4] in a paper by Bux and his co-authors. In this ring each station is a potential monitor, though of course there is only one of these in actual use at any given time.

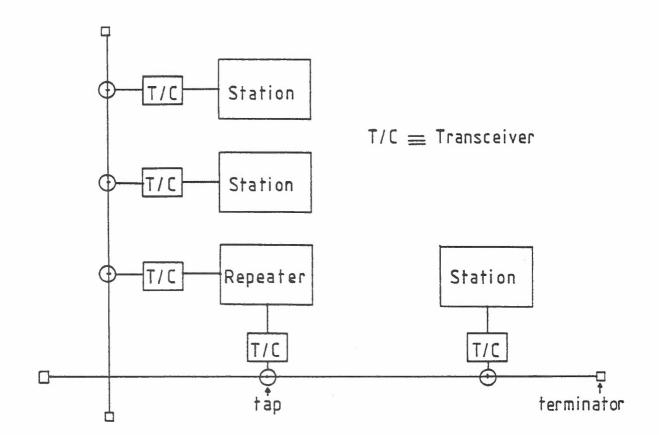

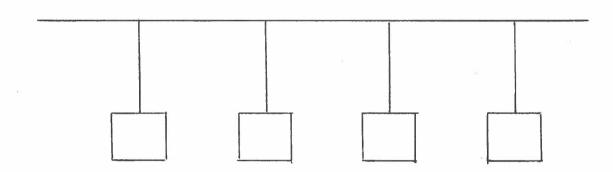

#### 5.4. Carrier sense multiple access

The so-called Carrier Sense Multiple Access (CSMA) technique is used in a number of networks including the Xerox Ethernet [2, 10]. It is an example of a broadcast media access method. In broadcast systems each connected device is at liberty to broadcast its information over the network. Since two transmissions occurring at the same time will result in the data being corrupted it is necessary to have arrangements to overcome this problem.

In CSMA each node of the network "listens" to see if any other nodes are transmitting. If this is the case then the node defers its transmission to a later time. If however the channel is free then it begins its transmission. However, since signals take a short time to travel along the network, it is possible for two nodes to transmit at almost identical times thus causing a collision. Therefore transmitting stations listen to the first part of the transmission. A collision will be detected and each station will then stop transmitting. They then wait for random time intervals and retransmit. Due to these random time intervals it is unlikely that the transmissions from these nodes will occur at the same time again. This is called collision detection and the usual abbreviation for this type of broadcast technique is CSMA/CD.

This basic technique may be implemented in various ways but it is usually done with coaxial cable where the single inner conductor is monitored for the presence or absence of signals.

The rules of the CSMA/CD technique imply that this type of network is probabilistic, i.e. there is no absolute guarantee that a transmission can be completed within a given time or that a station can transmit at a guaranteed minimum data rate. In practice this does not appear to be very restrictive and data communication response times are usually rapid.

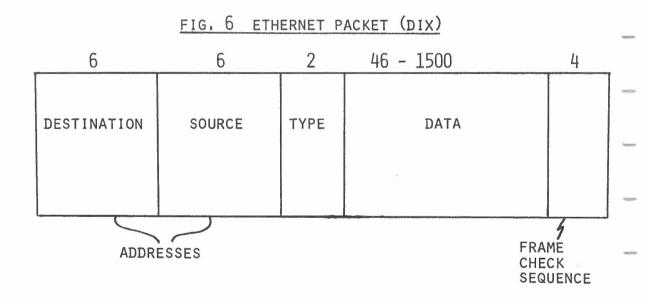

The information on an Ethernet is transmitted in a packet, the format of which is given in Fig 6.

#### 6. Comparative Issues

Comparisons are notoriously difficult and local networks are not an exception to this rule. However some trends appear to be coming clearer and we will now consider them.

The costs involved in local networks often only form part of a

total system cost and may in fact perhaps be less than 15%. One factor which is going to reduce costs and improve reliability is the availability of LSI components and these seem likely to become available in quantity during 1983, and they will then be speedily incorporated into products.

There are likely to be continual discussions about the relative merits of baseband and broadband systems. Each have their advantages, for example individual broadband channel speeds are currently limited in speed to some 10 to 12 megabits but there can be several of them. Much will depend upon developments in Frequency Agile Modems, which are used to attach devices to these channels. Another factor of importance in the U.K. is that there is less experience compared with the U.S. with the cable television technology (CATV) which is used with broadband networks, but voice and television transmissions can be carried out on a broadband network. On the other hand baseband speeds will probably increase past the 50/100 megabit range for rings using fibre optic cabling. A comparison between rings and other types of local network is given in [17].

Some of the points which are important when comparing networks are rather more down to earth and practical than some of the considerations above. Engineering and maintenance considerations are crucial in our view. From time to time things will go wrong and then faults will have to be speedily rectified. A lightning strike is one example of a phenomenon which has affected both ring and ethernet networks (with complete impartiality). Equally monitoring must be considered and embedded into the system in a suitable manner. Yet another important factor is that there is, as yet, only a small amount of feedback from customer sites.

These considerations lead one to the conclusion that it is too soon to start picking out outright winners in the local network field. Anyone contemplating the purchase of one of these systems would be well advised to avoid too many preconceived notions and to prepare a detailed specification of their requirements before starting detailed discussions with possible suppliers.

#### 7. Protocols for local and wide area networks

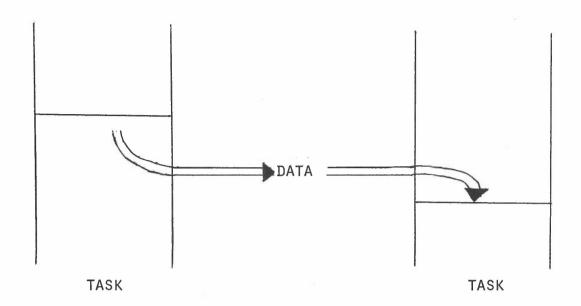

In this section we present some information about protocols, since these are a vital component in any local or wide area network. A protocol, standard, is necessary for the orderly exchange of information between computer processes. Without standard protocols it is impossible for systems from different suppliers or manufacturers to intercommunicate in an effective manner.

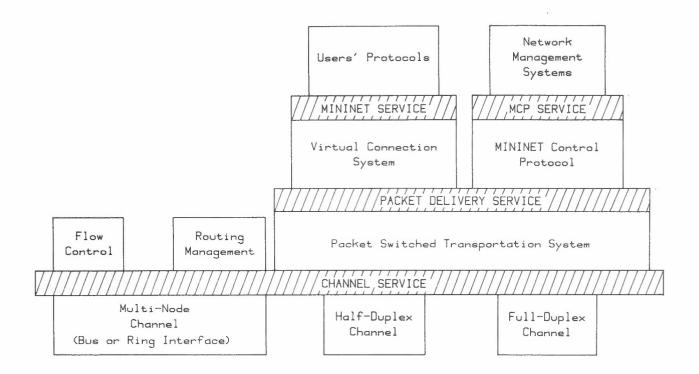

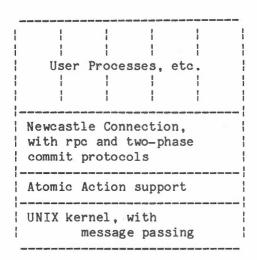

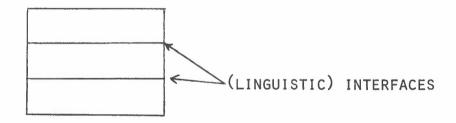

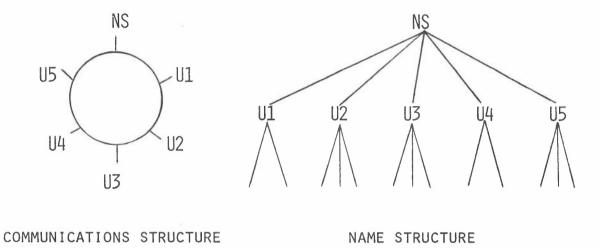

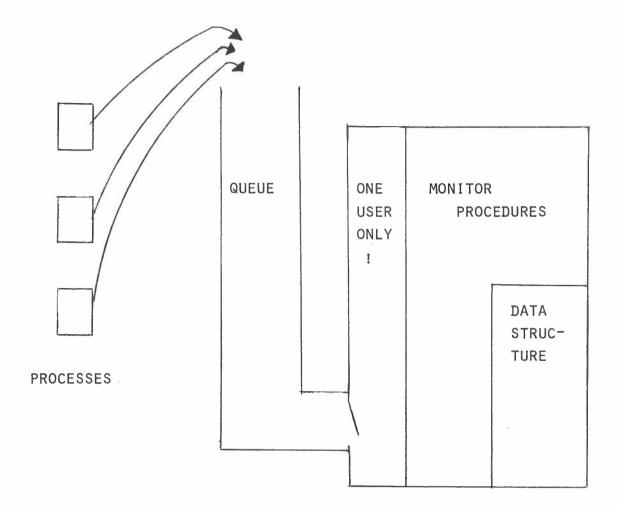

Most authorities now agree that these issues should be discussed within the framework of the Reference Model for Open Systems Interconnection which was put forward as a recommendation by the International Standards Organisation in 1978 (known as the ISO/OSI Reference Model), see [18]. Although it was originally intended for Wide Area Networks, many of the ideas apply also to local networks, see [7].

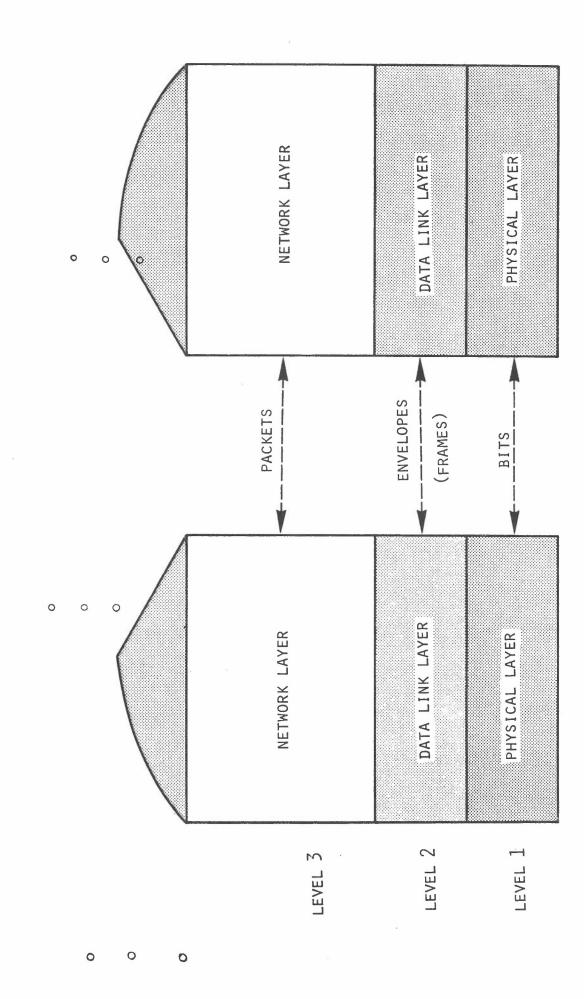

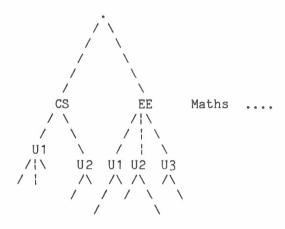

Essentially the proposal states that the communication issue should be addressed in terms of a seven-layer model as shown in Fig 7. Each of these layers provides a certain subject of services to the overall set of network functions which are required. In general each layer provides facilities to the modules (software or firmware) in the layers above. The physical link layer transfers the information as a stream of bits.

The data link layer structures this bitstream in order to provide an error-free communication path between two nodes. The network control layer sets up the path between nodes, routes, messages, errors, intervening nodes, addresses messages and controls the flow of messages between nodes.

The transport layer provides the end-to-end control of the communication session once the path has been established, allowing processes to exchange data reliably and sequentially. This is independent of which systems are communicating or their location in the network. The two layers above this are concerned with providing facilities for the applications layer, which provides services which support the actual user tasks. File and job transfer, terminal protocols and things like Electronic Mail are dealt with at about this conceptual level.

There are several important matters arising out of this model. Local network protocols do not conform exactly to the first three layers as discussed above. However it is generally agreed that any interconnections or gateways between local and wide area networks should be at the Transport level which enables the essential end to control issue to be resolved. In this connection it will be recalled that the British Telecom PSS (or Switchstream 1) service essentially uses the first three layers in the form of the CCITT X25 standard protocol. Provided the Transport level has been suitably implemented on the Local Network it is then feasible to use the <a href="mailto:same">same</a> higher level protocols (or layers) on both local and the wide area networks. Whilst this may not be appropriate for all applications; and in particular for certain types of distributed computer system, nevertheless it does provide the means to effectively interconnect wide area and local networks. So that for example files may be transferred between the two systems.

The Academic community in the U.K. has standardised on high level protocols (i.e. protocols above level 3) for wide area networks pending developments in International Standards, called the Coloured Book protocols. Namely

Yellow Book, Transport Layer. Blue Book, File Transfer.

Red Book, Job Transfer and Manipulation.

Green Book, TS29 Terminal Protocol.

Gray Book, Electronic Mail.

These are gradually being introduced for interconnection between community sites using either the Science Engineering Council Network (SERCNET) or the British Telecom PSS/Switchstream 1 service. Some of these sites, for example the University of Kent, have Cambridge Ring local networks and the coloured book protocols will also be used on them. It seems likely that the same developments will take place for Ethernets or other local networks on community sites.

However below the transport level the protocols for Cambridge Rings or Ethernets differ from the ISO/OSI model, there are several reasons for this. In particular the transient error rates are much lower (by three or four orders of magnitude) than in a typical wide area network, so with the higher speeds which are available in the local network case it is practical to correct these at a higher level rather than level two. Also addressing problems tend to be much simpler. Some details of the Cambridge Ring protocols at these levels are given in [5 and 14].

#### 8. Standards for Local Networks in the U.K.

Two of the most important standard developments affecting the U.K. are CR82 (see [13]) for Cambridge Rings and the forthcoming U.S. IEEE802/DIX/ECMA standard for Ethernets. Though at the present time both of these have de-facto rather than genuine standard status.

As its name implies CR82 emerged in 1982 as a result of discussions between the four U.K. suppliers of Cambridge Ring components namely Logica-VTS, Orbis/Acorn, SEEL, Toltec, together with the Science Engineering Research Council and the Joint Network Team. The latter organisations acting on behalf of the academic community. There were two consequences arising from this development. Firstly, there was a change from a 38 bit to a 40 bit minipacket by adding 2 additional control bits (Fig 5) and any equipment supplied to the CR82 specification from one of the firms above will interwork with CR82 equipment obtained from any of the others. Whilst CR82 has not been approved by the British Standards Institute (or BSI) nevertheless it is a significant step forward.

It seems unfortunate that it did not prove possible to get CR82 considered by the European Computer Manufacturers Association (ECMA) or the IEEE802 Local Network Standard Committee set up by the Institute of Electrical and Electronic Engineers in the U.S.

The CR82 definition covers only hardware. Specifications for protocol layers above this have been prepared by working groups set up by the JNT, as discussed in a previous section. Details of this are given in [14].

Although Cambridge University and Ferranti collaborated over the design of an LSI version of the principal Cambridge Ring components to a slightly enhanced version of the CR82 standard, using Uncommitted Logic Array techniques, this has not come into widespread use. It seems likely to be superseded during 1983 by an LSI version commissioned by the SERC. There are of course significant advantages for everyone once the components are engineered in silicon. For example reliability is superior and the standard status is much clearer.

The Ethernet position is rather different, the original design was carried out by Metcalfe and Boggs [16] of the Xerox Corporation at Palo Alto Research Centre (Xerox Parc) as part of a project work on Offices of the Future. Subsequently the specification of a revised version was agreed with the Digital Equipment Corporation (DEC) and Intel, and this was published in August 1980. Each partner in this grouping brought distinct advantages to the exercise, for example, Intel was to develop an LSI version of the Ethernet components whilst DEC had expertise in systems, micro mini computers and mainframes. DEC, Intel and Xerox are referred to as the DIX group in what follows. This specification was widely circulated, and it was possible for other firms to obtain a manufacturing licence for a reasonable fee. The hope of the DIX group was that other firms would use the specification to build compatible equipment and to a large extent this is what happened.

The original DIX standard (see [10]) did not cover any software protocol layers, however Xerox have themselves defined such facilities and the ECMA input to IEEE802 has also resulted in a proposal for the higher protocol levels. These are not compatible with the Rainbow protocols, in particular the Transport level is somewhat wider in scope than the comparable Yellow Book Transport Service. Nevertheless the

difference between these two levels is not large and it would be feasible to consider using the higher level Rainbow protocols on both Cambridge Rings and Ethernets. It is of course likely that many users of these networks will wish to define their own protocols for specific applications, particularly if the corresponding local networks are closed, i.e. they are entirely self contained and do not communicate with other networks.

In parallel with the DIX developments the IEEE in the U.S. set up a Local Network specification group know as the IEEE802 Committee and the DIX Ethernet specification was submitted to this body.

However the DIX Ethernet specification did not emerge as a recommendation of the IEEE802 committee, though considerable discussion ensued. In the meantime ECMA was considering Local Networks and came down in favour of a similar system which was backed by a large number of firms in the computer industry including ICL and CTL. ECMA then entered into discussions with IEEE802 and the DIX group. Late in 1982 all three bodies agreed upon a final version of the specification for submission to the IEEE. LSI versions have been developed by several suppliers and should be available in quantity during 1983. The reader should note that the IEEE802 work deals with other types of Local Network, specifically token rings and busses.

Although there are many Local Network products being marketed in the U.K. it is our view that careful attention should be paid to these two "standards". We have excluded discussion on local networks running at speeds lower than 10 megabits per second but it should be noted that there are several interesting products, e.g. the Acorn Econet which is a simple type of Ethernet, but currently only appears to connect Acorn systems. Another example is the Clearway system which is marketed by Real Time Systems Ltd, which may be used to interconnect equipment from different suppliers. It is a simple, effective and low cost system.

The reader who is interested in developments in U.K. standards and local networks should consult the recent report to the Focus Committee on Information Technology standards which is available from the Department of Industry. This contains recommendations on future work and in particular considers Electronic Telephone exchanges and their relation to local networks [11].

## 9. Current work in the U.K.

A substantial amount of the local network research and development effort in the U.K. is going into Rings. For example, research on high speed slotted rings is being carried out at Cambridge. Several Universities (Cambridge, Loughborough, University College London) are cooperating with British Telecom, Logica, GEC-Marconi on the Universe project. This is studying the possibilities opened up by interconnecting Cambridge Rings by means of a communications satellite using 1 megabit per second links, supplemented by normal terrestrial network connections. A general description of the status of this work during early 1982 is given by Kirstein et al in [8]. This reference also contains four specialist papers on the Universe project dealing with protocol architecture, encryption, network measurement and authentication.

There are a number of projects being carried out in the SERC Distributed Computing Programme all using the Cambridge Ring as a standard research vehicle, these include

| Needham, R.M.                            | Cambridge                        | Developments of the Cambridge Ring                                                                                                   |

|------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| K.H. Bennett                             | Keele                            | A Distributed Filestore                                                                                                              |

| H. Brown, S.E. Binns and D.J. Caul       | Kent                             | Typesetting and Text<br>Processing Servers for<br>the Cambridge Ring                                                                 |

| P.J. Brown and P.H. Welch                | Kent                             | Compiling Servers for the Cambridge Ring                                                                                             |

| B. Randell                               | Newcastle                        | Reliability and Integrity<br>of Distributed Computing<br>Systems                                                                     |

| C.A.R. Hoare, Stoy, J.E. and Harper M.K. | Oxford                           | Distributed Computing<br>Software                                                                                                    |

| R. Bornat                                | Queen Mary<br>College,<br>London | Pascal-M: A language for<br>the design of Loosely-Coupled<br>Computer Systems                                                        |

| D. Hutchinson and W.D. Shepherd          | Strathclyde                      | Direct Comparison of Ring and Ethernet Type Systems. Gateways for the Interconnection of Cambridge Rings and Ethernet-like networks. |

| J.W. Hughes and M.S. Powell              | UMIST                            | Multiprocessor Software<br>Engineering                                                                                               |

| P.T. Kirstein                            | University<br>College,<br>London | Communication Protocols in<br>the context of X25 Computer<br>networks                                                                |

| I.C. Wand                                | York                             | Operating Systems for a<br>Network of Personal<br>Computers                                                                          |

Further details are given in the Annual Reports from the SERC on Distributed Computing Systems.

The University of Strathclyde has an SERC Research grant for a comparative study on Cambridge Ring and Ethernet Type local networks. This work will also involve the developments of a gateway between these two networks. This is worth noting in view of the likely importance of these two technologies in the U.K. and the fact that some organisations may be involved with both of them. One University carrying out work on broadband systems is Sussex, and this includes the development of frequency agile modems and an Ethernet channel.

Kent, Leeds and Oxford are working on development contracts from the JNT on Cambridge Rings. Kent are tackling terminal concentrators, ring to ring bridges, reconfiguration and monitoring. The work at Leeds and Oxford involves different types of fibre optic cabling, whilst Oxford are also working on printer servers and micro computer interfaces. Other JNT projects on Ring interfaces involving both hardware

. .

and software, for several different computer systems including Prime, DEC Vax (Unix and VMS) and GEC4000, are being carried out on collaborative projects involving Universities, Polytechnics and Industry. It is interesting to note that these interfaces will operate at the Transport level. Other developments have been carried out at the Edinburgh Regional Computer Centre which include improved version of ring components and micro and minicomputer interfaces. It is anticipated that most of the items described in this paragraph will be marketed.

#### 10. Local networks which are available in the U.K.

There are four firms currently active in the Cambridge Ring field, Logica VTS, Orbis, SEEL and Toltec. Logica supplied the original SERC Rings and has just announced a fibre optic ring cabling product, and has also developed a fileserver. SEEL are working on fibre optics and ways of increasing reliability by duplicating certain components. It will be recalled that these firms all supply ring components to the CR82 standard.

Some twenty companies have made a commitment to the ECMA "Ethernet" local area standards and since these will eventually be compatible with the IEEE802 and DIX standards, there is likely to be considerable effort put in by the relevant U.K. companies who include ICL, Computer Technology Ltd (CTL, NTL and OTL) and this implies work on both baseband and broadband systems.

An interesting U.K. developed local network system is available from Xionics Ltd. Their system consists of two networks in one - there is the Xinet ring network to which minis, mainframes and word processors are connected using so-called intelligent sockets. The network allows for 4095 addresses using 256 byte packets. With 16 bytes reserved for error checking, addressing, and flag data. Hogging is avoided by letting each intelligent socket have a packet of its own.

The Xinet is attached to the Xibus which is a closely coupled network of processors which manage disc stores and carry out monitoring functions (as in the Cambridge Ring). There is extensive duplication within the Xionics system as regards cabling, power supplies and discs, to provide a high degree of redundancy.

Several networking type interfaces are available and others are planned, e.g. Telex, Ceefax, Oracle, the interconnection of Xionics systems, PSS and mainframes from suppliers such as IBM, ICL and DEC. The standards position is not entirely clear with this network and it appears to be a closed system with gateways providing any required compatibility with other systems.

The general picture which emerges is that of a rather limited number of installations during 1982, which is likely to increase enormously in 1983.

#### 11. Some current applications of networks

Local networks are being used in the academic community in at least two different ways. Many sites are using them as research vehicles for work on Distributed Computing, whilst others are using them as the basis for the provision of a computer service. An example of the former is the University of Cambridge who also provide a departmental computing service. A detailed description of this system which is based upon the Cambridge Ring, is given in [5]. Perhaps the main characteristic of

this work is that users of the system access banks of processors attached to the network from terminals relying on a shared filestore (or fileserver) on a separate node. There is no local filestore directly attached to the terminal or the processors. On the other hand the University of Kent based their computer service on a Cambridge Ring network service in January 1980. This has enabled a considerable rationalisation in the communication facilities. (Spratt [8]) describes the current state of this system and (Spratt [3]) contains an account of earlier work. Another example of a University which has based part of its computer service on this type of network is the Regional Computer Centre at Edinburgh. University College, London is using Cambridge Rings both in their research work and in their provision of gateway facilities to ARPANET for SERC Research Workers.

Very few Ethernet systems appear to be in actual use within Universities or Polytechnics during the last quarter of 1982. Apart from the work at Strathclyde mentioned earlier. However it is clear that this situation will change in 1983 as firm plans are known to exist at a number of sites.

The situation in the non-academic community is less clear. In general it appears that a number of baseband and broadband networks have been installed by U.K. firms essentially based on imported product mainly from the U.S., these systems often provide Ethernet facilities. Examples of this are Thame Systems and Case, who are using Ungermann Bass Net One equipment, and Network Technology Ltd who are using Sytek systems. A number of these systems are being installed under a government sponsored programme concerned with Office Automation. Some Ethernets have been installed by Xerox, in particular for the Greater London Council. Xionics have installed a number of systems including one in the Cabinet Office.

The four CR82 Cambridge Ring suppliers each have an installed user base, with Logica taking a leading role in respect of customers outside the U.K. Other firms have developed other types of ring, e.g. Racal with their Planet system which was announced during 1982.

#### 12. Networks Users Association Survey

This is basically a U.S. organisation and some of the results of a recent survey on local networks as reported in the Localnetter Newsletter (see References-reports) are summarised below.

| Q1:  | Responding Organisation Class Miscellaneous End Users Banking Government Education Manufacturing          | ssification.<br>41.5<br>18.4<br>16.1<br>12.0<br>12.0                                                              |

|------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Q2:  | Application of networks under<br>Host Access<br>Office Automation<br>Intra Data Centre<br>Manufacturing   | er following four categories<br>37.6<br>32.8<br>19.8<br>9.8                                                       |

| Q3:  | Broadband Baseband PBX Ring/Loop Note. This is a rather odd                                               | er following four categories 37.7 27.9 19.6 14.7 question, presumably the Ring/Loop f 42.6 is the important point |

| Q4:  | Media Access Technique prefe<br>CSMA/CD<br>Don't Care<br>Token<br>Don't know                              | erence<br>32.9<br>30.5<br>20.2<br>16.4                                                                            |

| Q5:  | Type of Access required<br>Statistical (Contention)<br>Don't care<br>Guaranteed                           | 40.3<br>37.0<br>22.7                                                                                              |

| Q6:  | Preferred Local Network typ<br>Baseband/CSMA-CD<br>Broadband/CSMA-CD<br>Baseband/Token<br>Broadband/Token | e<br>44.8<br>29.5<br>15.4<br>10.3                                                                                 |

| Q7:  | Traffic Types Data and Graphics Data only Data/Graph/Video All four                                       | 45.7<br>25.1<br>17.2<br>12.0                                                                                      |

| Q8:  | LN Compatibility Requiremen<br>Multiple Vendor<br>Single Vendor                                           | ts<br>69.1<br>30.9                                                                                                |

| Q9:  | Gateway requirements Dissimilar Networks Similar Networks Both                                            | 46.2<br>34.9<br>18.9                                                                                              |

| Q10: | LN Standard requirements<br>Yes<br>No                                                                     | 93.5<br>6.5                                                                                                       |

Whilst this survey is not definitive it does provide very useful information on the requirements and interests of local network users. In particular standardisation and multiple vendors appear very important issues. It would also appear that many users are not particularly worried about the baseband v broadband or CSMA/CD v Token Passing type of debate. More information is given in the December issue of the Localnetter Newsletter.

#### 13. Conclusions

Local networks cover a wide variety of systems and we have concentrated upon those which have reasonably high speeds at the present time. The situation in the U.K. over the next few years seems likely to be heavily influenced by the recent Ethernet standard discussed earlier and Cambridge Rings and other Ring based systems such as those from Xionics and perhaps Racal. It will be interesting to assess the Universe project when this is completed but early reports appear to be most encouraging.

One of the most important factors behind these developments is the emergence of LSI components for most of the local network hardware. This will bring the benefits of stability, reliability and low costs to users of these systems particularly for baseband systems. Ethernet CSMA techniques however are applicable on Broadband based systems though here the advantages of LSI may take longer to appear. Additionally there are speed restrictions on Baseband Ethernets which do not apply to rings, and the latter also have a distinct advantage in relation to the straightforward use of fibre optics.

If this mixed Ethernet/Ring scenario proves valid, then it will be important to have gateways between these networks. The SERC initiative at the University of Strathclyde is important in this context. As further developments in rings are carried out in the U.K. thus it will be crucial to put them into silicon at the appropriate time, test them out and tackle the international standards scene in a determined manner; speeds in the 50/100 megabit range appear quite feasible.

Another matter which may become important is that of encryption particularly for security purposes and the work at the National Physical Laboratory and in the Universe Project is pertinent in this regard.

In a more speculative vein it will be interesting to see if IBM decide to market a local area network product. As stated earlier they have published material on an experimental token ring [4] and this has been submitted to the IEEE802 committee. A possible complication is the patent position on token rings which may affect the attitude of the standards bodies.

A comment upon recent developments in Japan is perhaps in order. At least three companies, including Fujitsu and NEC, have announced local area network products involving fibre optic token ring, at speeds in the range 18 to 30 megabits per second, some of these can cover large distances, e.g. up to 100 kms, which is far in excess of the 3/4 kms diameter local networks given in our definition earlier in this paper.

In conclusion it appears that Local Networks are being increasingly used, we should have some stability once the LSI versions are available in 1983, though developments will certainly continue. Finally some standards de-facto are beginning to emerge.

#### 14. REFERENCES

#### Open Literature

- 1 Flint, D., The Data Ring Main, John Wiley, 1983 (to appear)

- 2 Local Area Networks (Report to Focus Committee), Department of Industry, London, 1982

- West, A., and Janson, P. (eds), Local Networks for computer communications, North Holland, 1981

- Ravasio, P.C., Hopkins, G. and Naffah. N., Local Computer Networks, North Holland, 1982

- Needham, R.M., and Herbert, A.J., The Cambridge Distributed Computing System, Addison-Wesley, 1982

- 6 Spratt, E.B., Local Area Networks: Management and Quasi-Political Issues, Proc ICCC82 (see Williams, M.B.)

- 7 Tannenbaum, A., Computer Networks, Prentice-Hall, 1982

- 8 Williams, M.B. (ed), Pathways to the Information Society, Proceedings of the Sixth International Conference on Computer Communication, North Holland, 1982

- 9 Local Networks and Distributed Office Systems, On line Conferences, 1981

- The Ethernet, A Local Area Network-Data Link Layer and Physical Layer Specification, 30/9/80 (Digital, Intel and Xerox).

- 11 Local Area Networks. Report to the Focus Committee. Department of Industry, August 1982.

- 12 Clark, D.D., Program K.T. and Reed, D.P., "An introduction to local area networks", Proc IEEE, 66, 11, Nov 1978.

- 13 Cambridge Ring 82 Interface Specification

- 14 Cambridge Ring 82 Protocol Specification, Nov 1982

- 15 Rainbow Protocols

Green Book TS29 Terminal Protocol

Red Book Job Transfer and Manipulation Protocol

Yellow Book Transport Service

Blue Book File Transfer Protocol

Gray Book Electronic Mail

Note. Copies of the references 13, 14 and 15 may be obtained from:

Joint Network Team,

SERC Rutherford Appleton Laboratory,

Didcot

Oxfordshire

- Metcalfe, R. and Boggs, D., "Ethernet: Distributed Packet Switching for Local Computer Networks", CACM 19, 1976.

- 17 Saltzer, C., Clark, D.D. and Pogran, K., "Why a Ring", Proc 7th Data Communications Symposium, Mexico City, Oct 1981.

- 18 ISO 7498 Data Processing Open Systems Interconnection-Basic Reference Model obtainable from:

British Standards Institution 2, Park Street London W1A 2BS

#### Consultancy Reports

Local Area Networks,

Xephon Technology Transfer Ltd, 1981

Kings House,

King Street,

Maidenhead,

Berkshire SL6 1EF

Localnetter Designers Handbook, 1982 Localnetter Newsletter (published monthly) - both available from:

Architecture Technology Corporation, P.O. Box 24344 Minneapolis, Minnesota 55424, U.S.A.

Yankee Group Report on Local Communications, C/IS Communications/Information Systems, Regal House, Lower Road, Chorley Wood, Rickmansworth, Herts.

FIG. 1 COMPUTER NETWORKS

FIG. 2 TYPICAL LOCAL NETWORK NODE

. . . . . .

FIG. 3 TOPOLOGIES

FIG 4 CAMBRIDGE RING NODE

FIG. 5 CAMBRIDGE RING PACKET

UNITS OF BITS

UNITS OF BYTES (OCTETS)

| APPLICATION        | ·   |             | CAN                                    |

|--------------------|-----|-------------|----------------------------------------|

| PRESENTATION       |     |             | BE AS IN WAN                           |

| SESSION            |     |             | CASE                                   |

| TRANSPORT          |     |             | TRANSPORT<br>SERVICE<br>BYTE<br>STREAM |

| NETWORK<br>CONTROL | a . |             | PROTOCOL                               |

| DATA LINK          |     | BASIC BLOCK |                                        |

| PHYSICAL           |     | PHYSICAL    |                                        |

FIG. 7 ISO/OSI REFERENCE MODEL AND LOCAL NETWORKS SPECIFIC EXAMPLE OF A CAMBRIDGE RING

. .

SERC INDUSTRIAL DISTRIBUTED

COMPUTING SYSTEMS CONFERENCE

# RINGS AND THINGS

BRIAN SPRATT

DIRECTOR, COMPUTER LABORATORY

UNIVERSITY OF KENT

- PERSONAL VIEWS

- EMPHASIS ON DEVELOPMENTS IN ACADEMIC COMMUNITY

- UNIVERSITIES

- POLYTECHNICS

- SCIENCE AND ENGINEERING RESEARCH COUNCIL (SERC)

# TWO TYPES OF COMPUTER NETWORK

- LOCAL

- WIDE AREA

LOCAL: DIAMETER UP TO 2/3 KM

TOTAL DATA RATE > 1 MEGABIT PER SEC

OWNED BY ONE ORGANISATION

WIDE AREA: CAN BE INTERCONTINENTAL

TYPICAL DATA RATE ~9600 BITS PER SEC

INVOLVE PTT'S (EG BRITISH TELECOM)

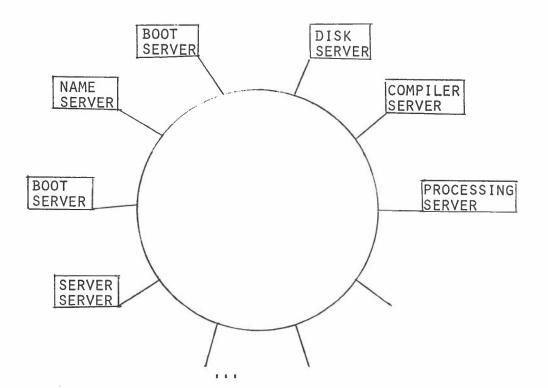

# WHY ARE LOCAL NETWORKS IMPORTANT?

1) REQUIRED TO EXPLOIT ADVANTAGES OF FUNCTIONALLY DISTRIBUTED COMPUTING

COMPUTERS IN NETWORK DEDICATED TO SPECIFIC FUNCTIONS

- TERMINAL HANDLING

- DATA BASE MANAGEMENT

- STORAGE OF FILES

- PRINTING

- CONTROLLING PROCESS CONTROL EQUIPMENT

REASON FOR RELEVANCE TO SERC DCS PROGRAMME

## 2) USED TO INTERCONNECT

COMPUTERS

TERMINALS

PERIPHERALS (EG PRINTERS)

WORK STATIONS

REMOTE/LOCAL FACILITIES

CAN BE USED AS BASIS OF A COMPUTER SERVICE FOR TEACHING/ RESEARCH/ADMINISTRATION

JOINT NETWORK TEAM

SERC

COMPUTER BOARD

DEVELOPMENT PROGRAMME

- STANDARDS

BANDWIDTH NOT SCARCE RESOURCE

# SERC COMMON BASE POLICY

FORTRAN 77

PASCAL

GEC 4000 } MINICOMPUTERS

ICL PERQ WORKSTATIONS

CONNECTED BY

CAMBRIDGE RING LOCAL NETWORKS

WHICH IN TURN ARE INTERCONNECTED USING WIDE AREA NETWORKS

## 4 NODE LOCAL NETWORK

CABLE

TWISTED PAIR COAXIAL FIBRE OPTIC

STANDARD LOGIC

DEVICE SPECIFIC LOGIC

DEVICE

TYPICAL NODE ON LOCAL NETWORK

PROTOCOL: PRECISE SET OF RULES ENABLING COMPUTERS TO

COMMUNICATE EFFECTIVELY

# TECHNOLOGIES FOR LOCAL NETWORKS

## MEDIA - SERIAL TRANSMISSION

- CABLING

- BROADBAND AND BASEBAND

- PASSIVE

- NETWORK LAYOUT

SLOTTED RINGS

TOKEN PASSING

CARRIER SENSE MULTIPLE ACCESS (CSMA)

## CABLING

TWISTED PAIR

COAXIAL

FIBRE OPTIC

- ENVIRONMENT

- BANDWIDTH

- NOISE IMMUNITY

- ENGINEERING/INSTALLATION ISSUES

#### BASEBAND

SINGLE SIGNALLING CHANNEL

ACCESS SIMPLE

SPEEDS 10-30 MEGABITS/SEC

100 MEGABITS / SEC UPWARDS FEASIBLE

## **BROADBAND**

SEVERAL SIGNALLING CHANNELS

ACCESS COMPLEX - FREQUENCY AGILE MODEMS

CHANNEL SWITCHERS

CHANNEL SPEEDS 10 MEGABITS/SEC

CABLE TELEVISION TECHNOLOGY (CATV)

# PASSIVE OR ACTIVE

# NETWORK LAYOUT

NETWORK TOPOGRAPHY

WIRING

NETWORK TOPOLOGY

LOGICAL LINKS

MANAGEMENT RELIABILITY

MAINTENANCE

# SLOTTED (CAMBRIDGE) RING

MONITOR NODE

NO HOGGING

NO SWAMPING

# TOKEN PASSING

- HAVE TO POSSESS TOKEN TO TRANSMIT

- LOGICAL RING

- RINGS

VARIABLE LENGTH PACKETS

GOOD LINE UTILISATION

• BUSES (IEEE80Z)

# CARRIER SENSE MULTIPLE ACCESS (CSMA)

BROADCAST

COAXIAL CABLE

COLLISION DETECTION

PROBABILISTIC

ETHERNET (CF ALOHA)

# COMPARATIVE ISSUES

- DIFFICULT

- POSSIBLE TRENDS

- # LOCAL NETWORK FORMS ONLY SMALL (BUT VITAL) PART OF TOTAL SYSTEM COST

- # AVAILABILITY OF LSI COMPONENTS WILL REDUCE LN COSTS

- # BASEBAND V BROADBAND

BASEBAND SPEEDS WILL INCREASE

FIBRE OPTIC TECHNOLOGY

CATV - FREQUENCY AGILE MODEMS

BROADBAND - VOICE

BUT PABX DEVELOPMENTS

- # ENGINEERING / MAINTENANCE

- # MONITORING / MANAGEMENT

- # SPECIFY REQUIREMENTS CAREFULLY

## PROTOCOLS FOR LOCAL AND WIDE AREA NETWORKS

PROTOCOL - USED TO PROVIDE FOR AN ORDERLY EXCHANGE OF INFORMATION BETWEEN COMPUTER PROCESSES

- STANDARDS

- REFERENCE MODEL FOR OPEN SYSTEM INTERCONNECTION (OSI)

INTERNATIONAL STANDARDS ORGANISATION (ISO)

7 LAYER MODEL

DEVISED IN A WIDE AREA CONTEXT, BUT IDEAS VALID IN LOCAL NETWORKS

| APPLICATION  |   |                              | CAN                  |

|--------------|---|------------------------------|----------------------|

| PRESENTATION |   |                              | BE AS<br>FOR<br>WIDE |

| SESSION      |   |                              | AREA                 |

| TRANSPORT    |   | TRANSPORT<br>SERVICE<br>BYTE |                      |

| NETWORK      |   | STREAM                       |                      |

|              |   | BASIC BLOCK                  |                      |

| DATA LINK    |   | RING                         |                      |

| PHYSICAL     |   | HARDWARE                     | -                    |

| THISTCAL     |   | _                            |                      |

| $\uparrow$   |   |                              |                      |

| WIDE AREA    |   | LOCAL                        |                      |

|              | 1 | (CAMBRIDGE RII               | NG)                  |

- BRITISH TELECOM SWITCHED STREAM 1 (PSS) SERVICE X25 (CCITT) LEVELS 1 TO 3

- CAMBRIDGE RING PROTOCOLS GIVEN AS EXAMPLE NOT EXACTLY AS

FOR WIDE AREA CASE AT LOWER LEVELS

ISO/OSI REFERENCE MODEL, WIDE AND LOCAL AREA NETWORKS

## ACADEMIC COMMUNITY PROTOCOLS

### COLOURED BOOK PROTOCOLS (RAINBOW SERIES)

YELLOW BOOK

TRANSPORT SERVICE

BLUE BOOK

FILE TRANSFER

RED BOOK

JOB TRANSFER AND MANIPULATION

GREEN BOOK

TS29 TERMINAL PROTOCOL

GREY BOOK

ELECTRONIC MAIL

ORANGE BOOK

CAMBRIDGE RING PROTOCOLS

ETHERNET POSITION

ERROR RATES ON LOCAL NETWORKS

# "STANDARDS" FOR LOCAL NETWORKS IN THE U.K.

DEVELOPMENTS:- CR82 CAMBRIDGE RING

IEEE802/DIX/ ETHERNETS

ECMA

CR82 AGREED RING COMPONENT SUPPLIERS ACADEMIC COMMUNITY

ACORN/ORBIS

LOGICA / VTS

SEEL

TOLTEC

LSI VERSION ~ LATE 1983

**IEEE802**

ECMA - EUROPEAN COMPUTER MANUFACTURERS ASSOCIATION

ICL, CTL (OTL, NTL)

# ACORN - ECONET

REAL TIME SYSTEMS LTD - CLEARWAY

INEXPENSIVE, LOW SPEED - STANDARDS?

**EXAMPLES OF DEVELOPMENTS**

## CURRENT WORK IN U.K. - SERC

RINGS

- CAMBRIDGE HIGH SPEED SLOTTED RINGS

- UNIVERSE PROJECT

CAMBRIDGE

UNIVERSITY COLLEGE, LONDON

LOUGHBOROUGH

BRITISH TELECOM

GEC MARCONI

INTERCONNECTION OF CAMBRIDGE RINGS USING SATELLITE PLUS TERRESTRIAL LINKS

DISTRIBUTED COMPUTER SYSTEMS RESEARCH

CAMBRIDGE

KEELE

KENT

**NEWCASTLE**

OXFORD

QMC, LONDON

STRATHCLYDE

UMIST

UCL, LONDON

YORK

RINGS AND ETHERNETS COMPARATIVE STUDY + GATEWAY STRATHCLYDE

BROADBAND NETWORK SUSSEX

# RINGS (CONTINUED)

## JOINT NETWORK TEAM CONTRACTS

TERMINAL CONCENTRATORS

RING-RING BRIDGES

RECONFIGURATION

MONITORING

**KENT**

FIBRE OPTIC LINKS PRINTER SERVERS

**OXFORD**

RING INTERFACES FOR VAX/UNIX

VAX/VMS

GEC 4000

RING COMPONENTS

EDINBURGH REGIONAL COMPUTER CENTRE

## LOCAL NETWORKS AVAILABLE IN U.K.

CAMBRIDGE RINGS

LOGICA - VTS

FIBRE OPTIC PRODUCT

FILESERVER

SEEL

CABLE DUPLICATION

ORBIS

TOLTEC

"ECMA ETHERNET"

DIX/IEEE802

ICL

LARGELY IMPORTED

BASEBAND + BROADBAND

XIONICS RING

XIBUS - CLOSE COUPLED

XINET - LOCAL NETWORK

INTERFACES TO PSS

MAINFRAMES (IBM, ICL, DEC)

RACAL - PLANET

LIMITED NUMBER OF INSTALLATIONS 1982

MANY MORE 1983

## CURRENT APPLICATIONS

- ACADEMIC COMMUNITY

- RESEARCH VEHICLES FOR WORK ON DISTRIBUTED COMPUTING

- BASIS OF COMPUTER SERVICES

CAMBRIDGE

KENT

RINGS APART FROM STRATHCLYDE

SUSSEX

EDINBURGH

NON ACADEMIC COMMUNITY

INSTALLATIONS BASED ON IMPORTED PRODUCTS - "ETHERNETS"

- THAME AND CASE

(UNGERMANN BASS NET ONE)

- CTS (SYTEK)

- XEROX

OFFICE AUTOMATION - GOVERNMENT SCHEMES

# USER SURVEY

- STANDARDISATION

- MULTIPLE VENDORS

- BASEBAND V BROADBAND

- CSMA/CD V TOKEN PASSING

# CONCLUSIONS

## U.K. SITUATION HEAVILY INFLUENCED BY

- CR82

IEEE802/DIX/ECMA 'ETHERNET"

XIONICS

RACAL

- LSI COMPONENTS

- GATEWAYS FOR INTERWORKING

- # NEED FOR MORE U.K. ACTIVITY ON #

INTERNATIONAL STANDARDS

IBM

TOKEN RING

**JAPAN**

**FUJITSU**

NEC

FIBRE OPTIC TOKEN RINGS

18 - 30 MEGABITS/SEC

UP TO 100 KMS

LOCAL NETWORKS INCREASINGLY USED

SOME STABILITY WITH LSI

STANDARDS EMERGING

#### **EVALUATING LOCAL AREA NETWORKS**

Doug Shepherd

Computer Science Department

University of Strathclyde

#### 1.Introduction

The past two years have seen a large increase in the commercial availability of local area networks. These systems are usually based on one of the following three architectures:— slotted ring, CSMA collision detection bus, or token ring. Examples of each type are the Cambridge Ring, Standard Ethernet and MIT's token ring respectively. A number of papers have appeared describing these architectures [1,2,3] and the paper by Spratt[4] gives a good overview of the systems available. Most of the manufacturers make similar claims for the performance and versatility of their local area networks and it is the purpose of this paper to present a cross section of the work that has been carried out in evaluating the performance of various local area networks. It is not our intention to give an exhaustive review of the literature but rather to select one or two results that will give the reader some feeling for the relative merits of the various local area network architectures.

In the first part of the paper we look at modelling, both analytical and simulation, in the second part we present some actual performance measurements for the Ethernet and Cambridge Ring respectively, in the third part we discuss other factors that should be considered besides performance, and finally we draw appropriate conclusions.

#### 2.Modelling

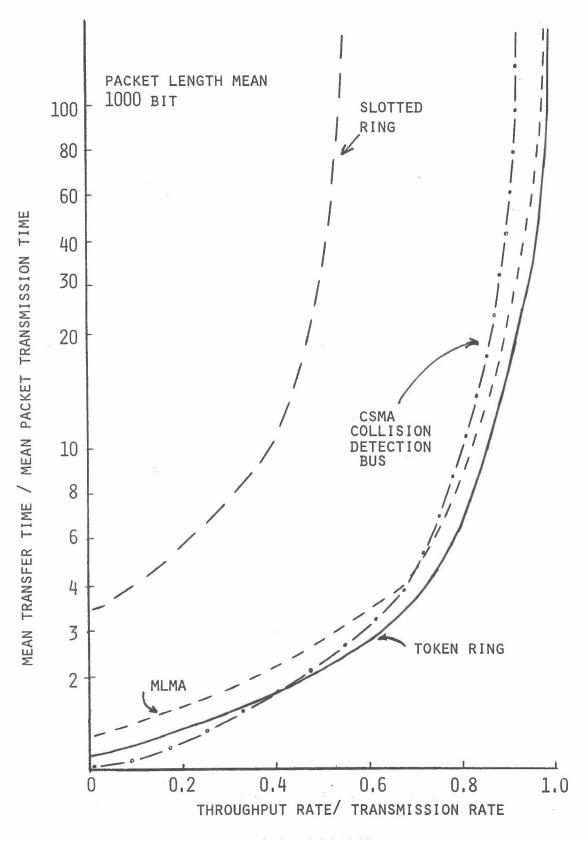

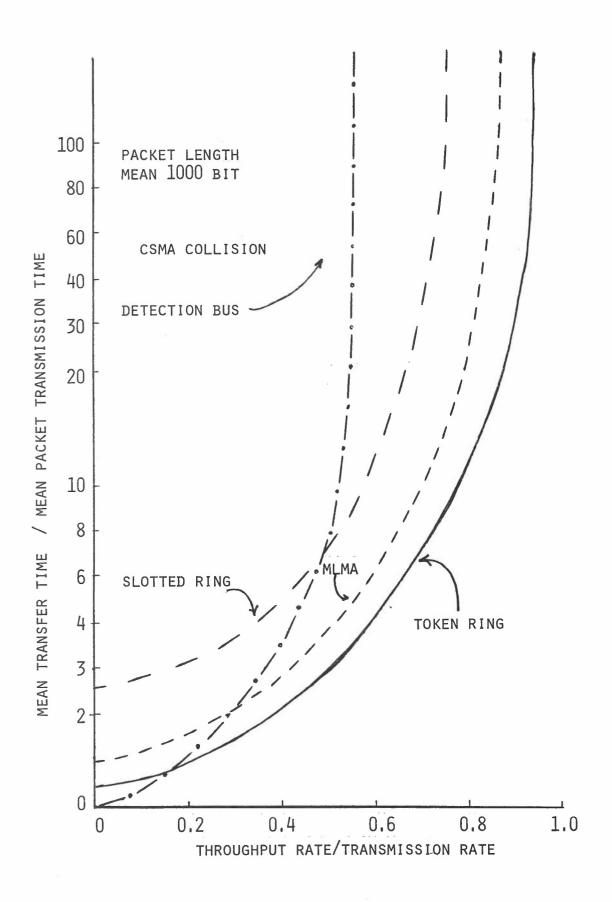

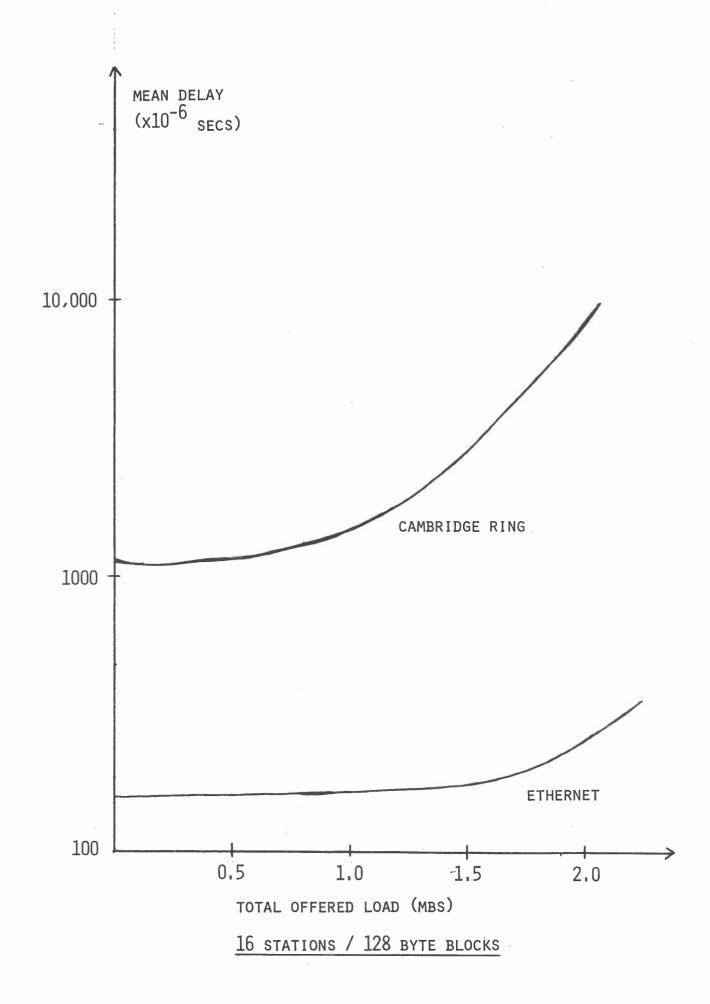

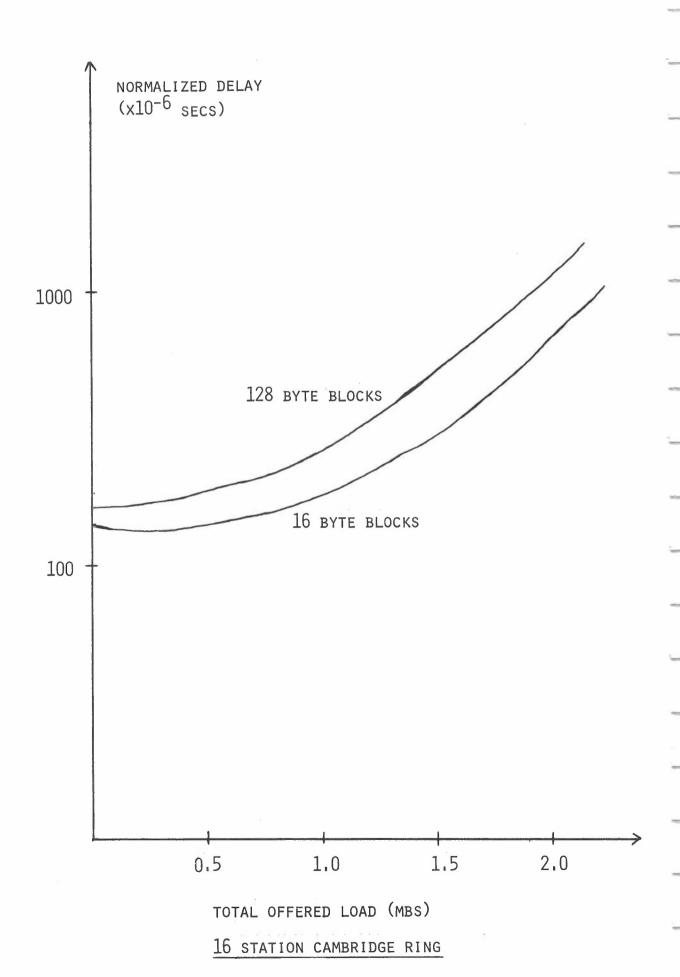

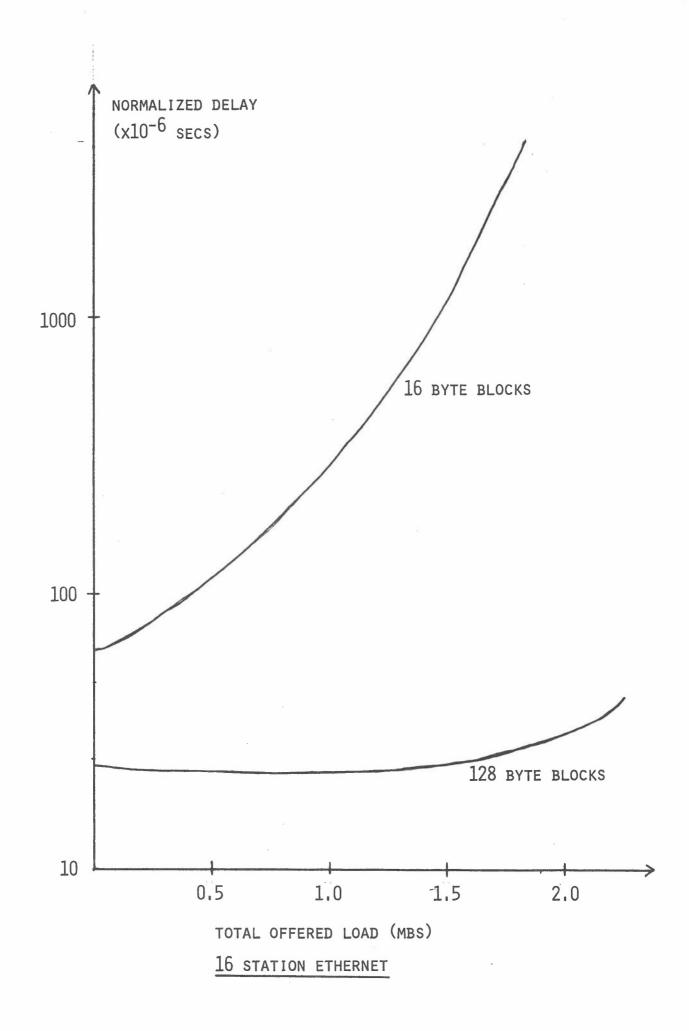

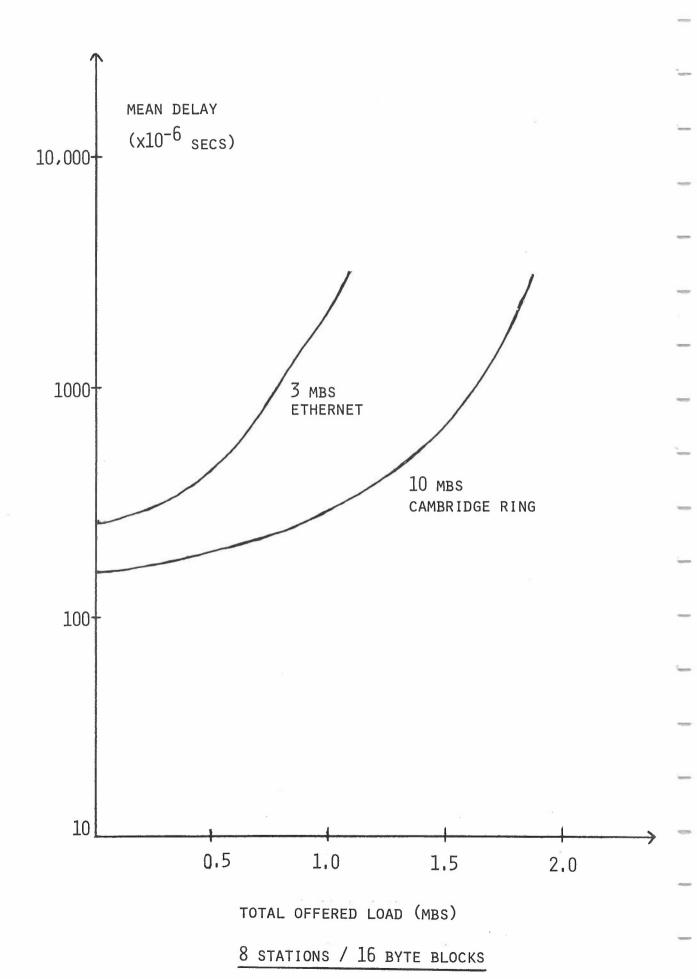

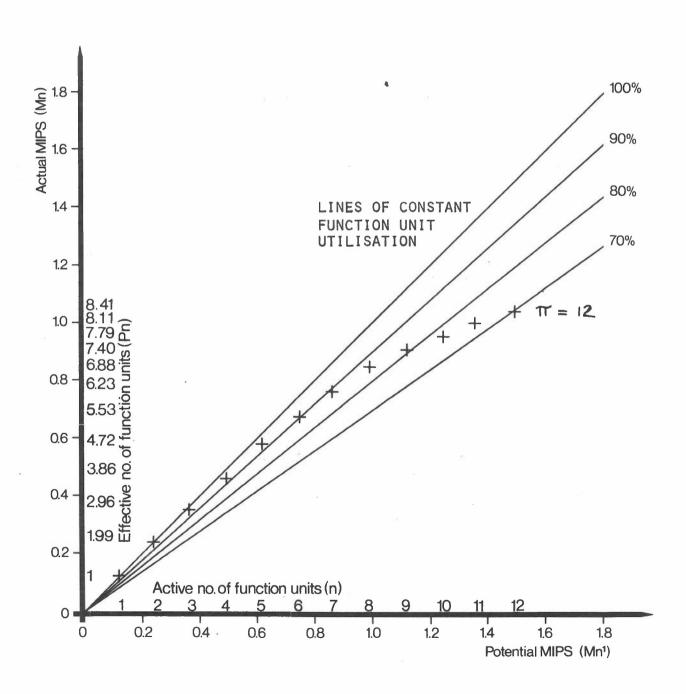

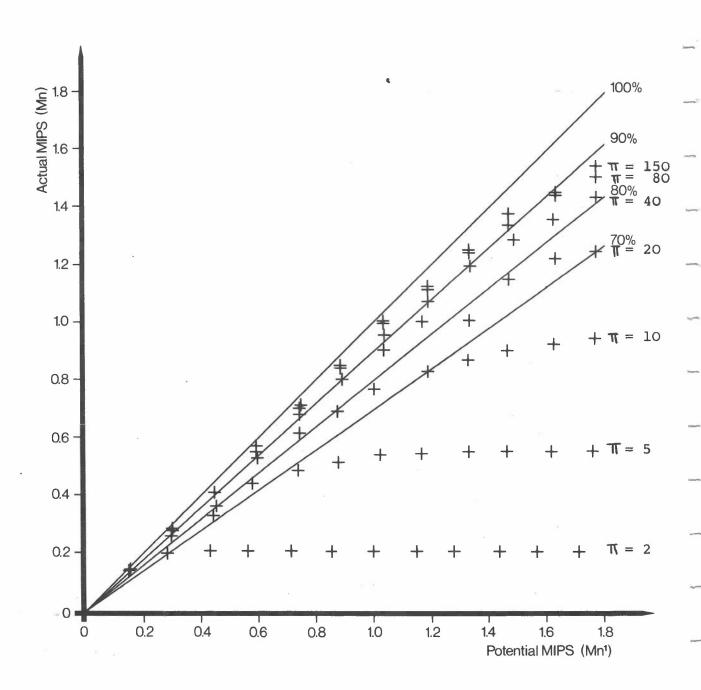

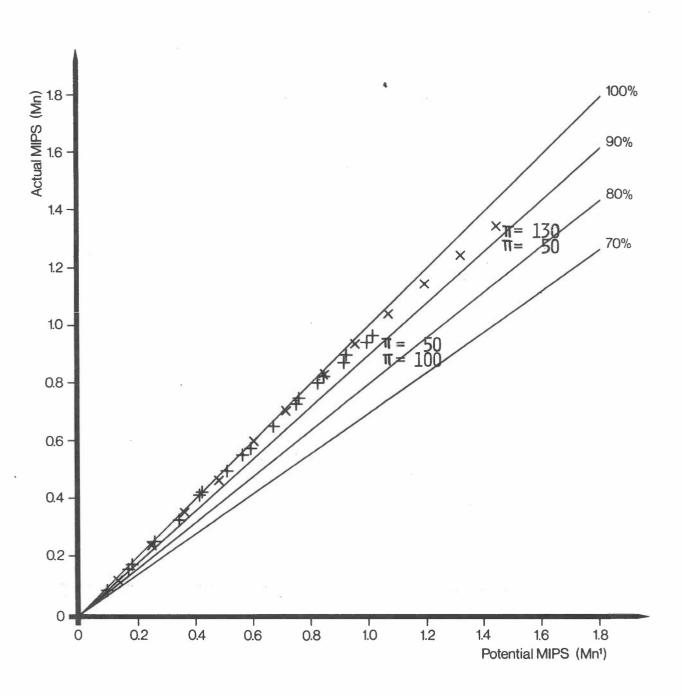

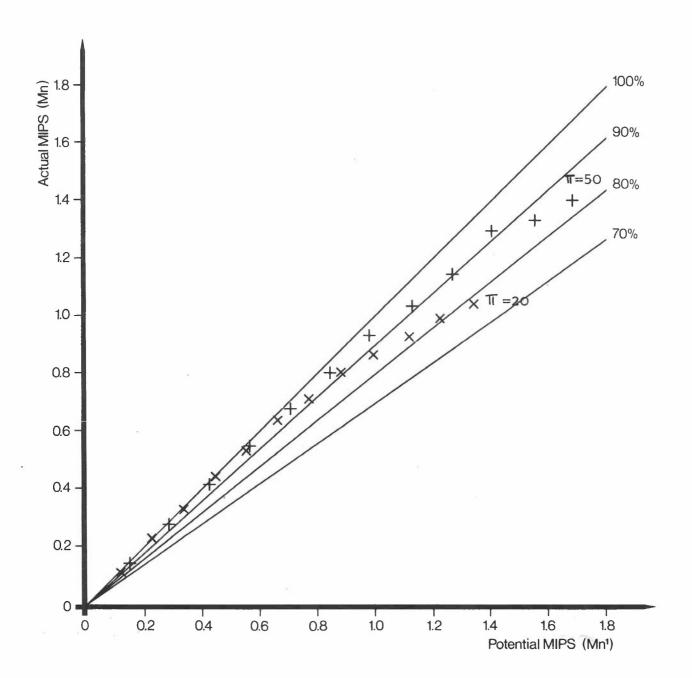

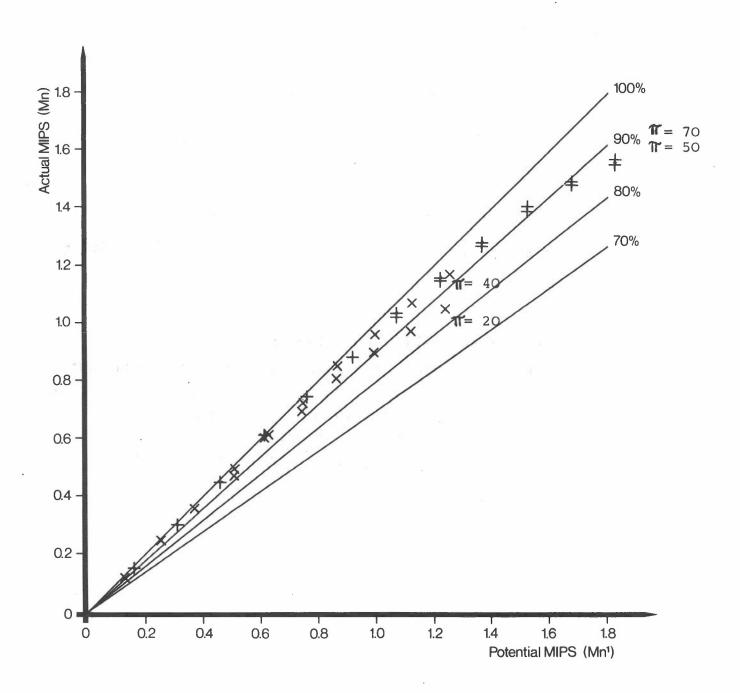

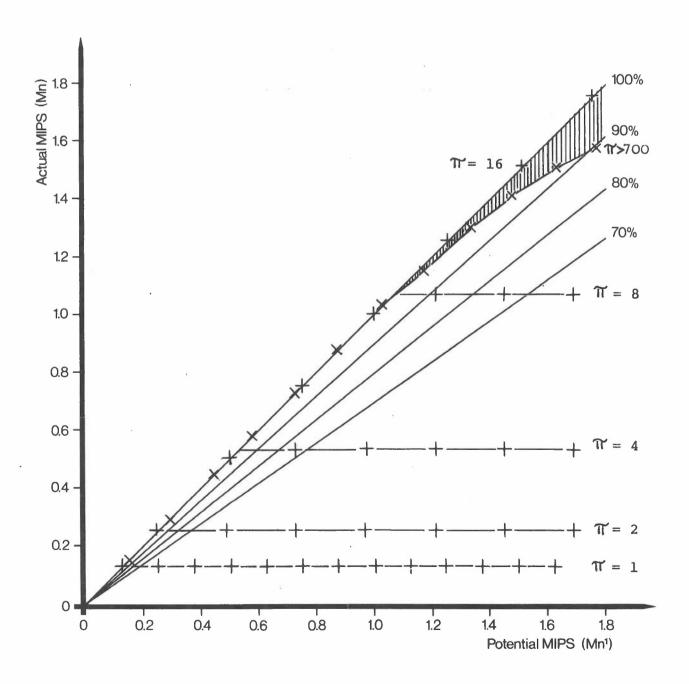

A large number of papers have appeared in the literature on modelling various local area network architectures [5]. The majority use analytical techniques but there are a few that use simulation. The three papers we will discuss in some detail are the ones by Werner Bux[6], Blair and Shepherd [7], and Almes and Lazowska[8]. The first paper compares analytically four different types of LAN architectures namely: token ring, slotted ring, random access bus (CSMA with collision detection), and ordered access bus (MLMA reservation scheme). The second uses simulation to compare the Standard Ethernet[9] with the Cambridge ring. The work described in the third is unusual in that it first of all derives an analytical model of an Ethernet-like system and then simulates the Experimental Ethernet system.

### 2.1 Analytical Comparison of Four Types of LAN Architecture

The performance criterion that Bux investigates is the delay-throughput characteristic of the system. Delay is measured as the mean transfer time of the packets which he defines as the time interval from the generation of a packet at the source station until its reception at the destination. This means the transfer time includes the queueing and access delay at the sender, the transmission time of the packet, and the propagation delay.

#### Modelling of the Networks

In order to allow for direct comparison of the results, consistent assumptions are made with respect to traffic properties for all models. These are: packets are generated at the S stations according to a Poisson process and the packet lengths can be generally distributed. A header is added to every packet which contains control and addressing information. Bux draws the following conclusions from his study. The token ring

performs almost ideally over the whole range provided the delay in each station is kept to a minimum. The slotted ring shows comparatively high transfer delay values due to the short slots of this type of ring, which mean that there is a high overhead for addressing and control information and the time needed to pass empty slots around the ring to ensure fair use of the bandwidth. The bus with CSMA and collision detection behaves ideally as long as the ratio of propagation delay to mean packet transmission time is low. If this ratio exceeds 5% the increase in collision frequency causes significant performance degradation. The MLMA ordered access bus shows slightly higher transfer delay than the token ring. This difference, which in most cases is insignificantly small, is caused by the overhead required for scheduling of the packets.

### 2.2 Simulation

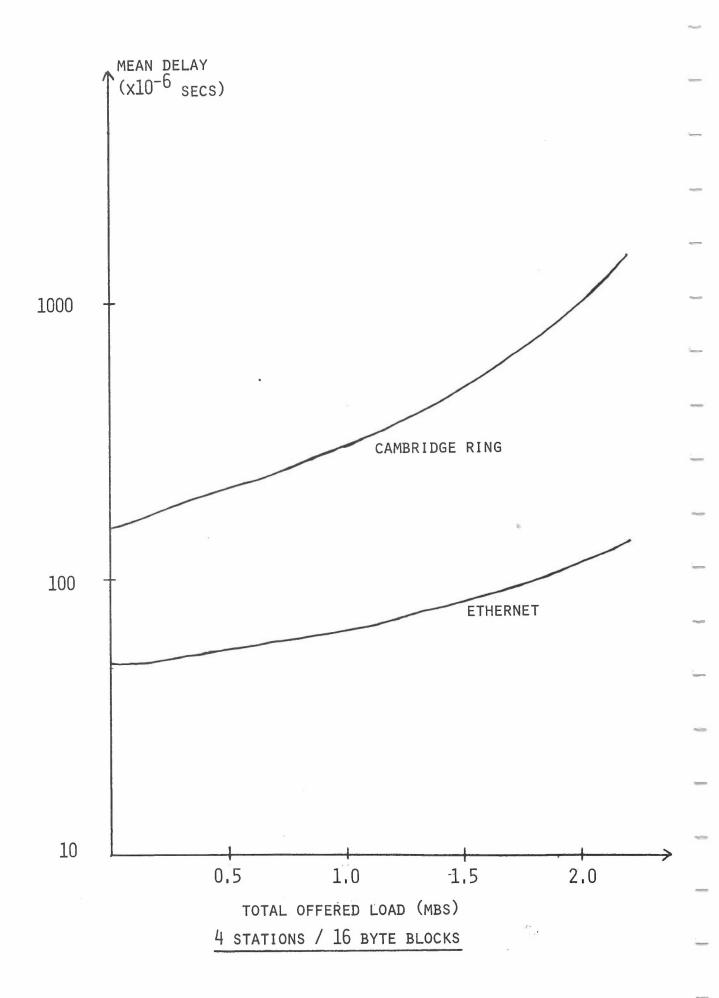

Blair and Shepherd have carried out a number of simulation studies of the Cambridge Ring and Ethernet-like systems[7,10]. The one we will discuss here compares the Cambridge Ring with the DEC, Intel, Xerox Ethernet[9]. The Standard DIX Ethernet specification was used namely:-

Data Rate 10 Mbs Slot time 512 bits

Jam Signal 32-48 bits Interframe spacing 9.6-10.6 microsecs

Preamble 64 bits Packet size 64-1518 bytes

The workload model consists of S stations. A Poisson arrival of messages is assumed with mean inter-arrival times t1 through tS. Constant message lengths L1 through LS are also assumed. A block consists of a header, route, data and checksum. A block is transmitted as one Ethernet frame or N ring minipackets. The error rate for each system is considered to be 1 in 10°7. Message destinations are random.

The following message statistics are collected:

- 1. Start time arrival time in station queues

- 2. Select time time message is selected for transmission

- 3. Finish time acknowledgment successfully received.

From these the mean queuing times, service times and delays can be calculated.

The number of stations, propagation delay between stations and frequency of the systems can be varied. In the case of the Cambridge Ring the number of minipackets and the number of data bytes per minipacket can be set. For the Ethernet the inter-frame spacing, length of preamble and length of jam signal can be varied.

The frequency of both the ring and ethernet were set at 10 MHz with a 6 bit delay between stations. The number of minipackets in the Cambridge Ring model is set to be optimal. The decision rule is to minimize the minipackets without introducing wasted bandwidth[11].

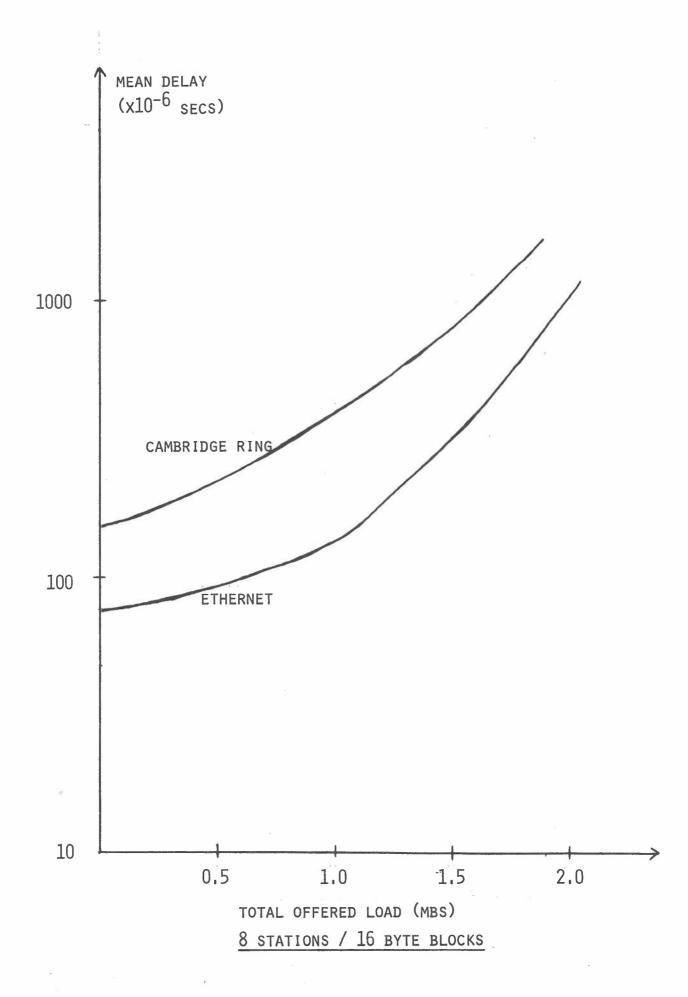

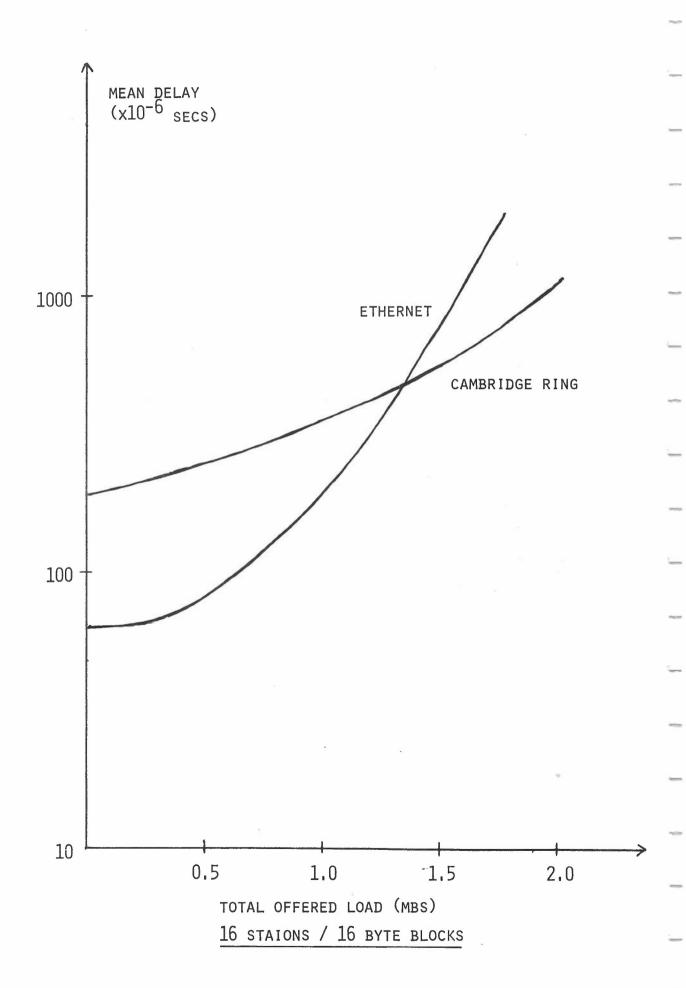

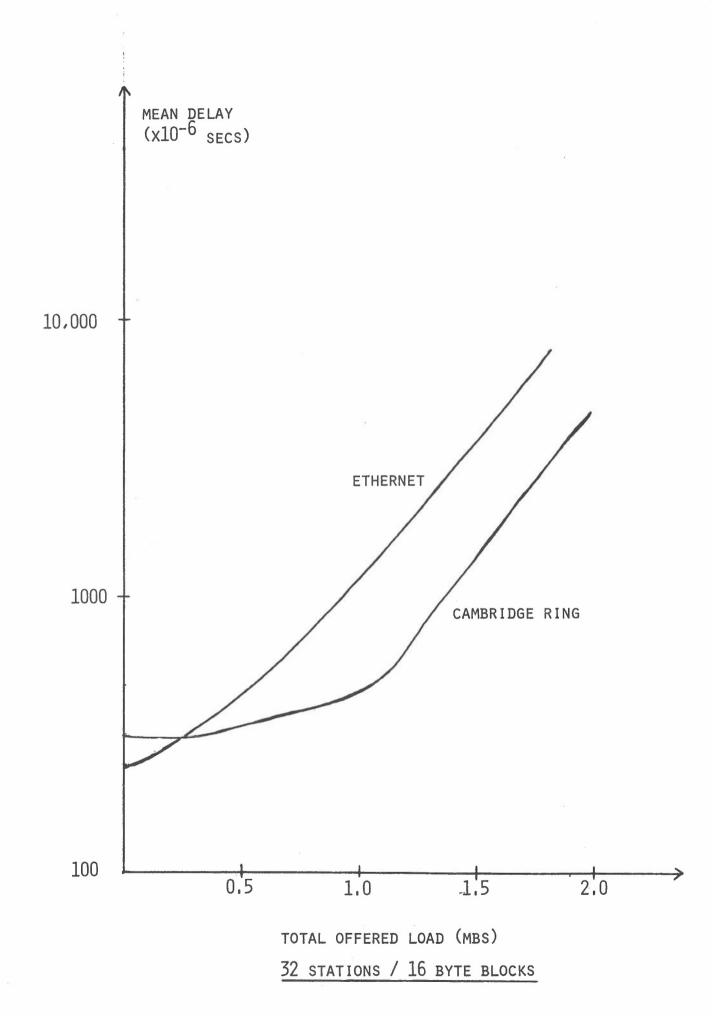

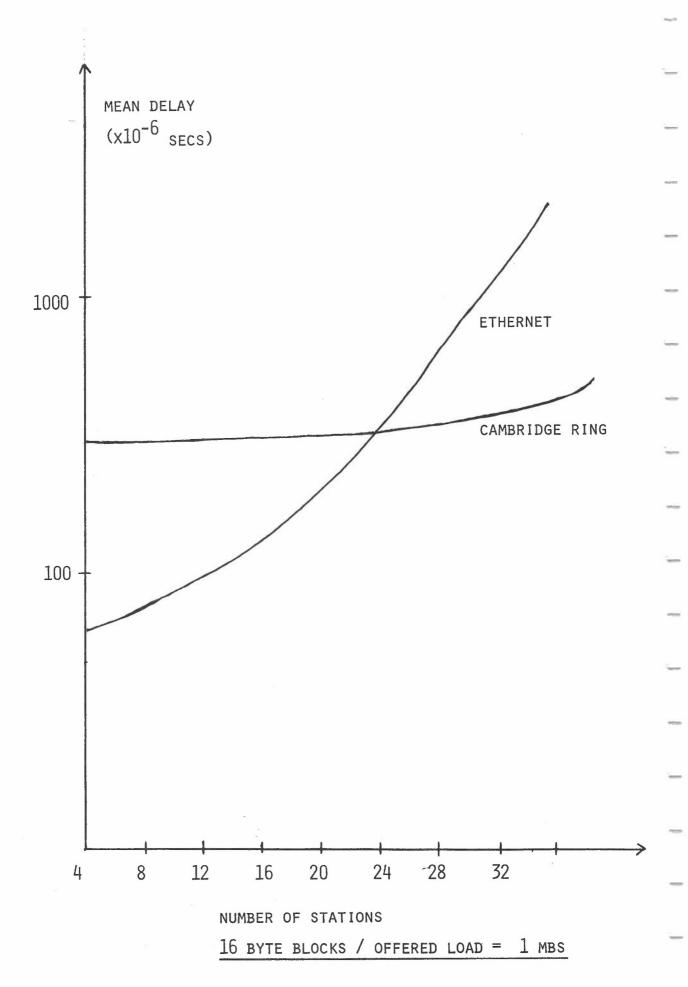

A number of experiments were carried out by varying the number of stations in the system while keeping the message length constant at 16 bytes. The results obtained show that as the number of stations increase the Ethernet is only better than the Cambridge Ring at low loads. For 32 stations the Cambridge Ring performs consistently better. The reason for this is that the collision window for the Ethernet is longer for larger networks increasing the chance of collisions whereas the addition of extra stations to the Cambridge Ring can be compensated by the extra packets that can be accommodated.

The simulators were then run using different message lengths. As the message lengths increase the performance of the Ethernet system is superior to the Cambridge Ring and in addition is more stable i.e. expected delay

does not degrade sharply as load increases.

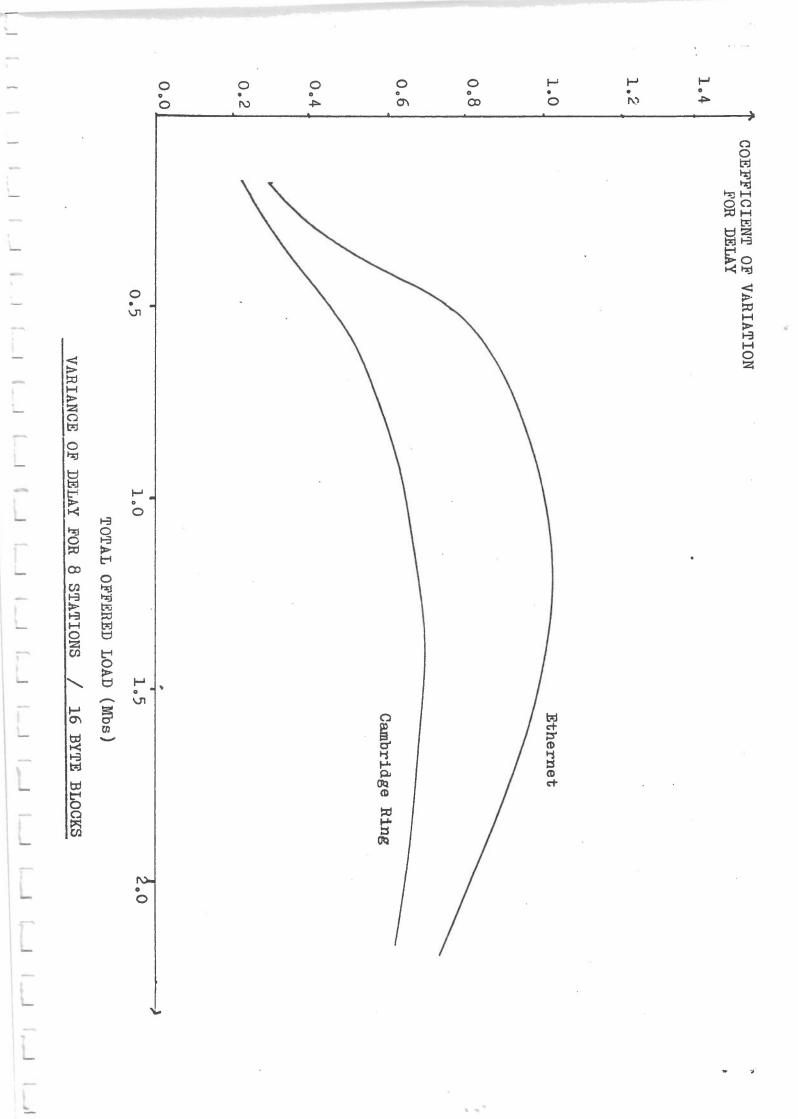

Satisfactory delay characteristics in LANs depend not only on low, stable expected delay but also on low variance of delay times. The variance of delay in the two systems was compared by plotting the ratio of standard deviation to mean for delay times against total offered load. Ethernet clearly has higher variance at all level of loads. There are two reasons for this:

- 1. It has been shown [12] that the backoff algorithm achieves stability for Ethernet at high loads at the expense of a kind of last come first served scheduling[8] resulting in high variance of delay times.

- 2. The Cambridge Ring has guaranteed maximum and minimum transmission times. The low level protocol implies that a station at worst gets 1/n(m+2) and at best gets 1/(m+2) in an n station, m minipacket ring.

The paper concludes that for most configurations Ethernet has a lower expected delay than the Cambridge Ring. The major reason for this is the overhead of the minipacket protocol in the Cambridge Ring. However the Cambridge Ring has the desirable property that delay characteristics do not depend on the size of the network or on the message lengths.

Almes and Lazowska use a simple analytic model based on 1/q control to study Ethernet-like systems, where q is a measure of the instantaneous load on the communication medium. They also simulate the Experimental Ethernet and from the results of their simulation conclude that their analytical model is acceptable. They also draw the following conclusions:-

Ethernet and other networks based on the 1/q model are stable.

The Ethernet has considerable variance in response time. This

variance does not, however, make it unsuitable for "soft real-time" applications at moderate average loads.

The performance of the systems is quite sensitive to packet size distribution. Higher technologies e.g optical fibres, will provide greatest benefit for applications that can use large packet lengths.

They also conclude that there might be some benefit in using a back-off algorithm based on an estimate of q from information available to the stations.

#### 3. Some Practical Measurements

Very few papers have appeared containing actual performance measurements of existing systems. An exception is the paper by Shoch[12] which considers the Ethernet at Xerox Parc and a paper by Temple[13] which examines the Cambridge Ring system at the University of Cambridge.

#### 3.1 Traffic Measurements of Ethernet

At Xerox Parc there are a number of interconnected Ethernet systems which have been providing a service for several years. They use a coaxial cable running at 2.94 MHz. The particular local Ethernetwork chosen for the measurements spans about 1800 feet and connects over 120 machines. These machines include a large number of single-user stand-alone computers, two time-sharing servers, numerous shared printers and fileservers as well as several gateways. Applications include: file transmission to the printers, access to shared data-base systems and terminal access to time-sharing machines.

To conduct the measurements a series of specialised test and monitoring

programs has been constructed to assess the behaviour of the network.

There is a <u>promiscuous</u> station which can receive all of the packets passing by. The measurements were taken using this passive technique.

One of the first results obtained was that one damaged packet in about 6000 was detected, and this resulted in the design of a new interface. Using the new interface a packet error rate of 1 in 2,000,000 packets was achieved.

### Performance Under Normal Traffic Loads

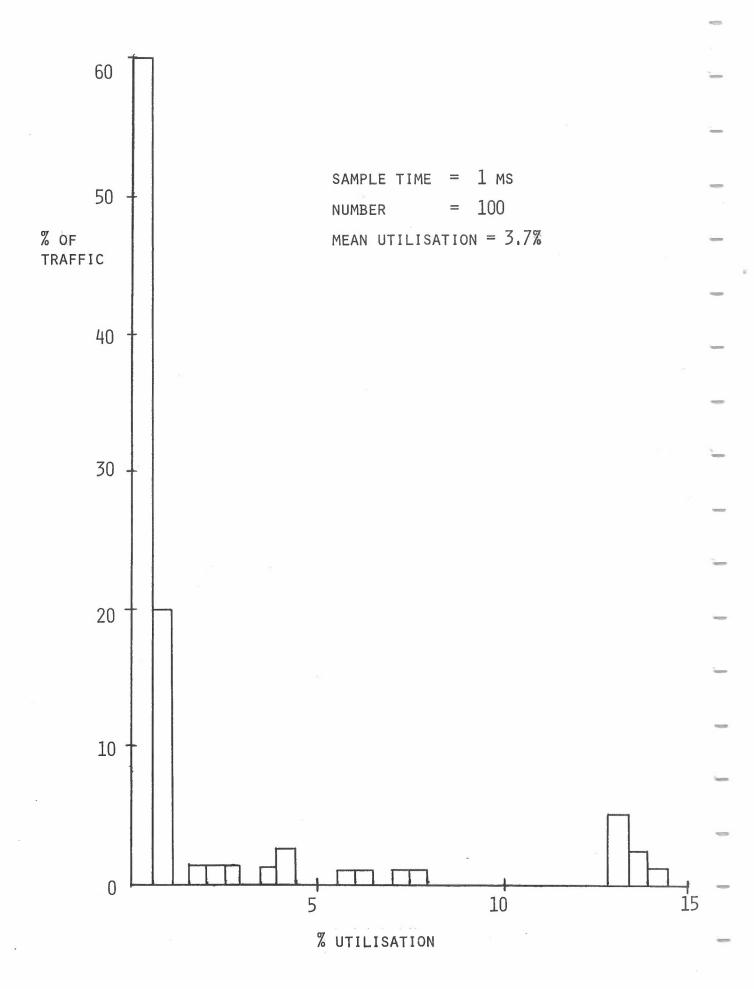

The utilisation of the system over a full 24-hour period ranges from 0.60% to 0.84%. During the busiest hour this rises to 3.6%, busiest minute 17% and busiest second 37% This verifies the design assumption that computer applications tend to produce a bursty pattern of requests.

Most of the packets sent through the system are short ones, but most of the total volume is carried in the large packets.

#### Performance Under High Load Conditions

The previous section discussed the system under normal operating conditions. Further growth of new systems will increase the load on the net and the system ought to be able to handle short term bursts at very high load.

To enable this to be tested a set of test programs was constructed to generate artificially high levels of traffic. Using a special control program these are loaded into idle machines on the net and then used to produce a specified offered load to the network. As the total offered load increases from 0% to 90% channel utilisation matches it perfectly: all the traffic gets out correctly and under high loads the Ethernet system remains

stable.

From these results it can be concluded that:

- 1. The error rates are very low, and few packets lost.

- 2. Under normal load, there are very few collisions.

- 3. Under heavy load there are more collisions but the collision mechanisms work well and channel utilisation remains high.

- 4. Even under heavy loads the Ethernet channel does not become unstable.

The last result would suggest that the several proposals for complex control schemes would offer little benefit for the increased complexity.

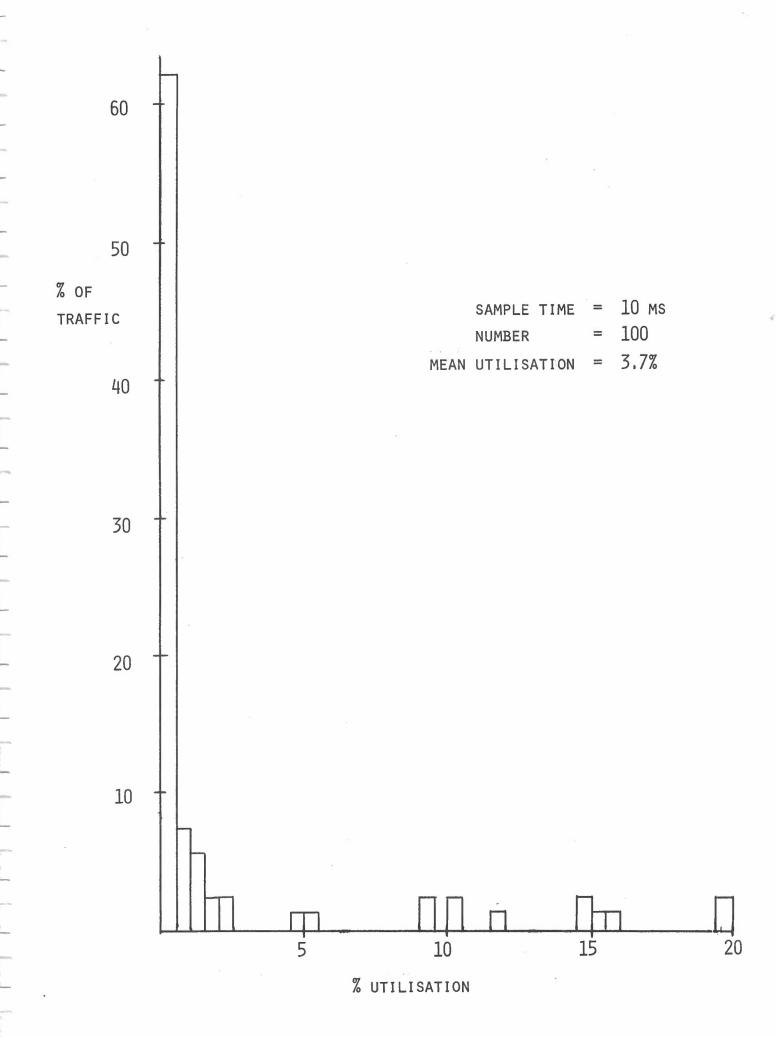

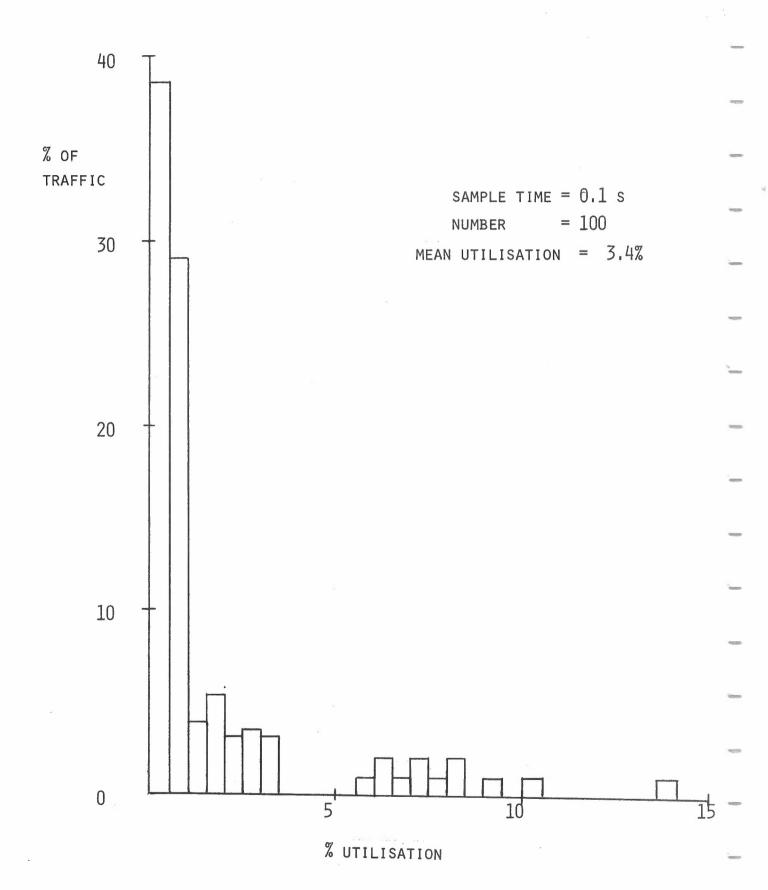

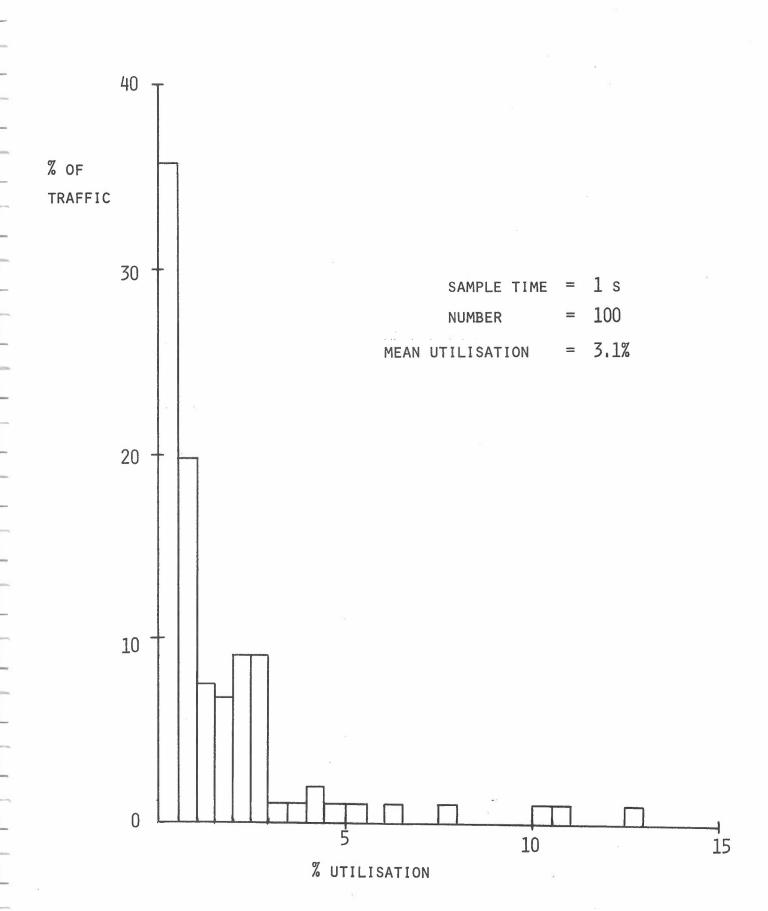

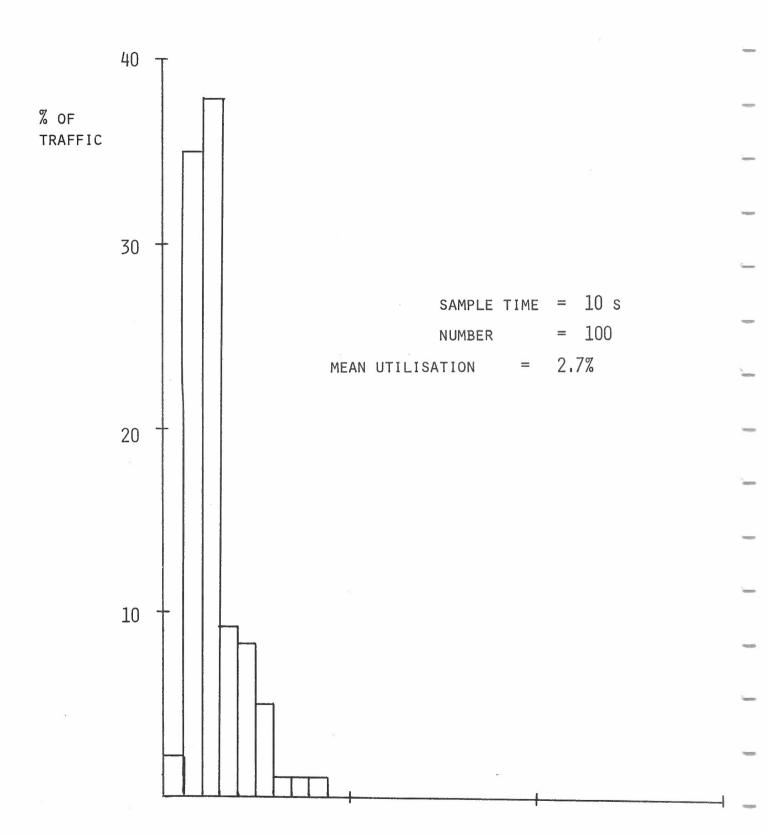

### 3.2 Traffic Measurements of the Cambridge Ring

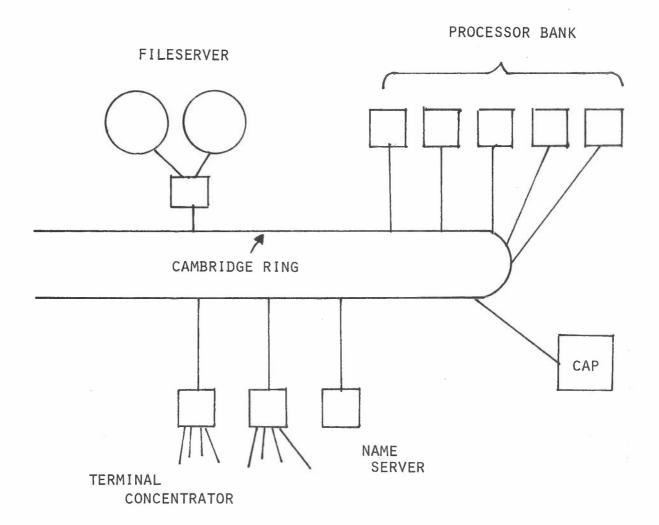

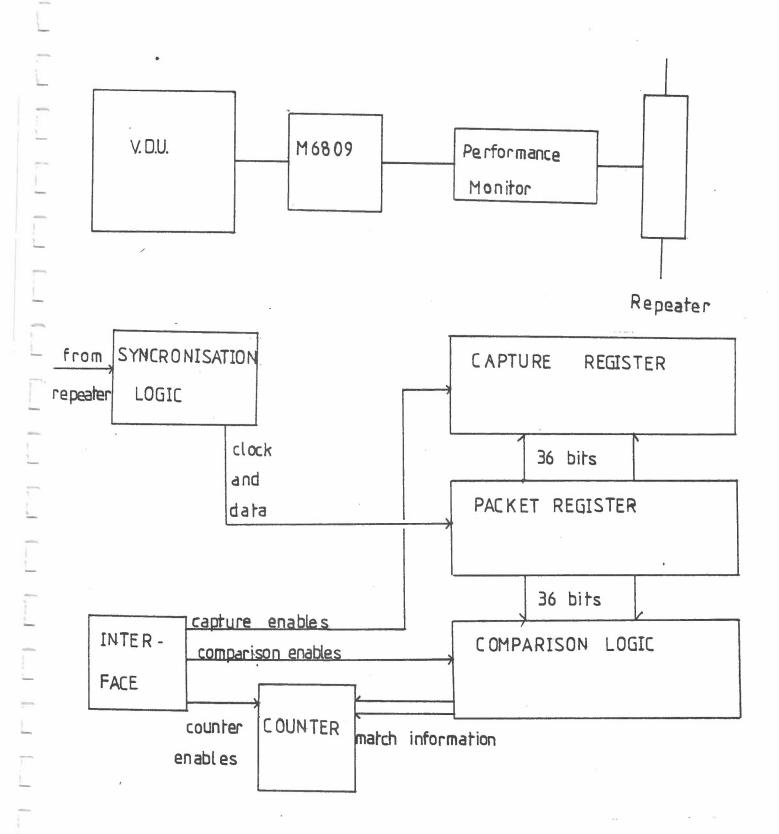

Some measurement work has been done at the University of Cambridge Computer Laboratory by Temple. The system consists of a Cambridge Ring operating at 9.8 Mbit/sec, with 3 minipacket slots and a gap of 3 bits. The ring is used to support the Cambridge Distributed Computing System[14] and also has a number of machines connected to it, such as the IBM 370, which provide a service for the general user. One of the devices on the ring is the fileserver[15] which as well as providing filing capabilities for the processor bank is used as a paging device for the CAP machine. i.e. swapping is carried out across the Ring.

A special device called a Traffic Monitor has been built which can be connected to the ring via a repeater. The repeater can either be a standalone one or one connected to a station. The traffic monitor can be attached to a standard vdu which allows particular patterns to be entered for matching against minipackets. The software also allows histograms of traffic to be displayed on the vdu. A complete description of the monitor

can be found in the report by Balfour[16].

The results from a typical experiment to see how many packets were accepted were that 86% are accepted, 2% unselected, 5% ignored, and 7% busied. The ring utilisation was 3.4%.

Most of the time the ring utilisation ia about 1% although bursts of up to about 20% were observed when a single station transmits at ring speed. For a medium term transaction, loading a processor bank machine, the utilisation is of the order of 10%. Over a longer period (30 mins) the typical utilisation is 3% and over a 24 hour period is 1.3%. The CAP is the only machine working at ring speed and one can see the bursts of CAP activity over a 0.1 sec time period. Over a 10 sec time period bursts are eliminated and utilisation clusters around a mean of 2.7%.

#### 4.Other Considerations

Although performance is an important factor in considering a local area network one thing that is perfectly clear from the previous sections is that all the systems discussed have more than ample bandwidth for current applications. In fact it is the belief of this author that in the case of Distributed Operating Systems the type LAN architecture you choose is irrelevant. In fact at Strathclyde we have developed a network operating system, called MIMAS, which runs on top of both an Ethernet-like system and a Cambridge Ring[17]. Therefore it should be other factors that influence the choice of LAN used. We discuss a few of these factors below.

### Internetworking

It seems extremely likely that any large organisation will have a number of separate installations consisting of devices connected together by their own local network. In order to gain the full potential of

networking and to maximise the sharing of expensive facilities such as disc storage it will be necessary to link these networks together. In addition it may be desirable to link the local area network to a wide area network, typically through the X25 access protocol.

Because of the variable size of their basic packets the token ring and the Ethernet have a clear advantage over the slotted rings with their smaller fixed length packets. For instance, in the case of the Cambridge Ring which has only 8 bits for the destination address the limit on the number of stations it can address is 256. This means that it has to use a local addressing scheme. Therefore, any gateway linking Cambridge Rings together must be able to transform from a local address to one recognised by the rest of the networks. The token ring and Ethernet, however, can have a larger destination and source field. In their case a global addressing scheme could be adopted using a standard 48 bit address field which would allow every station to have a unique address over all the networks. This has been proposed in the paper by Dalas and Printis[18], who call it a universal address. The use of universal station numbers in an internetwork provide for reliable and manageable operations as the system grows, as machines move, and as the overall topology changes.

#### Flow Control and Guaranteed Response.

The token ring and Ethernet have no low level flow control. A packet is sent to a station and the sender has no idea whether it has been accepted or not. Any acknowledgment must be provided by the higher level protocols. Experience is showing that it is the high level protocols which slow the systems down. The Cambridge Ring, however, indicates in the reponse bits whether or not the minipacket has been accepted. If for instance the response bits indicate that the destination was busy the minipacket can be

retransmitted.

With an Ethernet system there is no guaranteed response time. In the case of a token ring the maximum response time will be function of message lengths as well as the number of stations. The slotted ring, however, will have maximum response time which only depends on the number of stations in the system. This might be important in some real-time situations, for instance if the local area network is used to link some form of control system together.

Another example is the use of mixed voice and data traffic over the network. If the network is very lightly loaded then an Ethernet could handle voice as well as data[19] taking advantage of the fact that there is considerable redundancy in the digitised speech. However, if the load increased by having a large number of calls going on at the same time then the information lost would be unacceptable. The Cambridge Ring, however, would have the same characteristics whatever the load[20].

#### Cost

An important factor in evaluating any LAN will be its cost. In the opinion of the author there are a large number of applications of LANs that do not require a 10 Mbyte/sec bandwidth. Xerox Parc, for instance, have been operating with a 3 Mbyte/sec system for a number of years and the measurements carried out show that there is considerable spare capacity. This would appear to indicate that systems built using cheap off-the-shelf components operating at 1-2 MBits/sec would be quite suitable for a large number of cases, for example a shop floor reporting system[21].

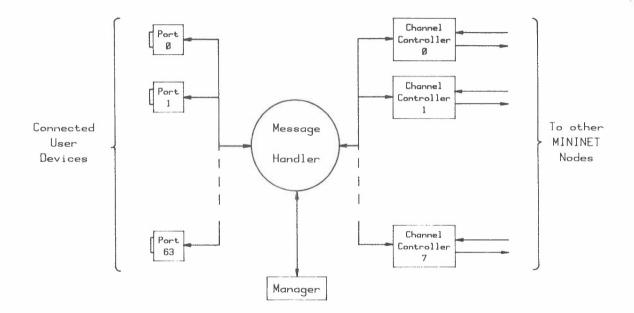

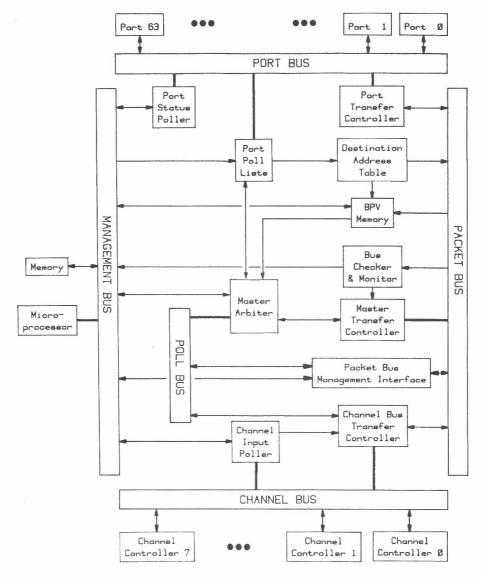

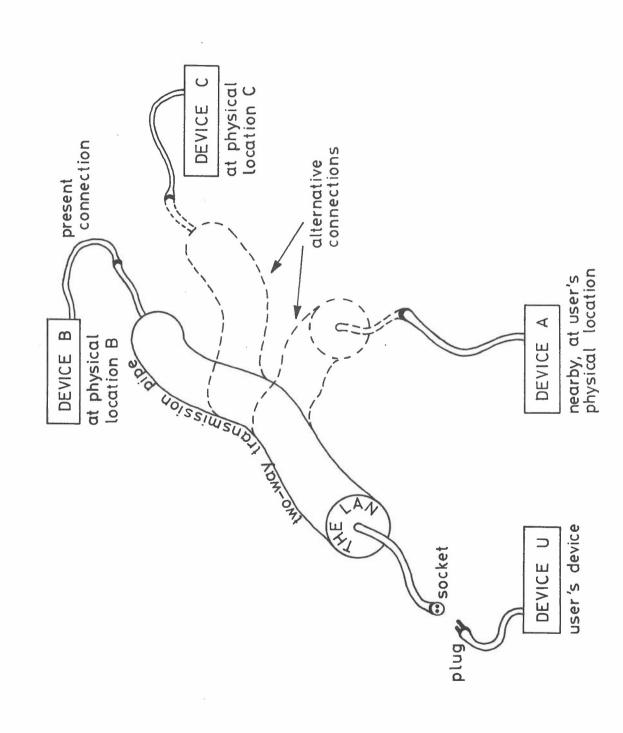

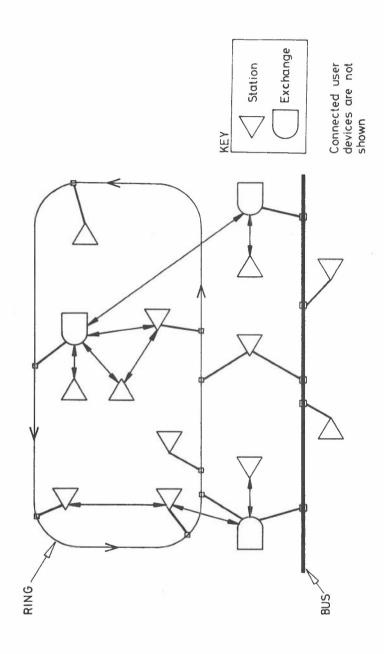

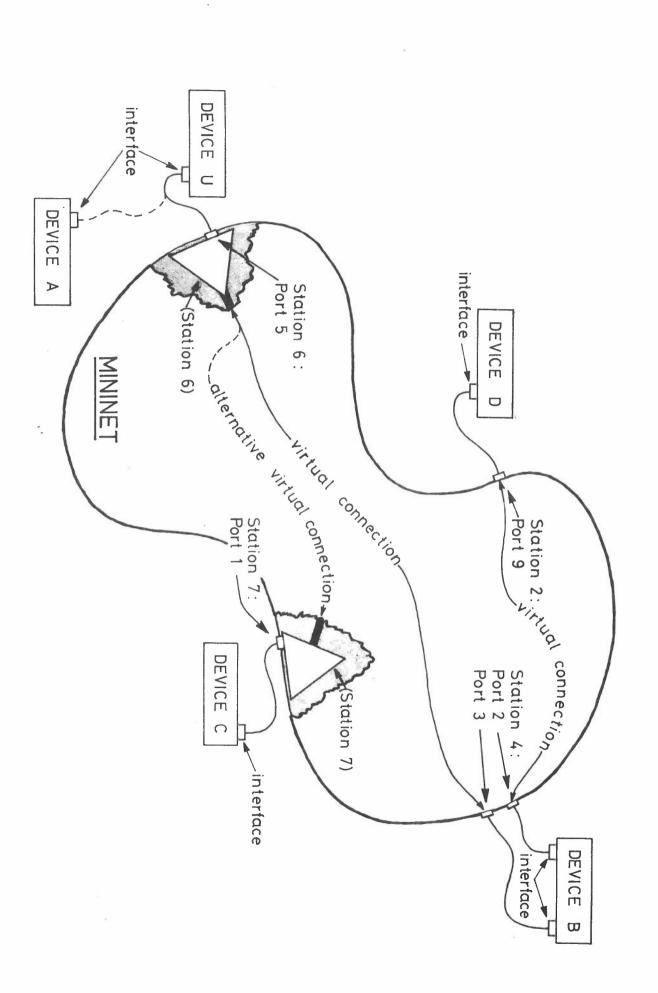

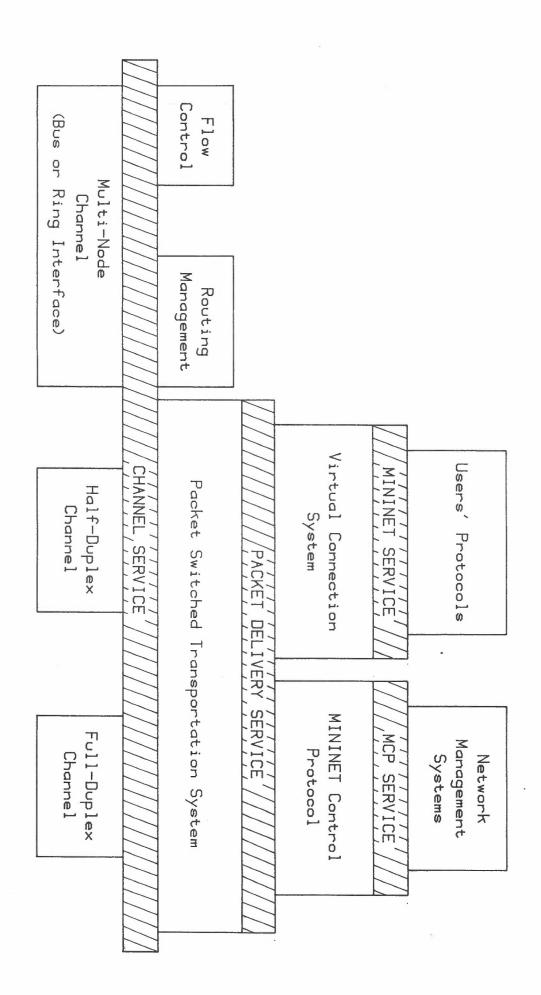

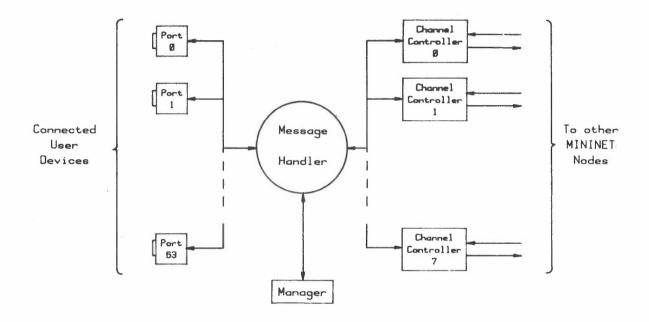

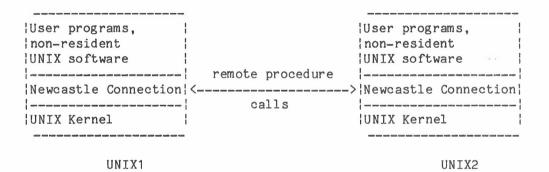

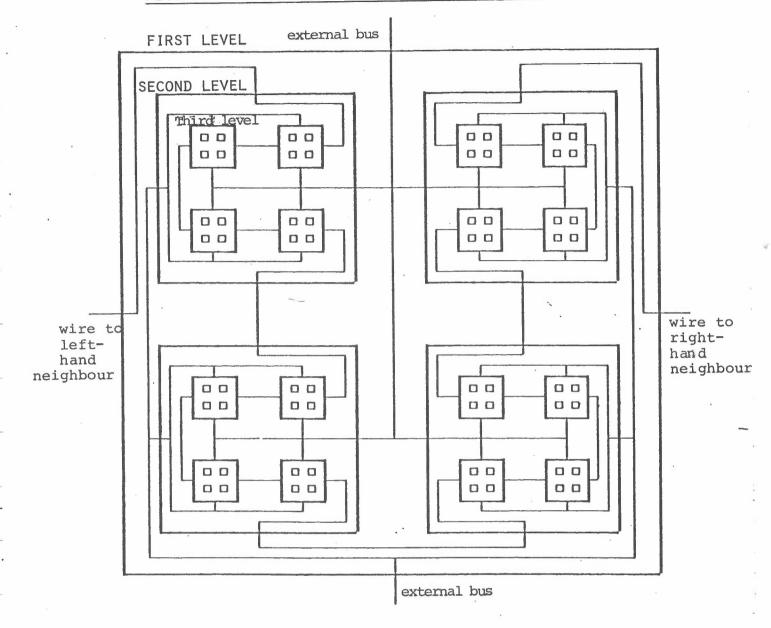

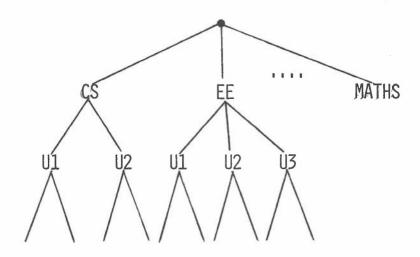

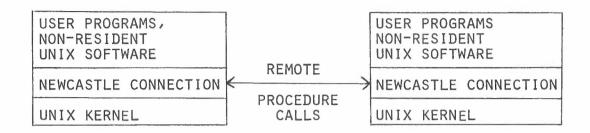

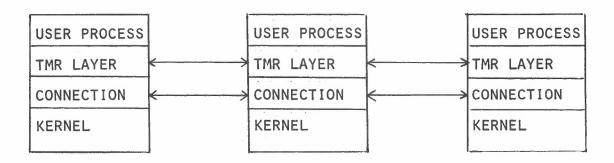

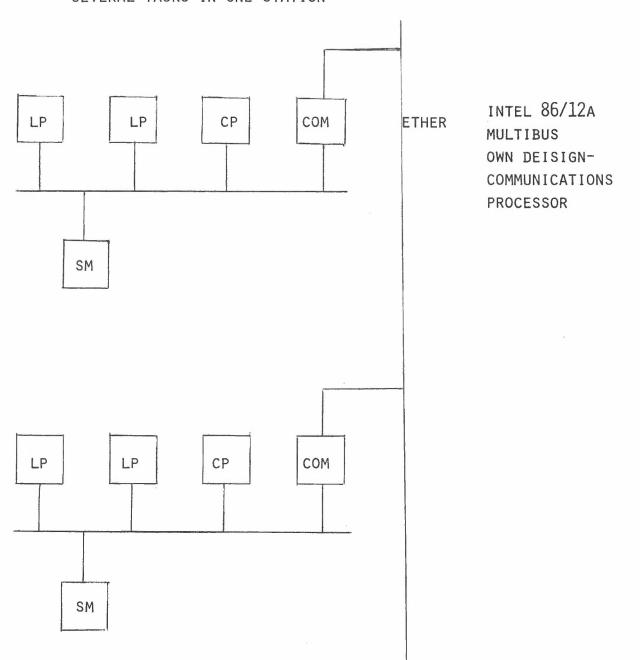

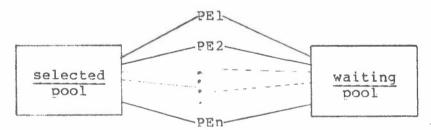

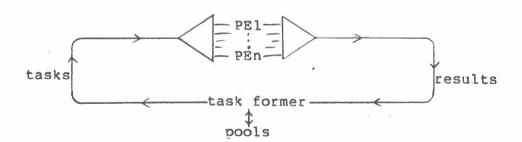

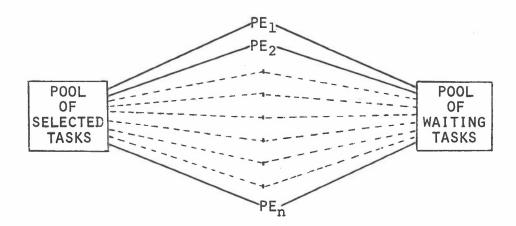

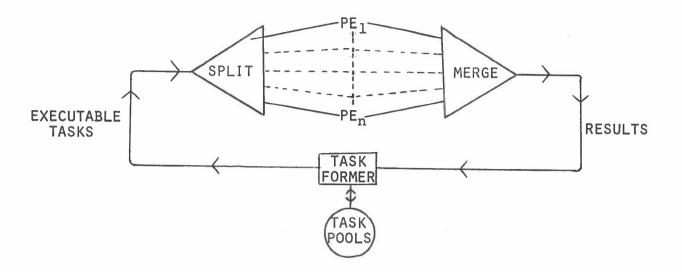

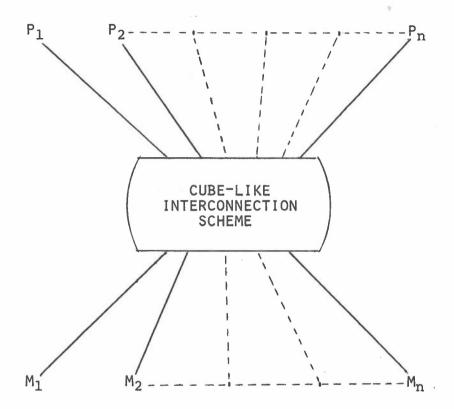

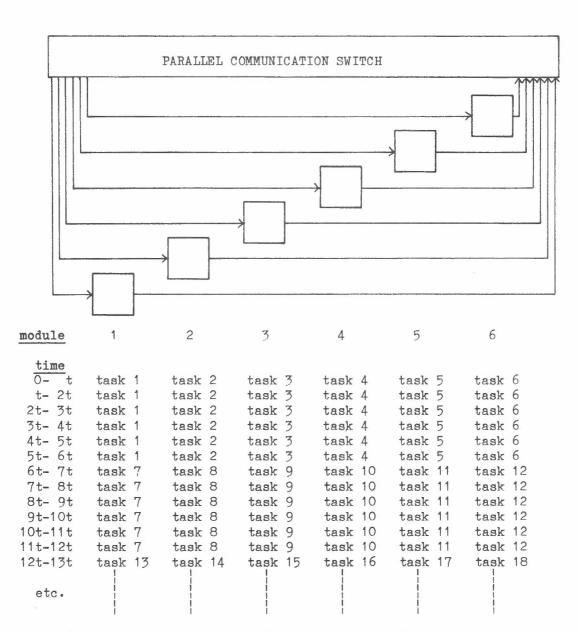

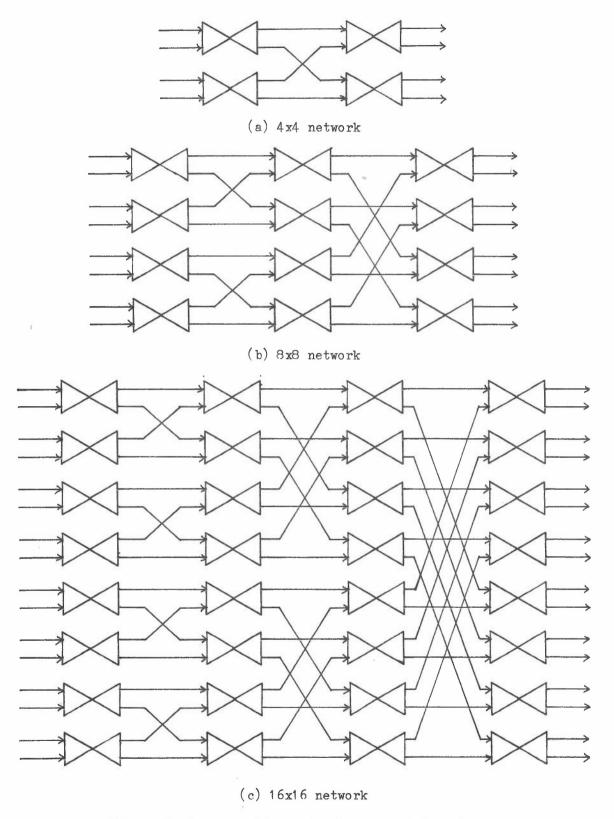

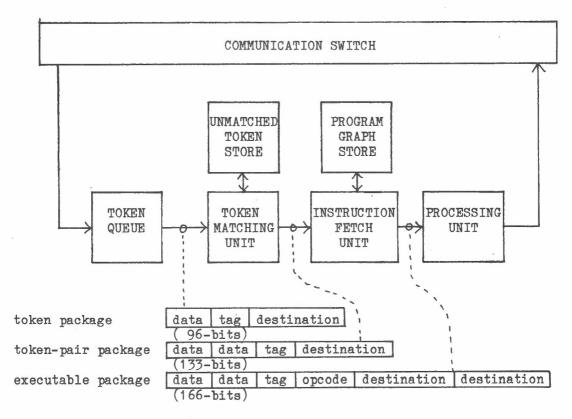

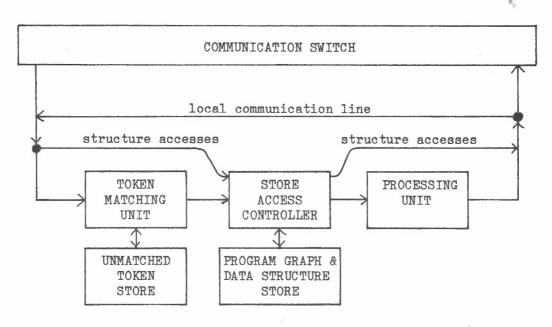

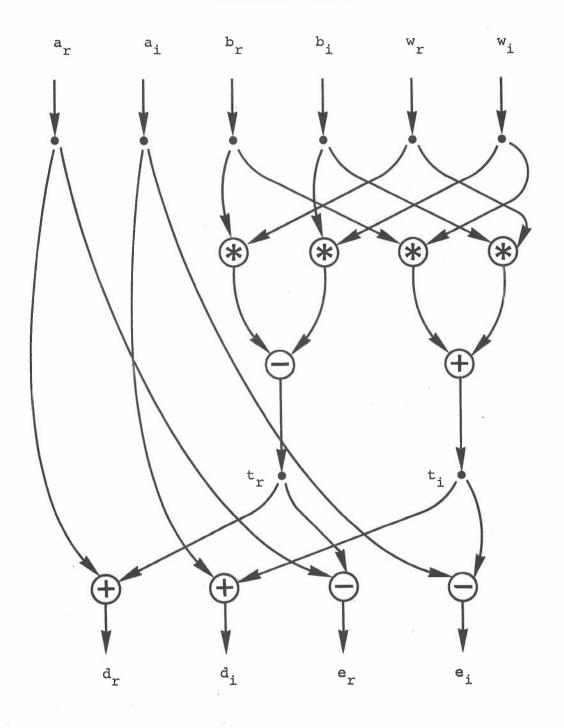

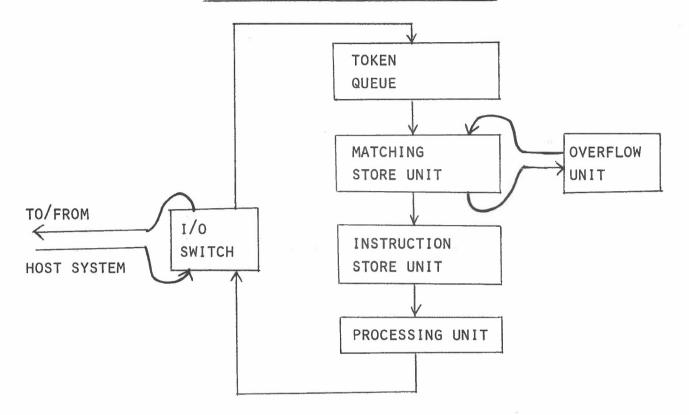

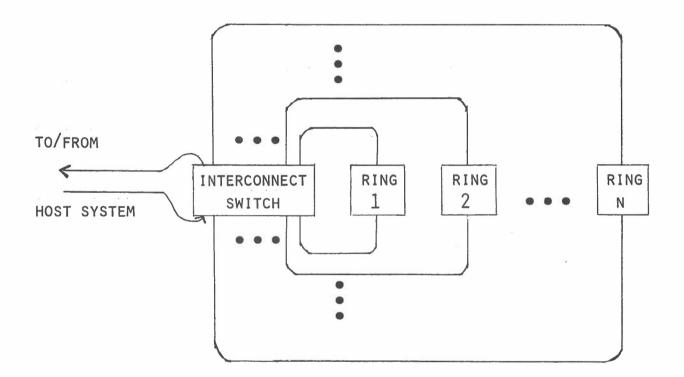

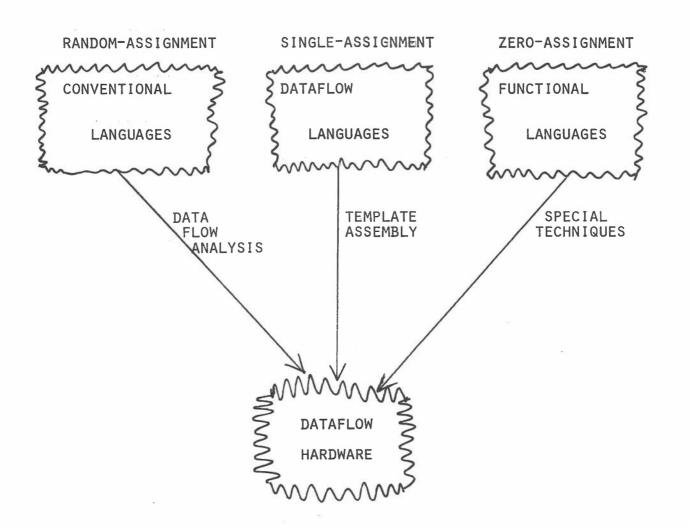

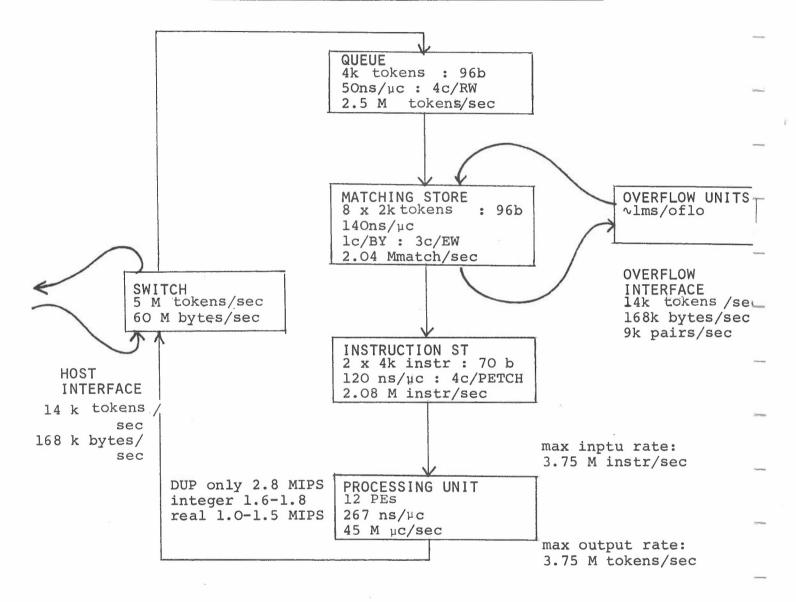

### High Level Protocols