APIC Studies in Data Processing No. 20

# DISTRIBUTED COMPUTING

Edited by FRED B. CHAMBERS

DAVID A. DUCE and GILLIAN P. JONES

# Distributed Computing

Edited by

# FRED B. CHAMBERS

Logica Ltd. London, England

DAVID A. DUCE GILLIAN P. JONES

Computing Division Rutherford Appleton Laboratory Didcot, England

**ACADEMIC PRESS**

(Harcourt Brace Jovanovich, Publishers)

London Orlando San Diego New York

Toronto Montreal Sydney Tokyo

UNIX™ is a Trademark of AT&T Bell Laboratories

Ada® is a registered Trade Mark of the U.S. Government (Ada Joint Program Office)

Chapter 21 is reproduced from Workshop on the Analysis of Concurrent Systems—Proceedings, Lecture Notes in Computer Science (to appear), by kind permission of Springer-Verlag

COPYRIGHT © 1984, BY ACADEMIC PRESS, INC. (LONDON) LTD. ALL RIGHTS RESERVED.

NO PART OF THS PUBLICATION MAY BE REPRODUCED OR TRANSMITTED IN ANY FORM OR BY ANY MEANS, ELECTRONIC OR MECHANICAL, INCLUDING PHOTOCOPY, RECORDING, OR ANY INFORMATION STORAGE AND RETRIEVAL SYSTEM, WITHOUT PERMISSION IN WRITING FROM THE PUBLISHER.

ACADEMIC PRESS, INC. (LONDON) LTD. 24-28 Oval Road, London NW1 7DX

United States Edition published by ACADEMIC PRESS, INC. Orlando, Florida 32887

LIBRARY OF CONGRESS CATALOG CARD NUMBER: 84-48446 ISBN 0-12-167350-2

# **Preface**

This book helps to mark the completion of the Distributed Computing Systems research programme (DCS) sponsored by the U.K. Science and Engineering Research Council. The DCS programme, from 1977-1984, culminated in a conference at the University of Sussex, Brighton, U.K. in September 1984. The conference included a series of tutorials on major topics in distributed computing, based on the contents of this volume. When the programme first started, there was relatively little research in distributed computing underway in the U.K., and it was to promote research in what was seen as a key area for the future, that the programme was conceived. During the lifetime of the programme the field grew enormously both in the breadth of activity and the depth of understanding. Within the programme itself, a number of research themes emerged, and these have been reflected in the organization of the book.

The book aims to give a basic grounding in each of the areas covered. A general familiarity with the relevant aspects of computing is assumed, but specialist knowledge is not required. The book should be of interest to researchers and practitioners in the field, academic and industrial, and will also serve as an introductory text for new researchers. It is appropriate as an undergraduate or postgraduate text for a single-term introductory course on distributed systems.

The book is divided into five parts corresponding to the five themes covered.

- Part I describes the dataflow approach to parallel computation, one of the bases on which parallel super computer of the future will be constructed. This part is contributed by John Glauert, John Gurd, Chris Kirkham and Ian Watson, all members of the Manchester dataflow project, a DCS funded investigation which has established a world lead in this approach. Topics covered include the basic principles of dataflow computing, the evolution of dataflow computer architectures and the high level languages used to program them. Details of the Manchester prototype dataflow computer structure, instruction set and performance are presented. The single-assignment programming language SISAL is introduced.

- Part II is concerned with declarative languages, and with computer architectures to support their evaluation. The essence of the declarative approach to programming is to shift the burden of determining in detail how something must be done, from the programmer to the architecture. The first chapter in this part, by John Darlington, introduces the reader to functional languages and their conventional implementation. The next chapter, by Bill Clocksin, introduces logic languages and their conventional implementations. The remaining chapters, by Richard Kennaway and Ronan Sleep, describe the origins and rise of novel architectures to support such languages, and the parallel approach to implementation.

- Part III addresses loosely-coupled distributed systems. Such systems are multicomputer configurations that do not share immediate memory and can be dispersed over wide geographical areas. They form much the greater part of the distributed systems that have investigated and are in use today. The chapters in this part, by Keith Bennet, Ian Wand and Andy Wellings, describe the general architecture of such systems and examine the detailed requirements of their various components, operating systems appropriate to this environment and related programming languages.

- Part IV deals with closely-coupled distributed systems, typically systems which do share a common memory. The alternative architectures that may be adopted for the design of such systems; the structure and features of typical programming languages; the nature of run-time support software; and software development tools for debugging and testing applications, are considered in turn. This part concludes with two case studies describing the overall design of hardware and software for experimental multimicroprocessor systems (Cyba-M, developed at Swansea and UMIST; and POLYPROC, University of Sussex).

- Part V by Robin Milner and Samson Abramsky faces the essential questions of modelling and verifying concurrent systems. What is a good mathematical model of concurrency? Can there be a common model for both hardware and software? A concurrent program may be thought of alternatively as software to be compiled or as description of the behaviour of a piece of hardware. The development of fundamental notations for such programs' description is explored and some approaches to verifying them mathematically are illustrated using simple examples.

The editors of this book were the Industrial Coordinator, Academic Coordinator and Technical Secretary of the DCS Programme when it terminated. We, and the contributors, wish to acknowledge the many researchers whose work has contributed to this book.

We are particularly grateful to Paul, Arthur, Frits and many others at CWI for their assistance, patience and understanding during the preparation of the book. Finally, we would like to thank Alan Kinroy, Duncan Gibson and Elizabeth Fielding for their sterling work in producing the many diagrams in the book.

Easter 3, 1984

Fred B Chambers David A Duce Gillian P Jones

# Contributors

- S. Abramsky Department of Computing, Imperial College, 180 Queen's Gate, London SW7 2BZ

- D. Aspinall Department of Computation, University of Manchester Institute of Science and Technology, P. O. Box 88, Manchester, M60 1QD

- K. H. Bennett Department of Computer Science, University of Keele, Keele, Staffs ST5 5BG

- W. F. Clocksin Computer Laboratory, University of Cambridge, Corn Exchange Street, Cambridge CB2 3QG

- J. Darlington Department of Computing, Imperial College, 180 Queen's Gate, London SW7 2BZ

- J. R. W. Glauert School of Computing Studies, University of East Anglia, University Village, Norwich NO4 8BC

- R. L. Grimsdale School of Engineering and Applied Sciences, University of Sussex, Falmer, Brighton BN1 9QT

- J. R. Gurd Department of Computer Science, University of Manchester, Oxford Road, Manchester M13 9PL

- F. Halsall School of Engineering and Applied Sciences, University of Sussex, Falmer, Brighton BN1 9QT

- J. R. Kennaway School of Computing Studies, University of East Anglia, University Village, Norwich NO4 8BC

- C. C. Kirkham Department of Computer Science, University of Manchester, Oxford Road, Manchester M13 9PL

- A. J. R. G. Milner Department of Computer Science, James Clerk Maxwell Building, The King's Buildings, Mayfield Road, Edinburgh EH9 3JZ

- M. R. Sleep School of Computing Studies, University of East Anglia, University Village, Norwich NO4 8BC

- I. C. Wand Department of Computer Science, University of York, Heslington, York YO1 5DD

- I. Watson Department of Computer Science, University of Manchester, Oxford Road, Manchester M13 9PL

- A. J. Wellings Department of Computer Science, University of York, Heslington, York YO1 5DD

# Contents

| Co  | vii  |                                      |    |

|-----|------|--------------------------------------|----|

| Pa  | rt I | The Dataflow Approach                |    |

| 1   | Fun  | damentals of Dataflow                |    |

|     | 1.1  | INTRODUCTION                         | 3  |

|     | 1.2  | PARALLELISM IN SOFTWARE              | 4  |

|     | 1.3  | PROGRAMS AS GRAPHS                   | 5  |

|     | 1.4  | GENERALIZED DATAFLOW GRAPHS          | 10 |

|     | 1.5  | COMPILATION OF GRAPH CODE            | 16 |

|     | 1.6  | SUMMARY OF DATAFLOW GRAPHS           | 17 |

|     | 1.7  | REFERENCES                           | 18 |

| 2   | Arcl | nitecture and Performance            |    |

|     | 2.1  | INTRODUCTION                         | 21 |

|     | 2.2  | MACHINE TOPOLOGIES                   | 23 |

|     | 2.3  | PRACTICAL MACHINES                   | 26 |

|     | 2.4  | PERFORMANCE OF DATAFLOW SYSTEMS      | 30 |

|     | 2.5  | REFERENCES                           | 31 |

| 3   | Ass  | embler Level Programming             |    |

|     | 3.1  | MANCHESTER DATAFLOW MACHINE FEATURES | 33 |

|     | 3.2  | THE INSTRUCTION SET                  | 34 |

|     | 3.3  | THE MACHINE-LEVEL USER INTERFACE     | 37 |

|     | 3.4  | THE TEMPLATE ASSEMBLER (TASS)        | 38 |

|     | 3.5  | REFERENCES                           | 41 |

| 4   | High | Level Dataflow Programming           |    |

|     | 4.1  | INTRODUCTION                         | 43 |

|     | 4.2  | PROGRAM STRUCTURE                    | 43 |

|     | 4.3  | DATA STRUCTURE                       | 46 |

|     | 4.4  | OTHER LANGUAGE FEATURES              | 49 |

|     | 4.5  |                                      | 50 |

|     | 4.6  | REFERENCES                           | 53 |

| Pai | t II | <b>Declarative Systems</b>           |    |

| 5   | Fun  | ctional Programming                  |    |

|     | 5.1  | INTRODUCTION                         | 57 |

|     | 5.2  | FUNCTIONAL PROGRAMMING               | 59 |

|     |      |                                      |    |

# x Distributed Computing

|     | 5.3   | FUNCTIONAL PROGRAMMING METHODOLOGIES              | 66  |

|-----|-------|---------------------------------------------------|-----|

|     | 5.4   | SEQUENTIAL IMPLEMENTATION OF FUNCTIONAL LANGUAGES | 70  |

|     | 5.5   | FUNCTIONAL LANGUAGES                              | 72  |

|     | 5.6   | APPLICATIONS OF FUNCTIONAL LANGUAGES              | 73  |

|     | 5.7   | FUTURE DEVELOPMENT OF FUNCTIONAL LANGUAGES        | 74  |

|     | 5.8   | REFERENCES                                        | 75  |

| 6   | Logi  | c Programming and Prolog                          |     |

|     | 6.1   | AN HISTORICAL INTRODUCTION                        | 79  |

|     | 6.2   | PREDICATE CALCULUS                                | 81  |

|     | 6.3   | FUNCTIONAL AND RELATIONAL FORMS, AND PROOFS       | 83  |

|     | 6.4   | SUBSTITUTION AND UNIFICATION                      | 85  |

|     | 6.5   | CLAUSES AND RESOLUTION                            | 87  |

|     | 6.6   | LOGIC PROGRAMMING TERMINOLOGY                     | 90  |

|     | 6.7   | DATABASES AND NEGATION                            | 91  |

|     | 6.8   | PROLOG AS A PROGRAMMING LANGUAGE                  | 93  |

|     | 6.9   | EXTRALOGICAL FEATURES                             | 98  |

|     | 6.10  | IDIOMATIC PROGRAMMING IN PROLOG                   | 99  |

|     | 6.11  | PRACTICAL APPLICATIONS OF PROLOG                  | 101 |

|     | 6.12  | ACKNOWLEDGEMENTS                                  | 104 |

|     | 6.13  | REFERENCES                                        | 104 |

| 7   | The   | 'Language First' Approach                         |     |

|     | 7.1   | MOTIVATION FOR CHANGE                             | 111 |

|     | 7.2   | THE 'LANGUAGE-FIRST' APPROACH                     | 112 |

|     | 7.3   | DESIGN ISSUES FOR LAMBDA MACHINES                 | 115 |

|     | 7.4   | THE IMPORTANCE OF THEORY                          | 123 |

|     | 7.5   | REFERENCES                                        | 123 |

| 8   | Tow   | ards a Successor to von Neumann                   |     |

|     | 8.1   | PHYSICAL MODELS                                   | 125 |

|     | 8.2   | EVOLUTIONS OF THE VON NEUMANN PHYSICAL MODEL      | 125 |

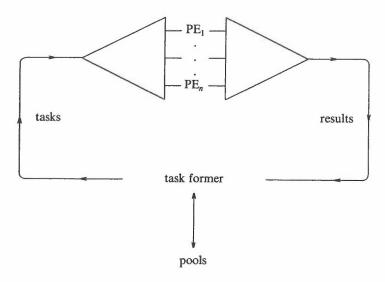

|     | 8.3   | A GENERAL MODEL OF A VON NEUMANN SUCCESSOR        | 126 |

|     | 8.4   | PARTICULAR ORGANIZATIONS FOR DISTRIBUTING WORK    | 128 |

|     | 8.5   | A NOTE ON LOGIC MACHINES                          | 133 |

|     | 8.6   | CONCLUSION                                        | 135 |

|     | 8.7   | ACKNOWLEDGEMENTS                                  | 135 |

|     | 8.8   | REFERENCES                                        | 136 |

| _   |       |                                                   |     |

| Par | t III | Loosely-Coupled Systems                           |     |

| 9   | Arch  | itectures                                         |     |

|     | 9.1   | INTRODUCTION                                      | 141 |

|     | 9.2   | OBJECTIVES                                        | 142 |

|     | 9.3   | A MODEL FOR DISTRIBUTED SYSTEM ARCHITECTURES      | 142 |

|     | 9.4   | THE MODEL LAYERS                                  | 143 |

|     | 9.5   | ISSUES WITHIN EACH LAYER                          | 144 |

|     | 9.6   | GLOBAL ISSUES                                     | 146 |

|     | 9.7   | REFERENCES                                        | 146 |

| 10  | Com   | munications                                       |     |

|     | 10.1  | INTRODUCTION                                      | 147 |

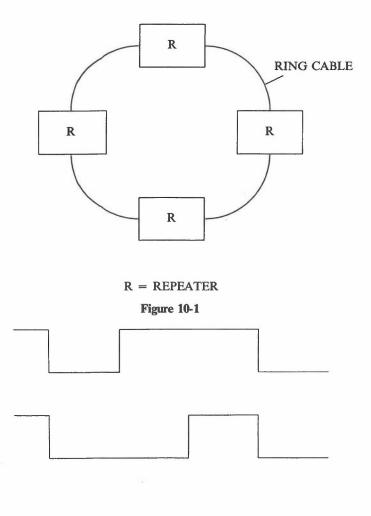

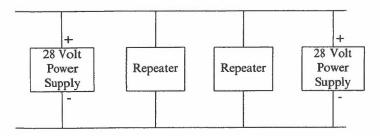

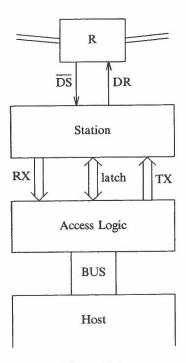

|     | 10.2  | THE CAMBRIDGE RING                                | 148 |

|     | 10.3  | PROTOCOLS                                         | 151 |

|     | 10.4  | PERFORMANCE ISSUES                                | 155 |

|      |       |                                                           | Contents | xi  |

|------|-------|-----------------------------------------------------------|----------|-----|

|      | 10.5  | DE /EI 001/E1/E0                                          |          |     |

|      |       | DEVELOPMENTS                                              |          | 157 |

|      |       | CONCLUSIONS                                               |          | 158 |

| 11   |       | REFERENCES                                                |          | 158 |

| 11   |       | ributed Filestores                                        |          | 101 |

|      |       | MOTIVATION                                                |          | 161 |

|      |       | ISSUES IN DISTRIBUTED FILESTORE DESIGN                    |          | 163 |

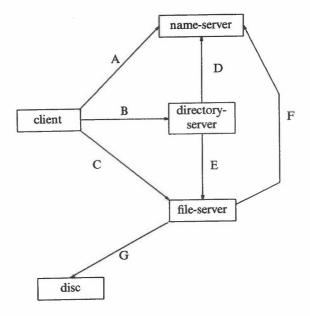

|      |       | REVIEW OF DISTRIBUTED FILESTORES THE CAMBRIDGE FILESERVER |          | 166 |

|      |       |                                                           |          | 166 |

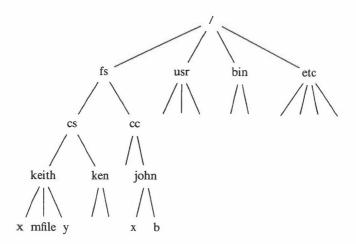

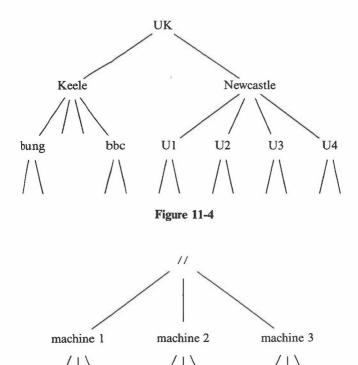

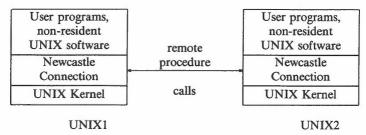

|      |       | UNIX UNITED                                               |          | 168 |

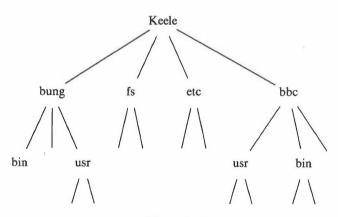

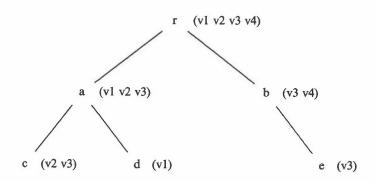

|      |       | THE KEELE DISTRIBUTED FILESTORE                           |          | 171 |

|      |       | OTHER WORK                                                |          | 175 |

| 10   |       | REFERENCES                                                |          | 176 |

| 12   |       | hanisms for Distributed Control                           |          | 470 |

|      |       | REVIEW OF PROBLEMS                                        |          | 179 |

|      | _     | SYNCHRONISATION IN DISTRIBUTED SYSTEMS                    |          | 181 |

|      | _     | ATOMIC TRANSACTIONS                                       |          | 183 |

|      |       | TRANSACTION STRUCTURES                                    |          | 186 |

|      |       | MULTIPLE COPY UPDATING                                    |          | 187 |

|      |       | SUMMARY                                                   |          | 191 |

| 40   |       | REFERENCES                                                |          | 191 |

| 13   |       | ibuted Operating Systems                                  |          |     |

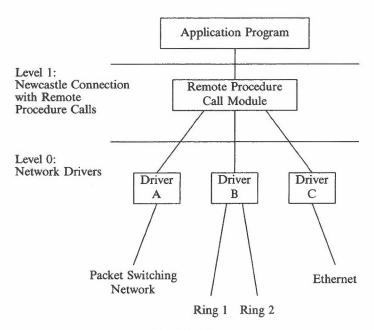

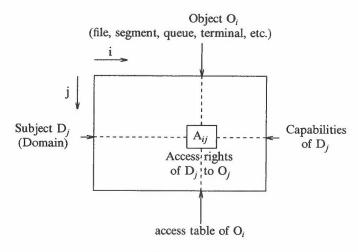

|      |       | THE DISTRIBUTED SYSTEM MODEL                              |          | 193 |

|      |       | CLASSIFICATION OF DISTRIBUTED OPERATING SYSTEMS           |          | 195 |

|      |       | DESCRIPTION OF TWO DISTRIBUTED OPERATING SYSTEMS          |          | 196 |

|      |       | REFERENCES                                                |          | 198 |

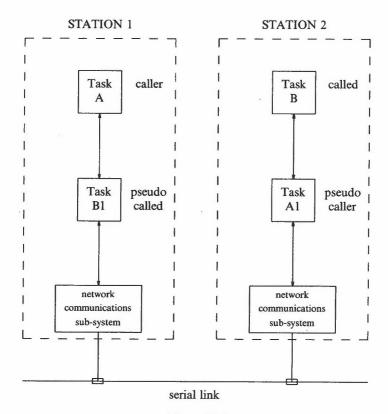

| 14   | -     | gramming Languages                                        |          | 001 |

|      |       | INTRODUCTION                                              |          | 201 |

|      |       | CONCURRENT EXECUTION                                      |          | 201 |

|      |       | TASKS ON LOOSELY COUPLED DISTRIBUTED SYSTEMS              |          | 208 |

|      | 14.4  | REFERENCES                                                |          | 212 |

| Parl | IV    | Closely-Coupled Systems                                   |          |     |

| 15   | Arch  | itecture                                                  |          |     |

|      | 15.1  | INTRODUCTION                                              |          | 219 |

|      | 15.2  | INTERCONNECTION STRATEGIES                                |          | 220 |

|      | 15.3  | INSTRUCTION SET PRIMITIVES                                |          | 221 |

|      | 15.4  | TEST AND SET OF LOCK                                      |          | 221 |

|      | 15.5  | MATCHING OF PROCESSOR AND MEMORY SPEED                    |          | 222 |

|      | 15.6  | SHARED MEMORY IMPLEMENTATION                              |          | 223 |

|      | 15.7  | COMMON FEATURES OF SHARED MEMORY ACCESS MECHANISMS        | S        | 225 |

|      | 15.8  | POINT-TO-POINT INTERCONNECTIONS: THE TRANSPUTER           |          | 227 |

|      | 15.9  | CONCLUSIONS                                               |          | 228 |

|      | 15.10 | REFERENCES                                                |          | 228 |

| 16   | Prog  | ramming Languages                                         |          |     |

|      | 16.1  | INTRODUCTION                                              |          | 231 |

|      | 16.2  | CONCURRENCY SUPPORT MECHANISMS                            |          | 231 |

|      |       | THE MONITOR CONCEPT                                       |          | 232 |

|      | 16.4  | THE RENDEZVOUS                                            |          | 234 |

|      |       | SYSTEM DEADLOCK                                           |          | 236 |

|      | 16.6  | REFERENCES                                                |          | 236 |

|      |       |                                                           |          |     |

# xii Distributed Computing

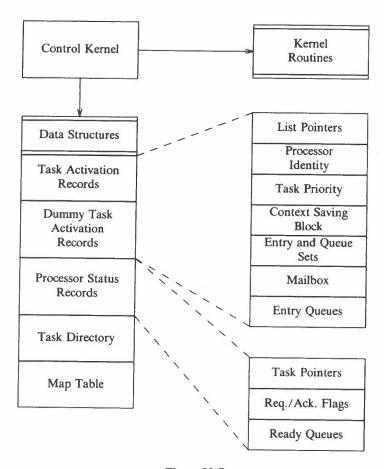

| 17   | Run-time Support                                |     |

|------|-------------------------------------------------|-----|

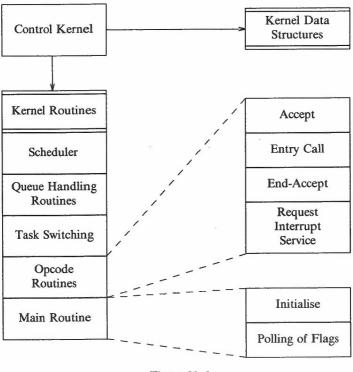

|      | 17.1 THE CONTROL KERNEL                         | 239 |

|      | 17.2 CONTROL KERNEL IMPLEMENTATION              | 24  |

|      | 17.3 INTER-PROCESSOR COMMUNICATIONS MECHANISMS  | 248 |

|      | 17.4 REFERENCES                                 | 250 |

| 18   | Development Aids                                |     |

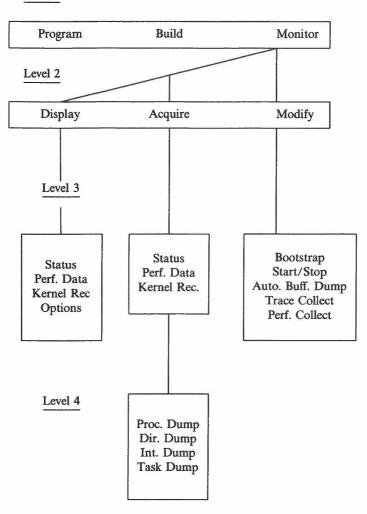

|      | 18.1 INTRODUCTION                               | 25  |

|      | 18.2 THE LABORATORY M-MDS                       | 253 |

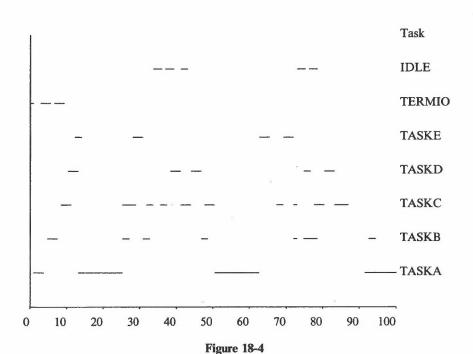

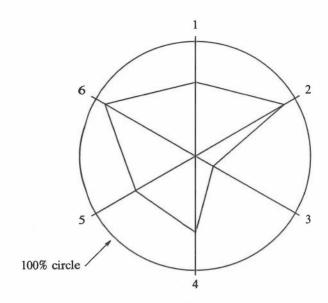

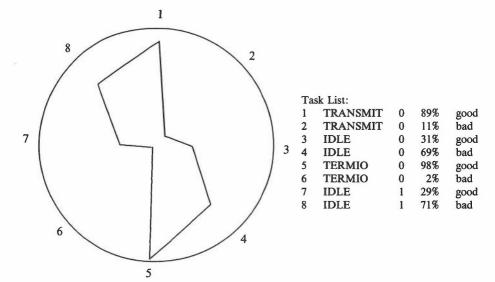

|      | 18.3 RUN-TIME SUPPORT FACILITIES                | 255 |

|      | 18.4 DISCUSSION AND CONCLUSIONS                 | 269 |

|      | 18.5 REFERENCES                                 | 266 |

| 19   | Cyba-M                                          |     |

|      | 19.1 INTRODUCTION                               | 267 |

|      | 19.2 SPECIFICATION AND INITIAL DESIGN DECISIONS | 268 |

|      | 19.3 HARDWARE DESIGN CONSIDERATIONS             | 272 |

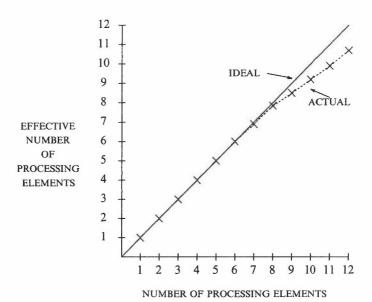

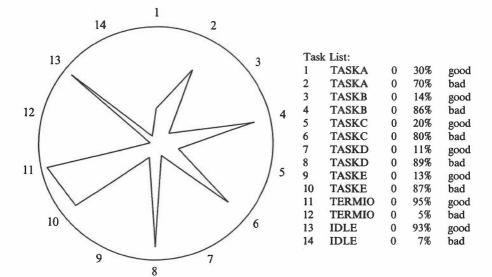

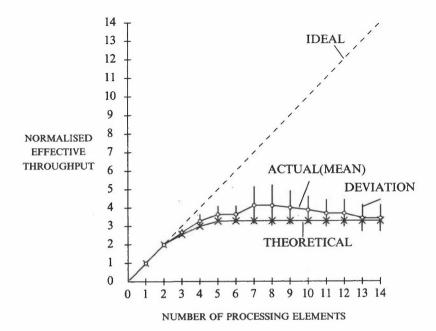

|      | 19.4 SOME PERFORMANCE MEASUREMENTS              | 273 |

|      | 19.5 CONCLUSIONS                                | 274 |

|      | 19.6 REFERENCES                                 | 275 |

| 20   | POLYPROC                                        |     |

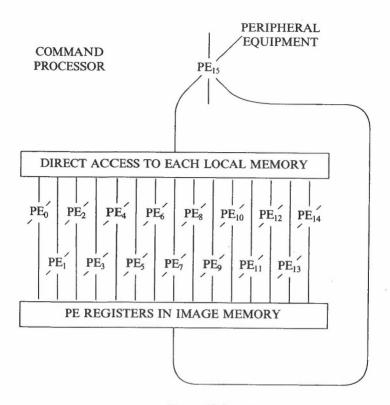

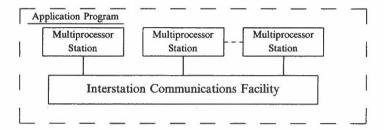

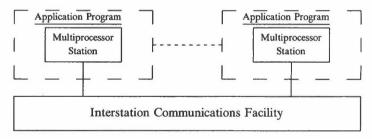

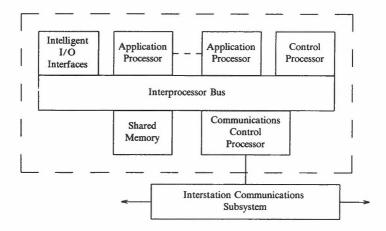

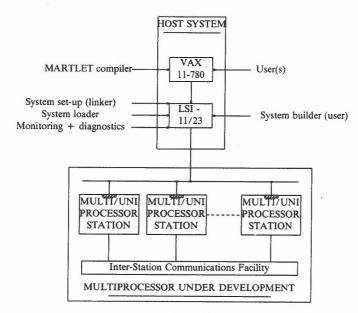

|      | 20.1 BACKGROUND AND AIMS                        | 277 |

|      | 20.2 A MULTIPROCESSOR DEVELOPMENT ENVIRONMENT   | 277 |

|      | 20.3 LABORATORY DEVELOPMENT FACILITY            | 284 |

|      | 20.4 DISCUSSION                                 | 287 |

|      | 20.5 REFERENCES                                 | 288 |

| Par  | t V Modelling and Verification                  |     |

| 21   | Using Algebra for Concurrency                   |     |

|      | 21.1 INTRODUCTION                               | 291 |

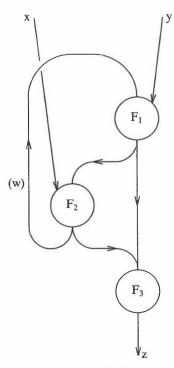

|      | 21.2 PIPELINING: KAHN NETWORKS                  | 292 |

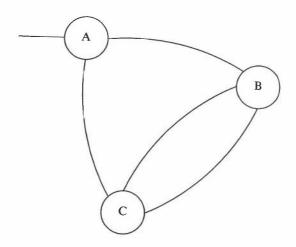

|      | 21.3 INTERACTING AGENTS                         | 295 |

|      | 21.4 PRODUCT OF AGENTS                          | 297 |

|      | 21.5 AN ALTERNATIVE AGENT PRODUCT               | 301 |

|      | 21.6 A BIGGER EXAMPLE                           | 303 |

|      | 21.7 CONCLUSION                                 | 304 |

|      | 21.8 REFERENCES                                 | 305 |

| 22   | Reasoning About Concurrent Systems              |     |

|      | 22.1 INTERACTIVE PROGRAMS                       | 307 |

|      | 22.2 CONCURRENT PROGRAMS                        | 309 |

|      | 22.3 DYNAMIC NETWORKS                           | 313 |

|      | 22.4 TIME DEPENDENCY                            | 316 |

|      | 22.5 REFERENCES                                 | 318 |

| Inde | ex                                              | 321 |

# Part I

The Dataflow Approach

J. R. W. Glauert J. R. Gurd C. C. Kirkham I. Watson

# 1 Fundamentals of Dataflow

J. R. Gurd

#### 1.1 INTRODUCTION

It is becoming apparent that future requirements for computing speed, system reliability, software manageability and cost-effectiveness will entail the development of alternative computer architectures to replace the traditional 'von Neumann' organization on which our present computing practices are based. Dataflow architecture is one possible alternative which aims for high-speed computing via efficient exploitation of software parallelism in a highly parallel system of processing hardware. The name 'dataflow' is derived from the graphical model of computation which is used to describe how programs are executed. In this model data is active and flows asynchronously through the two-dimensional program, activating each instruction when all the required input data has arrived. This is in direct contrast to the 'von Neumann' model in which data passively resides in store whilst instructions are executed one-at-a-time according to a defined sequence controlled by a 'program counter'.

Dataflow architectures, as described in this part of the book, are only one alternative to traditional computers. Several other models with similar characteristics are emerging, and these are sometimes confused with dataflow systems, usually because they too are driven by their data. In particular, string reduction and graph reduction systems fall into this category. In the following we will concentrate on 'pure' dataflow architectures.

This part of the book is divided into four chapters, covering fundamentals, hardware techniques, machine-level programming and high-level software. This first chapter opens with a discussion of the nature of software parallelism, the possible ways of representing it, and some implications for parallel machine-code design. This provides an introduction to dataflow notation and also demonstrates the important distinction between static and dynamic dataflow systems. The chapter concludes with a discussion of techniques for compiling from various high-level programming languages into dataflow object-code.

In Chapter 2 on hardware we consider the requirements for executing dataflow code and exploiting the exposed software parallelism. We then study three different system designs which have been, or are being, constructed as experimental research vehicles for further work applying and refining dataflow techniques. The chapter closes with a discussion of dataflow system performance.

Chapter 3, on machine-level programming, studies the languages which are used to specify graph programs for the Manchester Dataflow Machine. The lowest-level interface

is via a compact textual representation of the binary messages which are sent to load the program store. This is difficult for humans to use as a programming vehicle, and it is more normal to use the Template Assembler (TASS) which is also described.

Chapter 4 describes a specific high-level language for dataflow programming, SISAL, illustrated by a number of examples of language constructs and some complete programs. SISAL is a single-assignment language with Pascal-like syntax. It is currently being used for evaluation of a variety of multiprocessing strategies.

### 1.2 PARALLELISM IN SOFTWARE

Two kinds of parallelism can be found in software. The first kind occurs when a common operation (or set of operations) is to be applied to many separate sets of data. An example is the element-wise addition of several arrays, as in the Fortran program:

DO 10 I = 1,100

$$F(I) = A(I) + B(I) + C(I) + D(I)$$

10 CONTINUE

The second kind is found when different operations (or sets of operations) are to be applied to separate (or even common) sets of data. This may be found in many blocks of assignment statements, for example, the following Fortran code:

$$A = E - G$$

$B = H * Z$

$C = E * H + F$

$D = E + G$

These forms of parallelism have been known for a long time and their importance in influencing parallel hardware design has been recognized. Flynn [1] classified hardware systems as SIMD (single-instruction-stream, multiple-data-stream) if they exploit the first kind of software parallelism, and MIMD (multiple-instruction-stream, multiple-data-stream) if they exploit the second kind.

Nowadays this classification is considered overly simple, but no generally accepted alternative taxonomy is emerging. The difficulty seems to be that parallel hardware may be deployed at a different level of 'granularity' to the obvious software parallelism. For example, in an instruction pipeline, small parts of the execution of successive instructions are processed concurrently by overlapping, regardless of any program parallelism at the instruction level, or above. In the absence of a level-independent taxonomy of parallel systems comparison of different architectures is by *ad hoc* methods. We have found it useful to distinguish between 'regular' and 'irregular' parallelism when comparing the abilities of dataflow systems with those of more conventional parallel systems.

Regular parallelism exists wherever the same task is to be performed many times over, usually on disjoint data. With connected data it may be necessary to exploit regular parallelism via a pipeline, as in the instruction pipeline cited above. With unconnected data, as in the case of the first (SIMD) kind of software parallelism, a lock-step parallel array of hardware can be used, as in the DAP [2] or ILLIAC IV [3]. In either case, the actions to be performed concurrently are highly regular, and the performance of the systems depends critically on whether or not the program can provide sufficient work with the required amount of the required form of regularity.

Most of the parallel computers so far constructed exploit regular parallelism of one form or another. In practice it has proved surprisingly difficult to arrange for programs to provide, continuously, sufficient parallelism of the desired nature. Consequently applications run at variable speed, the regular parts executing rapidly, whilst other sections

are necessarily slower. In many cases the slow segments dominate overall performance and reduce the total speedup of programs to a small fraction of that intended.

Irregular parallelism exists wherever different tasks are potentially concurrently executable, sometimes on common data. This corresponds to the second (MIMD) form of software parallelism. An independent array of parallel hardware, such as in the CDC 6600 [4] (on a small scale) or the C.mmp [5] and Cm\* [6] multiprocessors (on a large scale), is needed for implementation. Where common data is involved complex interlocking mechanisms are necessary to prevent unintentional accesses being made (e.g. reading data before it has been defined, or writing before all prior reads have been completed). Note that hardware mechanisms which exploit irregular parallelism will also be able to handle regular parallelism. The reverse is not usually the case.

Few systems have been constructed to exploit irregular parallelism on a large scale, and it is in this area that many interesting experiments in computer architecture are now being conducted. The best known examples use parallelism at the 'process' level, derived from programming languages such as Concurrent Pascal [7], Modula [8], Distributed Processes [9], and Communicating Sequential Processes [10] and implemented on shared-memory or message-passing multiprocessors. Dataflow systems exploit irregular parallelism at a lower level, approximating to the conventional machine-code instruction-level.

Whether parallelism is regular or not, the key issue in developing a system to exploit it is to provide an effective notation for expressing potential parallelism in programs. In the following section we develop a notation for instruction-level irregular parallelism by examining the nature of inherent parallelism in a small segment of conventional Fortran code.

#### 1.3 PROGRAMS AS GRAPHS

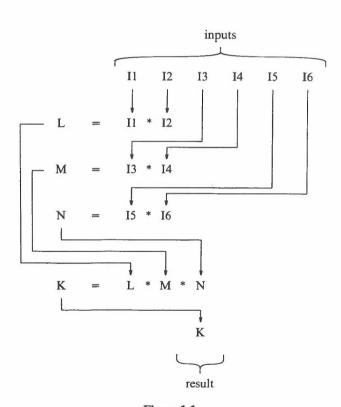

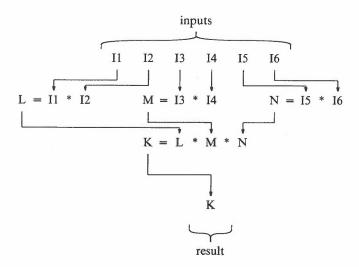

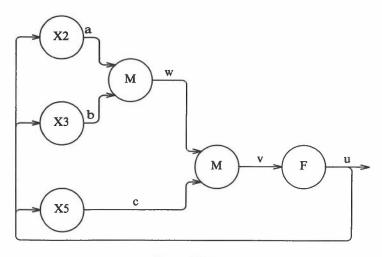

Consider the following set of Fortran assignments which multiply together the 'variables' I1, I2, I3, I4, I5 and I6 and put the result in 'variable' K:

L = I1 \* I2 M = I3 \* I4 N = I5 \* I6 K = L \* M \* N

To discover the potential software parallelism we must discard the traditional view of a program as a list of instructions which manipulate data in fixed storage locations in a defined sequence. Instead we need to concentrate on the role the individual storage locations play as they temporarily hold data values whilst the latter pass between operations in the program. The pattern of store accesses brought about by the sequence of activation of instructions is normally contrived by the programmer to achieve the combinations of data with operators dictated by the particular problem being solved. The fact that this is specified as a one-at-a-time process owes more to the history of the development of computers than to inherent constraints in the problems that computers are used to solve.

# 1.3.1 Data Dependence Graphs

An alternative view of the combination of data with operators is obtained by constructing a data dependence graph for the program [11,12]. Algorithms for this task are in common use for conventional machines in optimizing compilers. In the example above, we simply draw a number of arcs over the program, one arc for each variable. The tail of an arc shows where the variable is assigned, and the head shows where the variable is

consumed (by appearing on the right-hand side of an assignment statement). In more complex examples more than one arc may be required for a variable when it appears on the right-hand side of more than one assignment statement. Multiple assignments, where a variable is assigned a value at more than one point in the program, can be dealt with by systematically renaming the variables so that a version is created without multiple assignments, but with the same meaning as the original. Where variables appear only on the right-hand side they are assumed to be input data to the program segment. The resultant graph for our example is shown in Figure 1-1.

This diagram is more visually attractive if it is rearranged to show enforced sequence down the page, with potential concurrency across the page, as shown in Figure 1-2.

In this graphical form it is possible to omit all the variable names as they are now superfluous, being constrained to be the same at head and tail of each arc. If names are required (as an aid to understanding, or for writing a textual version of the graph), they can be written just once, alongside the appropriate arc. Each assignment statement can be simplified to a description of the expression to be computed. In many cases this will be a simple arithmetic operation, as in the case of the multiplication in our example, shown in Figure 1-3.

Figure 1-1

Figure 1-2

Figure 1-3

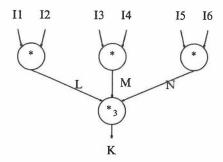

# 1.3.2 Machine-Level Graph Programs

We have now constructed a simple statement-level data dependence graph. Note that it retains the meaning of the original program, but it also shows potential parallelism and enforced sequence in a two-dimensional format. In order to illustrate all the program parallelism available for exploitation by instruction-level parallel hardware it is necessary to decompose the program even further. Of course the level to which we descend is completely arbitrary. We could build a system capable of multiplying three values together in one instruction (in which case the above graph would not need further reduction), or we could go to the extreme of implementing only boolean operators (AND, OR, NOT, etc.) in hardware, and building up more complex operators using standard techniques (in which case our example graph would require considerable further decomposition). Most of the dataflow computers currently under construction use an instruction-level comparable to that of a 16-bit minicomputer with extended arithmetic capabilities. We shall assume this level in the remainder of this part of the book. This implies the availability of straightforward monadic and dyadic arithmetic operators on integer and floating-point numbers, and we will also assume the existence of operators which generate and

manipulate boolean values.

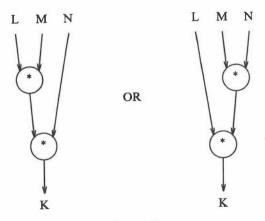

In our example program it will be noted that the lowest expression evaluation in the graph is not a machine instruction at this level. Consequently it must be implemented by a subgraph of instructions such as either of those shown in Figure 1-4.

In this particular example it is immaterial which of these alternatives is used, and a compiler could choose between them arbitrarily. In other cases there will be efficient and inefficient options and compilers will need to be sensitive to the assessment criteria if they are to produce optimal code under a wide range of conditions. To develop such assessment criteria we need to know how programs will actually execute on a specific parallel hardware configuration. This is too difficult to discuss in detail here, but we shall finish this chapter with a brief description of an abstract dataflow implementation model from which the basic principles of execution may be derived.

#### 1.3.3 Execution of Machine-Level Graphs

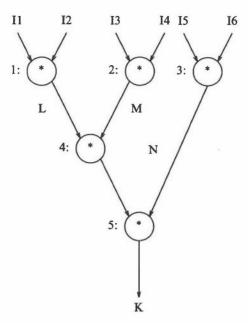

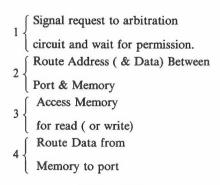

Consider a complete machine-level program graph for our example in which each multiply instruction is given an identification number, as shown in **Figure 1-5**. Remember that the purpose of this notation is to allow all potentially concurrent instructions to execute simultaneously. In the original sequential program we would expect the multiplications to be performed in the order {1}, {2}, {3}, {4}, {5}, producing the answer in five multiplication times. On the graph above we can see that either of the parallel execution orderings {1, 2, 3}, {4}, {5} or {1, 2}, {3, 4}, {5} will produce the answer in three multiplication times (given at least three and two multipliers, respectively). The problem for the parallel execution model is to cause one of these parallel execution orderings to be followed.

It is difficult to arrange activation of instructions by some parallel equivalent of a program counter. In the first place such program counters would have to be associated with processors, and the variable amounts of parallelism that could occur might require large numbers of these processors, many of which could frequently become idle. Secondly, the idea of a program counter is closely linked to the concept of a linear data store with fixed locations for each program variable. Large numbers of active instructions would

Figure 1-4

Figure 1-5

imply large numbers of active store locations with attendant problems of multiplexing the required accesses. In addition to this each horizontal 'band' of instructions would have to be synchronized so that the next lower band could not start processing until all current instructions had terminated. This implies that a program would proceed at the speed of the slowest operation in each band. Apart from these problems, the task of allocating instructions to processors would be extremely difficult.

These arguments constitute a compelling reason for abandoning program counters in instruction-level parallel computers. The key to making this transition is to notice that a data dependence graph shows how instructions are dependent on data. It is not sensible to execute an instruction before all the data it requires is available. Conversely, once an instruction has finished executing, all other instructions that are waiting for its output data can be activated safely. The simplest way to execute a graph program so as to obey these rules is to send data directly from instruction to instruction according to the data dependence arcs, and to allow each instruction to execute when and only when it has all its required input data available. In this way the graph program execution will be data-driven.

We can illustrate data-driven execution of graph programs by introducing data-carriers, known as 'tokens' after Petri-net notation [13], onto the data dependence graph. Each token carries one data value. A token is constrained to move (at any speed it can) from the tail to the head of one data dependence arc. Tokens wait at the heads of their dependence arcs until all other arcs (if there are others) pointing to the same instruction also have tokens at their heads. At this time this instruction can be executed, taking an arbitrary amount of time to complete, after which its result token(s) is(are) placed on its output arc(s). The tokens causing the execution are no longer needed, and so they will be removed from their (input) arcs.

The sequence of 'snapshots' in Figure 1-6 shows how our example program could be used to evaluate 6! by sending tokens with integer values 1 to 6 to the program inputs I1 to I6, respectively. Tokens are shown on the dependence arcs as black discs with the associated values written alongside. The way in which the data appears to flow through the program graph during execution is the reason for the name 'dataflow'.

#### 1.4 GENERALIZED DATAFLOW GRAPHS

The multiplication program considered above is not a general example of conventional computing practice. The only arithmetic operation used is multiplication and there are no control structures, such as conditionals or loops. In this section we consider enhancements to the dataflow notation which help to accommodate more general programs.

The first point to be made is that *any* form of machine instruction can be represented by a node in a dataflow graph and could therefore be executed in parallel with other instructions. This property makes the graph notation useful for exploiting irregular software parallelism. The simplest case in which this is advantageous is in the evaluation of general arithmetic expressions in which any arithmetic machine instructions could be

Figure 1-6

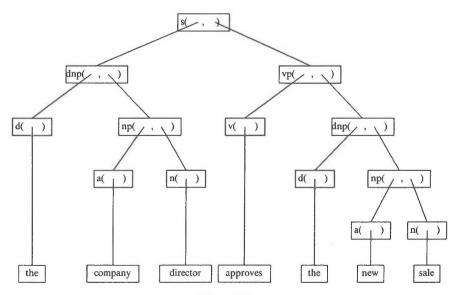

used. Such expressions can be converted easily into graphs. In fact most conventional compilers already generate 'expression evaluation trees', when parsing high level programs, before they generate the required linear object code. The dataflow execution model demonstrates how such trees may be evaluated directly, in time proportional to their height, using parallel instruction execution. At a higher level, the model also allows whole expressions to be evaluated concurrently. Additional parallelism can be found when control structures are invoked.

#### 1.4.1 Conditionals

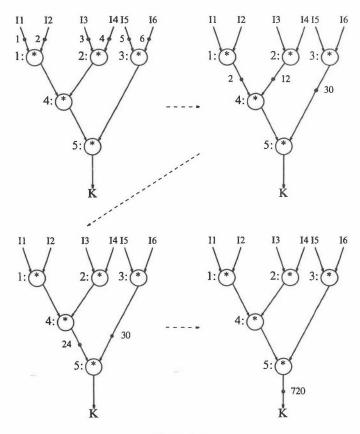

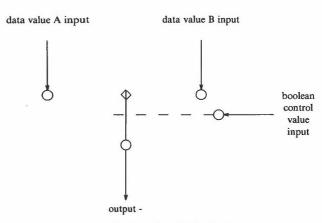

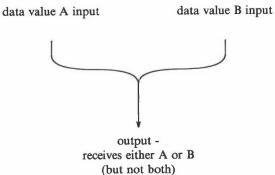

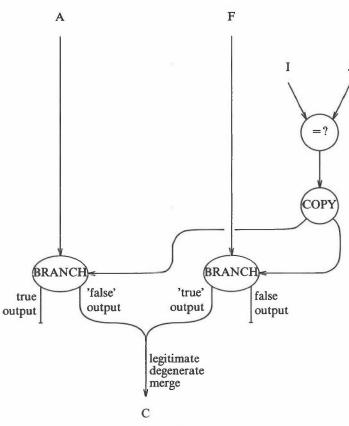

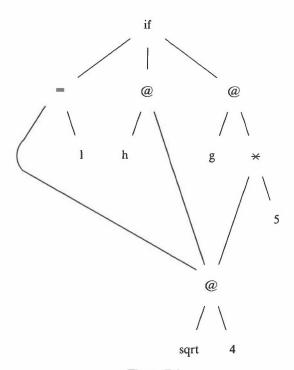

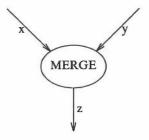

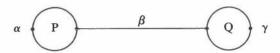

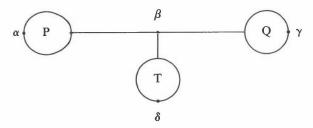

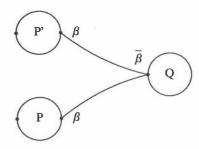

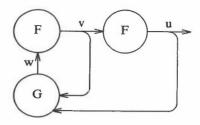

The simplest control structure is the conditional (if ... then ... else ... fi). We can construct a data dependence graph for a conditional statement using conditional dependence arcs which are controlled by the runtime evaluation of a boolean predicate. These arcs are implemented using the two 'switching' machine instructions, known as branch and merge, shown in Figure 1-7 and Figure 1-8.

These may be visualized as two-way switches inserted into the arcs of a standard dependence graph. Each switch selects one of two possible routes for an incoming data token, the other route being left inactive. The route is selected according to the value of

Figure 1-7

receives data value A if boolean is true or data value B if boolean is false

Figure 1-8

a boolean control token. The data and control tokens wait for each other at the inputs to the switch exactly as they would at a dyadic or triadic arithmetic instruction. Where it is certain that only one of the data inputs to a *merge* instruction will be generated, and in proper correspondence to the associated boolean (e.g. from a previous *branch* instruction using the same control value), the *merge* may be omitted from the machine code and the two data arcs conjoined, as shown in Figure 1-9.

Using the extended instruction set we can implement a conditional Fortran statement such as:

$$C = A$$

IF (I .EQ. J)  $C = F$

by the graph shown in Figure 1-10 in which '⊥' indicates that tokens travelling down this arc will be destroyed, and the '=?' instruction generates a boolean value indicating whether its two data inputs are equal.

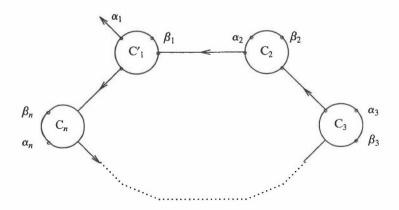

# **1.4.2 Loops**

Switch instructions are most powerful when used to implement graphical loops and functions. These are important because they allow complex computations to be defined by relatively small programs, in the same way as conventional loops, subroutines or procedures. However, these reentrant constructs pose substantial implementation problems in a parallel computer because of the possibility of simultaneous activation of the reentrant code.

Figure 1-9

Figure 1-10

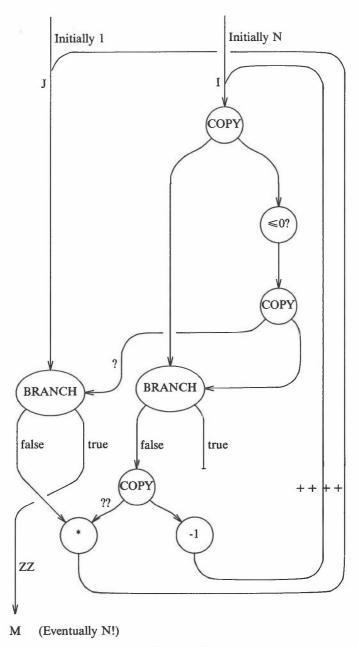

As an example, consider the Fortran program segment below:

```

I = N

J = 1

10 IF (I.LE. 0) GOTO 99

J = I * J

I = I - 1

GOTO 10

99 M = J

```

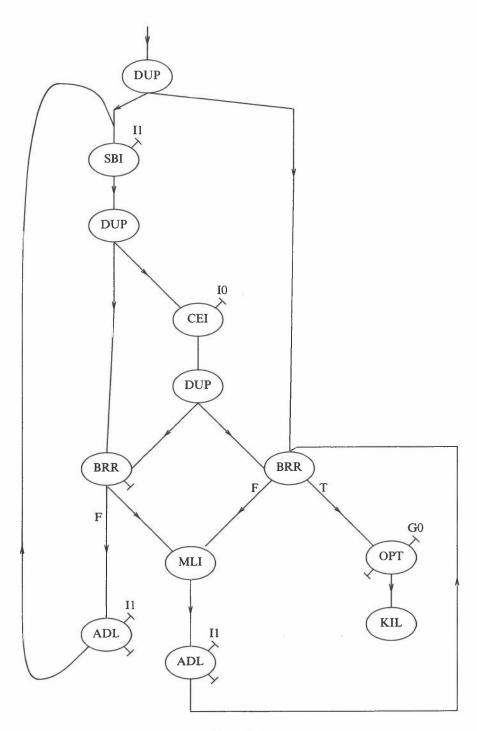

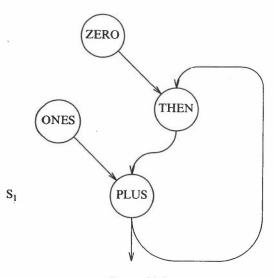

This is an iterative program which computes values of N! for variable N (i.e. not just 6!). It translates into the machine-level graph of Figure 1-11. Detailed analysis of this graph reveals that it is possible for more than one token to occupy the arcs labelled "?" and "??". Consequently, it is essential that the arcs of the graph behave as first-in-first-out queues (otherwise the loop could terminate early because of overtaking on the arc labelled "?"). Unfortunately implementation of unbounded queues proves to be difficult, so it is usual in practical dataflow systems to restrict the normal 'firing rule' so that instructions can only be executed when their output arc is empty.

This is the simplest way of implementing reentrant graph programs, but it is not completely general because it prohibits concurrent reentrancy. It only permits loops which are reactivated in strict sequence. Although a limited amount of parallelism can be obtained by pipelining within the cycles of a loop, there is often further parallelism which can only be extracted by a more general scheme (as described in the next two sections). Systems which implement this first scheme, allowing only sequential, cyclic reentrancy, are known as *static* dataflow systems [14].

#### 1.4.3 Functions

A typical case in which concurrent reentrancy is required is when the programmer defines a function (i.e. a user-defined subgraph) which is to be called from several places within the program. This is somewhat similar to a Fortran subroutine. It is, of course, possible to create many copies of the machine code representing the function and to plant them 'in-line' at the appropriate places. However, this is wasteful of instruction storage for large functions and those which are called frequently. It also prohibits the use of recursion since this implies provision of infinitely expanded program graphs. Consequently, two alternative implementation schemes for reentrant programs have been proposed.

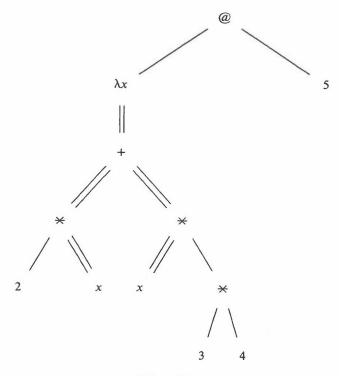

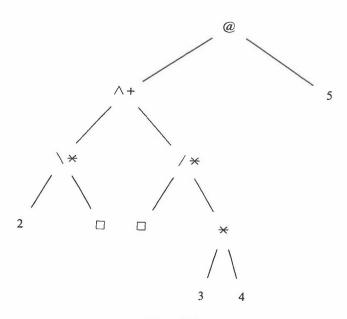

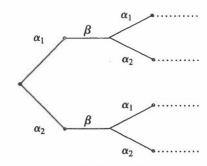

The first such scheme permits concurrent reentrancy via an apply instruction, planted at the start of a user-defined subgraph, which creates a new copy of the subgraph each time it is activated [15]. All input tokens to a subgraph activation are gathered together at the apply instruction and are then transferred to the unique new copy of the reentrant code. An exit instruction, placed at the end of the copy of the subgraph, gathers together all the output tokens for the activation and transfers them back to the output arcs of the appropriate apply instruction. The copy of the reentrant code is then destroyed. The operation of this scheme is analogous to conventional macro-expansion in that extra code and data space is allocated whenever it is called for. This avoids data having to share code concurrently.

An alternative scheme allows data to share code by 'tagging' tokens as they enter into and exit from the reentrant areas [16, 17]. This system is similar to the use of a stack for implementing procedures and functions on conventional machines, except that the concurrent activation of shared graph code requires that each token be *individually* tagged with the appropriate 'name-base' instead of using global stack registers to identify the

Figure 1-11

currently active data space. In visual terms tagging can be thought of as the process of colouring the data tokens [18]. The graph execution rules need to be modified so that only tokens of the same colour (i.e. those carrying identical tags) can group together to cause execution of an instruction. Special instructions are needed to create new tags at

entry to, and to restore old tags at exit from, the reentrant code. Of course, tokens must carry extra bits to denote the tag.

Note that token-tagging can be used to distinguish data belonging to different cycles around a loop. For example, in the program shown in Figure 1-11, assuming all input tags have value zero, the tags could be incremented each time round the loop at the points labelled '++', and zeroed on exit from the loop at the point labelled 'ZZ'. In this case it is no longer necessary for the arcs to act as first-in-first-out queues, and the 'firing rule' can be derestricted.

Systems using the above schemes to implement concurrently reentrant functions are known as *dynamic* dataflow systems. The first scheme is called the *dynamic code-copying* scheme. The second scheme is known as the *dynamic tagged*, or *dynamic code-sharing* scheme. Hybrid dynamic systems use both code-sharing and code-copying in order to limit the size of the tag.

#### 1.4.4 Structured Data

Compact programs can also be written using data structuring, by which a single variable name is used to refer to a large collection of simple data items. Two schemes have been developed to implement data structures in dataflow graph programs.

The first scheme uses separate storage to hold the structures and represents each structure travelling in the program graph by a *pointer* token. A specialized *structure store* is responsible for executing read and write operations on structures, and also for issuing the appropriate pointers [19]. All other instructions are as described above, and operate on scalar data, or control the flow of pointer tokens through the program graph.

An alternative scheme uses the tagging system described in the previous section [20]. Each element of a data structure is a normal token which carries a unique tag defining the position of the element in the structure. Tag-sensitive instructions are used to manipulate the structure in the required way. This scheme is particularly useful for implementing regular structures, such as arrays, whose elements are all subject to continuous processing (as, for example, in signal processing applications).

#### 1.5 COMPILATION OF GRAPH CODE

The examples introduced earlier demonstrate that it is possible to generate dataflow graphs from a conventional high-level programming language such as Fortran. However, the analysis algorithm that forms data dependence graphs from such languages is highly complex and takes a long time to execute. There exist other languages which are easier to translate and these are receiving the majority of attention in dataflow research projects.

# 1.5.1 Conventional Languages

The principal difficulties with conventional languages reside in possible side-effects due to explicit use of storage locations (accessed by the programmer as 'variables'). Data dependence analysis is often hampered by obscure array index expressions which are impossible to analyse at compile-time and thus requires some assistance from the programmer to indicate how the arrays will be accessed. However, the worst problem is that of aliasing via the use of unbounded arrays or arithmetic operations on pointers. No amount of compile-time analysis can help unravel devious or undisciplined use of such language 'features'. The only method of control is to ban the facilities from the language [21].

## 1.5.2 Single-Assignment Languages

Single-assignment languages (SALs) have no concept of sequential execution and no direct control statements such as the GOTO. To combat the ambiguities that might arise from reassigning values to variables, the languages allow each variable to be assigned just once in a program. Constructs which permit controlled reassignment in special cases, such as loops, are provided. SALs tend to use data structures, such as arrays and streams, that can be readily implemented in dataflow graphs. There are often strict type and scope rules. In particular, it is common to prohibit all forms of side-effect in reentrant constructs. The net results are languages that provide ideal textual syntax for the description of dataflow graphs [22, 23, 16, 24, 25].

Many SALs were developed without reference to dataflow execution, and they are similar to the *functional* or *applicative* languages which have been developed without reference to any particular means of execution.

## 1.5.3 Functional Languages

Functional languages are based on the mathematics of functional algebra and have no concepts of storage state and assignment [26]. They are sometimes referred to as zero-assignment languages. In fact, if assignment is restricted to occur only once for each variable in a program, the effect is the same as if there were no assignment at all and 'assignment' statements were treated as definitions of the variables. In this sense SALs and functional languages are identical and it should come as no surprise to find that absence of GOTOs and side-effects are common to them both. However, functional algebra allows more powerful programming constructs than are used in SALs because it permits construction of higher order functions and abstract data structures. Consequently the two groups are not directly equivalent. Nevertheless they have enough in common to make it attractive to implement functional languages on dataflow systems.

Several attempts have been made to compile dataflow code from higher order functional languages [27]. These indicate that it is possible to implement such languages fully, but there are many doubts as to the efficiency of programs produced in this way. Recent research has concentrated on developing mixed data-driven/demand-driven architectures for such languages [28].

#### 1.6 SUMMARY OF DATAFLOW GRAPHS

Dataflow graphs are a convenient notation for representing parallel computations. They permit conditional constructs, loops, functions (including recursion), and data structuring. Translation to dataflow graphs is feasible from a wide range of high-level programming languages.

There is a natural classification for dataflow systems according to the way they handle reentrant code. The three classes of system are known as *static*, *dynamic code-copying*, and *dynamic tagged* schemes.

#### 1.7 REFERENCES

- 1. M. J. Flynn, "Some Computer Organisations and Their Effectiveness," *IEEE Transactions on Computers* C-21(9), p.948 (September 1972).

- 2. S. F. Reddaway, "DAP A Distributed Array Processor," *Proceedings of 1st ACM Symposium on Computer Architecture* (December 1973).

- 3. G. H. Barnes et. al., "The ILLIAC IV Computer," *IEEE Transactions on Computers* C-17(8), p.746 (August 1968).

- 4. J. E. Thornton, Design of a Computer: The CDC6600, Scott Foresman & Co (1970).

- 5. W. A. Wulf and C. G. Bell, "C.mmp A multi-mini-processor," *Proceedings of AFIPS FJCC* 41, p.765 (September 1972).

- R. J. Swan, S. H. Fuller, and D. P. Siewiorek, "Cm\* A Modular Multimicroprocessor," Proceedings of AFIPS NCC 46, p.637 (June 1977).

- 7. P. Brinch Hansen, "The Programming Language Concurrent Pascal," *IEEE Transactions on Software Engineering* SE-1(2) (June 1975).

- 8. N. Wirth, "Modula: A Language for Modular Multiprogramming," Software Practice & Experience 7(1), p.3 (January 1977).

- 9. P. Brinch Hansen, "Distributed Processes: A Concurrent Programming Concept," Communications of the ACM 21(11), p.934 (November 1978).

- 10. C. A. R. Hoare, "Communicating Sequential Processes," Communications of the ACM 21(8), p.666 (August 1978).

- 11. F. E. Allen and J. Cocke, "A Program Data Flow Analysis Procedure," Communications of the ACM 19(3), p.137 (March 1976).

- 12. D. J. Kuck et. al., "Dependence Graphs and Compiler Optimisations," *Proceedings of 8th ACM Symposium on Principles of Programming Languages*, p.207 (January 1981).

- 13. J. L. Peterson, "Petri Nets," ACM Computing Surveys 9(3), p.223 (September 1977).

- 14. J. B. Dennis and D. P. Misunas, "A Preliminary Architecture for a Basic Data Flow Processor," *Proceedings of 2nd IEEE Symposium on Computer Architecture*, p.126 (January 1975).

- 15. G. S. Miranker, "Implementation of Procedures on a Class of Dataflow Processors," *Proceedings of International Conference on Parallel Processing*, p.77 (August 1977).

- Arvind, K. P. Gostelow, and W. Plouffe, "An Asynchronous Programming Language and Computing Machine," Technical Report TR114a, Department of Information and Computer Science, University of California at Irvine (December 1978).

- 17. I. Watson and J. R. Gurd, "A Prototype Data Flow Computer with Token Labelling," *Proceedings of AFIPS NCC* 48, p.623 (June 1979).

- 18. J. B. Dennis, "First Version of a Dataflow Procedure Language," Lecture Notes in Computer Science 5, p.187 (1974).

- 19. D. P. Misunas, "Structure Processing in a Dataflow Computer," *Proceedings of Sagamore Conference on Parallel Computation* (August 1975).

- 20. Bowen D.L, "Implementation of Data Structures in a Dataflow Computer," Ph.D. Thesis, Department of Computer Science, University of Manchester (May 1981).

- Arvind and R. A. Ianucci, "A Critique of Multiprocessing von Neumann Style," Technical Memo 226, MIT Laboratory for Computer Science (1983).

- W. B. Ackerman and J. B. Dennis, "VAL A Value-Oriented Algorithmic Language Preliminary Reference Manual," Technical Report 218, MIT Laboratory for Computer Science (June 1979).

- 23. W. B. Ackerman, "Dataflow Languages," *IEEE Computer* 15(2), p.15 (February 1982).

- 24. J. R. W. Glauert, "High Level Languages for Dataflow Computers," *Pergamon-Infotech State of the Art Report on Programming Technology*, p.173 (March 1982).

- J. McGraw, S. Skedzielewski, S. Allan, D. Grit, R. Oldehoeft, J. R. W. Glauert, I. Dobes, and P. Hohensee, "SISAL - Streams and Iteration in a Single-Assignment Language," Language Reference Manual Version 1.0, Lawrence Livermore National Laboratory (July 1983).

- J. Backus, "Can Programming be Liberated from the von Neumann Style? A Functional Style and its Algebra of Programs," Communications of the ACM 21(8), p.613 (August 1978).

- 27. G. Richmond, "A Dataflow Implementation of SASL," M.Sc. Thesis, Department of Computer Science, University of Manchester (October 1982).

- J. Darlington and M. Reeve, "ALICE: A Multiprocessor Reduction Machine for the Parallel Evaluation of Applicative Languages," *Languages and Computer Architecture* (October 1981).

# 2 Architecture and Performance

I. Watson

#### 2.1 INTRODUCTION

The dataflow model represents a parallel computation as a directed graph removing any requirement for unnecessary sequencing. If the model can be mapped on to a physical machine structure it should be possible to overcome many of the problems which have been encountered in the design of parallel machines based on more conventional computational models in which sequencing is fundamental. We will consider a variety of approaches to machine design in an attempt to explain how the architecture of current dataflow machines has arisen.

An equally important feature of the dataflow approach is the development of a parallel programming style which retains the power of current programming languages but removes any necessity to express parallelism explicitly and requires no knowledge of the machine structure. Although conventional high level programming languages reflect the basic sequential nature of the machines which execute the compiled code, the details of more complex architectural features (instruction pipelines, virtual memory etc.) are usually completely hidden. There is much evidence that, if the programmer is required to take account of machine level features (vectorization, overlays etc.), then the programming task becomes significantly more complex and error prone. This situation can only be compounded by the introduction of parallelism. It will be seen that this attempt to hide the physical structure from the programmer has a significant influence when considering practical implementation.

# 2.1.1 Existing Parallel Machines

A great deal of work has been done on parallel computer structures. Before considering a completely new architectural approach we should first consider the two major types of 'conventional' parallel computer architecture to see if the dataflow model is relevant.

Array processors (e.g. DAP [1]) have been designed to exploit the parallelism which exists in problems where similar operations can be performed on every element of an array concurrently with each processor executing the same sequence of instructions. This 'single instruction stream, multiple data stream' parallelism is only a small subset of that which can be expressed in dataflow form and a machine structure of this type is unsuited to the general case.

A 'multiple instruction stream, multiple data stream' capability is necessary in order that different processing resources can be executing different operations at the same time. A large number of machines of this type have been proposed and a significant number built, for example C.mmp [2] and Cm\* [3]. They usually consist of a number of conventional processors, each with their own program and data stores connected together via either a common store or a communication network (crossbar switch, common bus, slotted ring etc.). They are intended to be programmed in a relatively conventional language such as Modula [4] which has facilities for expressing communication between parallel processes. The user is required explicitly to divide a program into suitable parallel sections which can be mapped on to the physical machine structure.

This view of computation not only places a severe burden on the user but also constrains the architecture. The communication between processes is bidirectional and is unpredictable both in peak and average bandwidth. In order to produce satisfactory performance, an architecture is required which allows very high speed communication between random processors in the network. In practice the machine designers have compromised assuming that the data rates could be controlled and hence the machines have failed to realize their potential. This is not surprising as such random high speed communication is very difficult to achieve.

If a viable architecture of this type were developed then the dataflow approach with its software advantages would certainly be applicable to such a structure. However, the constraints imposed by the communicating process view of parallel computation are relaxed in a dataflow environment and it is possible to consider more realistic physical implementations of MIMD computers.

#### 2.1.2 Fine Grain Versus Coarse Grain Parallelism

It is clearly possible to apply dataflow principles over a wide range of problem structures from individual machine operations to processes at the level discussed above. If the correct process divisions are chosen then it is probable that the communication bandwidth for a given rate of computation will be minimized.

Conversely, if a low level is chosen then the number of inputs required before an operation can be executed will be smaller and hence the mechanism required to detect this condition in a physical machine will be simplified.

It is also necessary to consider how the machine is to be programmed. With a small number of notable exceptions (e.g APL), programming languages express computations at a relatively fine grain level of operation. Although there are many worthwhile attempts to produce 'very high level' programming languages they still retain the capability of performing scalar addition etc. If these operations are required for general purpose computation then this is the level at which the programmer will compose at least some portion of his code. If a number of such operations must then be 'bundled' for execution by the machine then this would need to be automated if the programming philosophy is to be maintained. Of course, the natural function/procedure divisions may be appropriate to minimize communication, but they may not. The automation of the task then becomes complex.

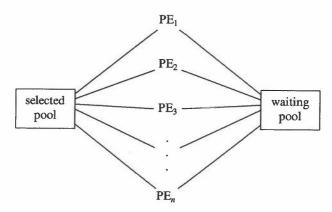

A further factor in the decision is the choice of static or dynamic task allocation. This is particularly important if coarse grain parallelism is considered. If high level operations are allocated to processing resources statically at the start of the problem execution, then each processor need only have access to the code which it will execute. In a dynamic scheme there is a requirement for access to the whole program from each individual processor. If each contains all the code, this could be a large overhead in storage, but if large portions of code are passed around dynamically this increases the bandwidth

requirements and the overheads of process allocation. In order that efficient use is made of parallel resources, it is important that they do not become idle, the chances of idleness are significantly increased in a scheme which allocates processes statically using coarse grain parallelism.

The choice is not straightforward, and this is reflected in the machine structures that have been proposed and constructed. On balance, it appears that the fine grain parallel-ism approach is winning but this may only be a temporary lead.

#### 2.2 MACHINE TOPOLOGIES

An obvious physical realization of a dataflow machine could consist of a processor for each computational node on the graph together with a reconfigurable communication network to provide the interconnections. There are two objections to this. Such a system would be grossly inefficient because inactive nodes would result in inactive processors. This might be overcome if several nodes were allocated to each processor. However, the complexities of the required communication are such that no physical machine based on these principles has been attempted.

An abstraction from the 'physical' interconnection of the dataflow graph can lead to more realistic structures for physical machines. If each node is allocated a unique identifier, the interconnections can be held in a node description as the identifier of the next node (together with an input number) to which data will be sent when computed. It is then possible to replace the explicit interconnection paths by a generalized communication network. A data value, when computed, uses the next node information as a routing director to find the processor which contains the required operation. It should now be clear how such a technique would allow a dataflow program to be mapped on to a conventional multi-processor where a number of nodes are statically allocated to each of the processors.

At this point it is worthwhile noting that the communication required is essentially uni-directional. A result value is computed and the computational resources used can be released to another task immediately. No reply is needed and, as long as the processor which contains the destination node has other work to do, the transit time to the destination is not critical. It should also be noted that there is no requirement to maintain ordering through the communication network. It is these aspects of the dataflow model which relax the architectural constraints on the physical structure and render the crossbar-switch approach to multi-processor design unnecessary.

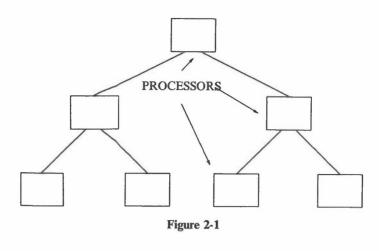

#### 2.2.1 Tree Structures

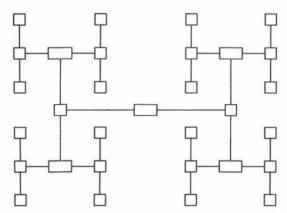

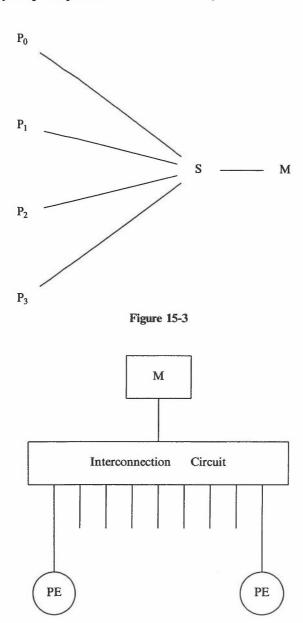

A large number of computational problems have the property that they start slowly, build up to a crescendo of activity, and then collapse to produce a relatively small result. This has led to an interest in tree structured machines, an example of which, using a binary tree, is shown in **Figure 2-1**.

A major reason for the interest in this physical structure is the ease with which it could be mapped on to VLSI using 'Recursive H' techniques. Figure 2-2 shows the basic principles of this method.

Although other computational models are also applicable, it is possible to see how a dataflow computation might map on to such a structure. The initial nodes are placed at the root of the tree and, as they produce their results, they are passed down, eventually reaching the leaves where maximum activity takes place. As the computation collapses the results can be passed back to the root. Unfortunately, as one might imagine, it is almost impossible to devise a general strategy whereby a computation can be mapped

Figure 2-2

statically on to such a structure so as to produce sensible use of the resources.

A dynamic allocation scheme is necessary. If the root processor holds a complete description of the dataflow graph, it can decide from the results which it produces which areas of the graph are to be activated next; and pass these together with the data to its sub-processors. If the distribution strategy is carefully chosen, then the computation could spread itself nicely over the structure.

A machine which operates in this way was conceived and partially constructed by Al Davis at the University of Utah. One processing node became operational in 1978 [5] and using information about the characteristics of this a complete structure was evaluated by simulation. The results of this work indicate that many problems still exist in this approach. Not only does the distribution occupy significant resources, but also the strategy is still complex. Computations which appear to become very active may cease due to run-time conditions which cannot be predicted and large sections of the physical tree which have been allocated may suddenly become idle. The limited communication available then makes re-distribution of the computation a very inefficient task. A further problem arises when the leaves of the tree are reached and processors discover that they

are in possession of a rapidly expanding section of the code.

Recognizing these difficulties there have been several proposals for machine topologies which can be classified as 'virtually tree structured' [6]. The physical machine structures can be viewed as 'folded trees' so that the communication is more general. Most of these ideas have not aimed at dataflow, but the more recent related area of Reduction Machines for the implementation of functional languages. It remains to be seen whether practical implementations of these ideas will work. There are still overheads of task distribution and unfortunately many of the physical interconnection schemes are not obviously suited to VLSI implementation.

## 2.2.2 Ring Structures

The tree structured approach to machine design has been driven by the possibilities of highly parallel computers which exploit the potential of VLSI technology; the dataflow computational model is then viewed as a possible method of using these machines.

An alternative approach is to take the dataflow model as the driving force and design machines which make maximum use of its capabilities. The particular technological constraints of VLSI, although important, should only be addressed when the feasibility of these parallel structures is fully understood. This has resulted in a variety of ring-structured dataflow machine designs.

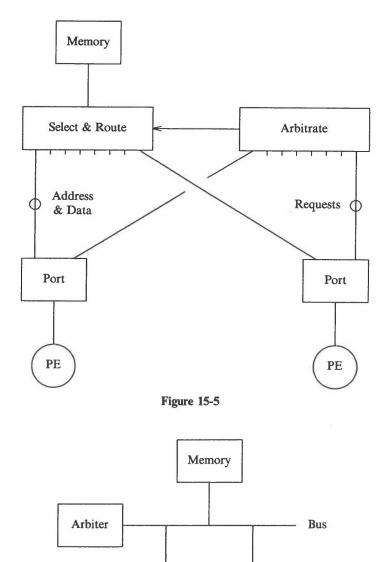

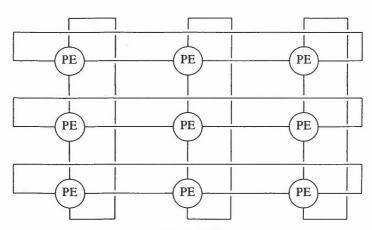

The most serious problem in any multi-processor structure is the provision of a flexible interconnection scheme with high bandwidth. The uni-directional communication property and the lack of a requirement for very rapid transit time between processors are exploited in ring-structured dataflow machines to overcome this problem. Figure 2-3 shows the basic outline of such a machine.

A processor is assumed to contain:

- (1) A description of the dataflow graph.

- (2) A mechanism for assembling incoming data into complete packets for execution.

The switching mechanism is composed of individual 2×2 switches, each of which contains buffers at its input to hold incoming data. Routing information within the data packet indicates which of the switch outputs it is directed towards. The overall structure is therefore effectively a set of parallel pipelines. An N input, N output switch requires N/2(log N) individual elements and any route through the switch is a log N stage pipeline. It can be shown that, assuming random contention for switching resources, such a structure achieves a throughput bandwidth which approaches its theoretical maximum. However its complexity is manageable in a practical implementation. As the communication is uni-directional, the only price paid is the pipeline delay between processors. As long as the processors are kept active and the pipeline is kept full by parallelism in the program, then no degradation of performance should result.

This structure has been presented without any mention of the exact dataflow computational model used or the level of granularity employed. The basic structure is largely independent of these factors and as such has formed the basis of most of the major dataflow machines which have been, or are in the process of being, constructed. The differences between these machines are reflected in the detailed structure of the processors.

Figure 2-3

## 2.3 PRACTICAL MACHINES

Although it has been mentioned that the dataflow principle is applicable to any level of granularity and the choice is not immediately obvious, all the major projects have chosen to implement the model at the level of simple machine instructions. The prevailing view amongst those closely involved is that programming languages require this. Others believe that the major impact of dataflow ideas will be at a higher level. Whatever the final outcome, the projects which are currently in progress are providing a great deal of useful information in the area of parallel machine design. It is worthwhile therefore to examine some of the architectures in more detail.

#### 2.3.1 The MIT Static Dataflow Machine

A machine which uses the static dataflow model of computation is being implemented currently by a team led by Jack Dennis at MIT. It uses bit-sliced microengines connected via a general purpose unidirectional routing network [7]. In this system the three major dataflow tasks of:

accessing the program description; gathering tokens to produce executable packets; executing instructions;

are implemented in software in the processor modules.

A key factor in the design of the MIT system is the ability to expand its power by adding extra processors via an extended communications switch.

The desire to expand power by adding hardware is common to all dataflow system designs. There is keen debate about the maximum size of switch that can be constructed (or that will be feasible in the forseeable future). There is an obvious relationship between the power of individual processors, the total power, and the size of the switch. Because the MIT system uses conventional microprocessor software to emulate the dataflow model, it runs relatively slowly and large switches will be needed for substantial applications (e.g. weather forecasting). It is envisaged in the MIT design that switches of size  $500 \times 500$  and more can be implemented using byte-wide  $2 \times 2$  routers.

Other researchers are less confident that switches of this size will be practicable. Consequently they have concentrated on improving the execution rates of individual processors by designing their internal structure to be dataflow oriented.

## 2.3.2 The MIT Dynamic Dataflow Machine

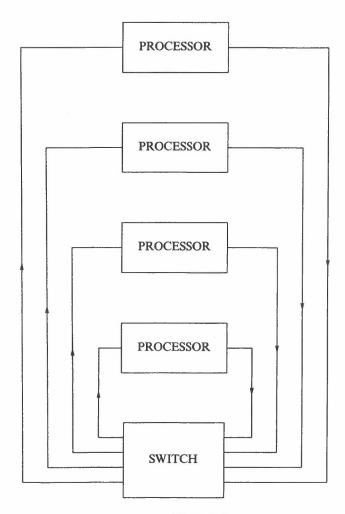

Another research group at MIT, under the leadership of Arvind, is constructing a VLSI-based dataflow processor with many of the characteristics of the ring-structured system. The main features of this system are that (1) data structure accesses are handled separately from ordinary token activities, and (2) there is a two-tiered communication system [8]. The processor design is outlined in Figure 2-4.

The three major dataflow activities are handled by separate hardware, in particular the token gathering operation is performed by a small associative store. Data structure operations are treated separately so that (1) they can be performed quickly, and (2) the potentially large numbers of tokens involved do not occupy space in the expensive unmatched-token store. The two-tiered communication structure relieves the general communications switch of excess traffic as long as programs exhibit strong 'locality' (i.e. processing activity is localized in subgraphs and processors rather than communicating randomly with other subgraphs/processors). Locality also benefits the size of the unmatched-token store, and current plans at MIT are to implement a small 64-word store.

Reduced traffic in the communications switch allows bit-wide data paths to be used. The proposed building block for this MIT system is an  $8\times8$  bit-wide module. Using program locality still further, large-size switches can be made rather less complex than the networks proposed for other systems.

This design relies heavily on strong program locality. The language Id [9] also developed by Arvind's team, has appropriate properties, and the system is being designed around this language.

Figure 2-4

### 2.3.3 The Manchester Dynamic Dataflow Machine

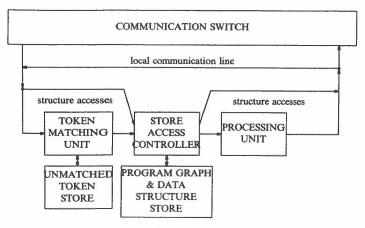

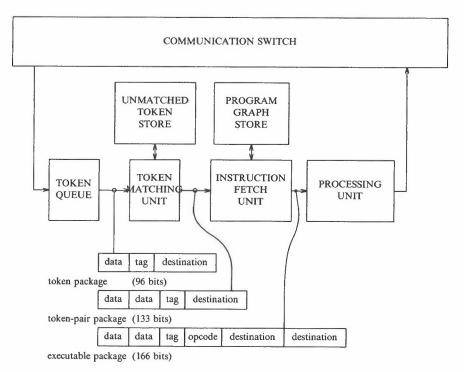

A research group at Manchester University under the leadership of John Gurd and Ian Watson has constructed a specialized 'ring-structured' dataflow processor with funding from the Distributed Computing Systems Programme of the Science and Engineering Research Council of Great Britain [10,11]. In this ring-structure the three dataflow tasks (i.e. matching tokens together; finding the next instruction; and processing of instructions) are implemented in three separate hardware modules. The individual actions in these modules are dependent solely on the module input data so that successive actions may be overlapped by connecting the modules in a pipeline. One extra pipeline module is provided to queue excess tasks when highly parallel programs are running. The overall ring-structure is therefore a four-stage pipeline as shown in Figure 2-5.

The fundamental unit of data in the switch is a token-package representing a tagged token on an arc of the program graph. The token has a data type and value, and a tag. The arc is represented by the address (in the program graph store) of the instruction at its head (known as the 'destination'). The token is the smallest data package in the system, and so the queue module is positioned adjacent to the switch, at the input to the ring.

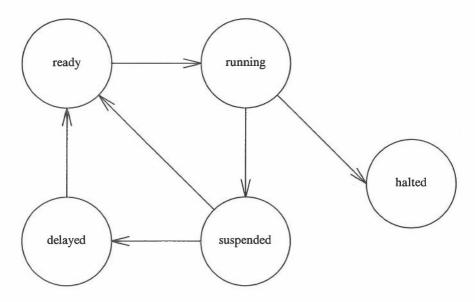

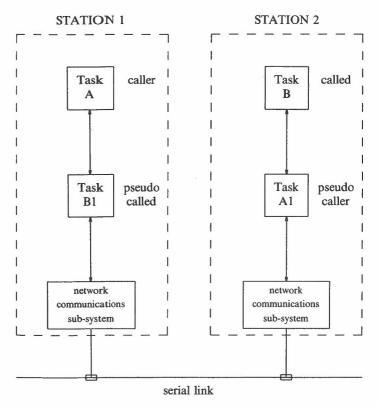

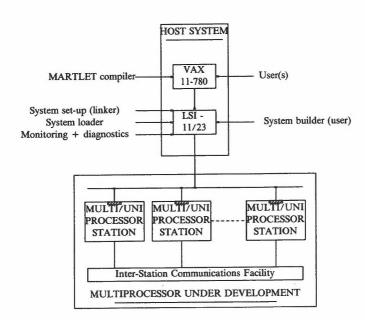

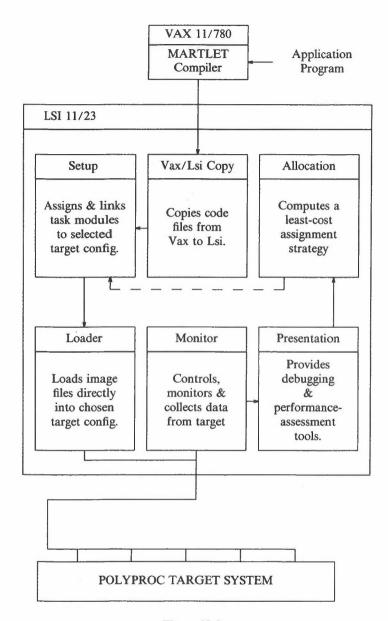

Queued tokens are presented one-at-a-time to the matching unit, which is responsible for grouping together tokens with the same tag heading for the same destination instruction. In the Manchester system tokens may be grouped together in ones or twos, so that triadic instructions and above cannot be supported. Tokens which expect to find a partner, but which arrive at the matching unit before the partner does, are kept in the unmatched-token store until the partner arrives. At this time (or, in the case of a single-input instruction, when the first and only token arrives) all the required input data and the common tag and destination fields are sent to the instruction fetch unit as a token-pair package.